概述

Serial RapidIO(SRIO) 特指 RapidIO 标准的串行物理层实现。

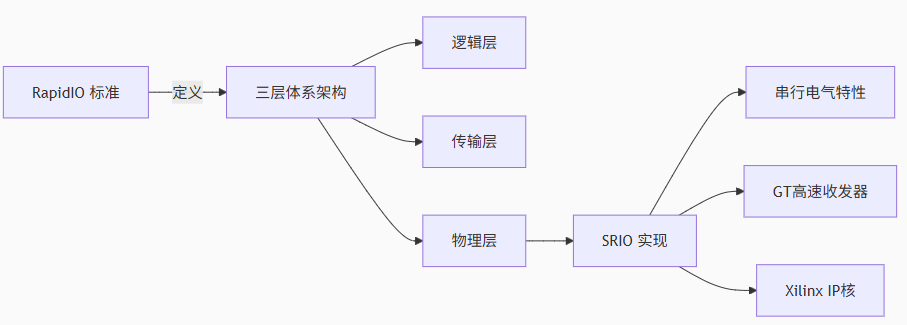

RapidIO 标准定义为三层:

-

逻辑层:定义总体协议和包格式,包含设备发起和完成事务的必要信息。

-

传输层:提供包传输的路由信息,对顶层不可见。

-

物理层:描述设备级接口细节(包传输机制、流控、电气特性、低级错误管理)。

逻辑层(LOG)

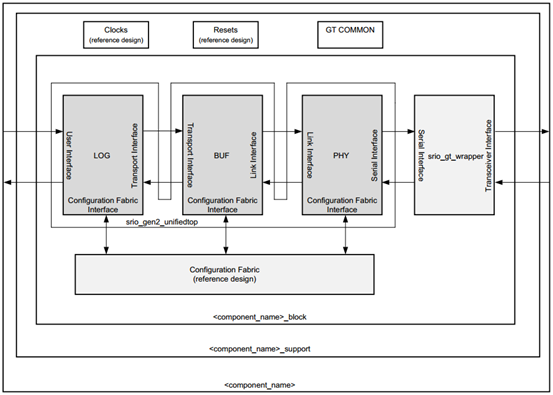

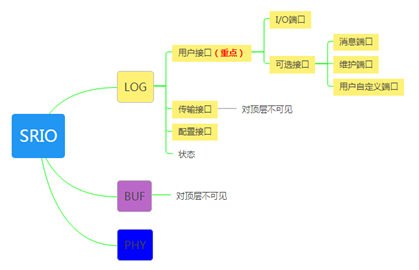

逻辑层划分为以下模块控制并解析数据包,提供三类接口:

-

用户接口(User Interface)

-

传输接口(Transport Interface)(相当于缓存 Buffer,对顶层不可见)

-

配置接口(Configuration Fabric Interface)(用于读写本地配置空间及逻辑/传输层寄存器)

用户接口(重点关注)

包含 I/O 端口集 和三个可选端口:

-

I/O 端口集:

-

支持事务:NWRITEs、NWRITE_Rs、SWRITEs、NREADs、RESPONSEs(不含维护事务响应)、门铃事务。

-

消息事务(取决于配置是否分离 I/O 与 Message 端口)。

-

-

消息端口:专用于消息事务。

-

维护端口:专用于维护事务。

-

用户自定义端口:支持自定义类型(未使能时丢弃包)。

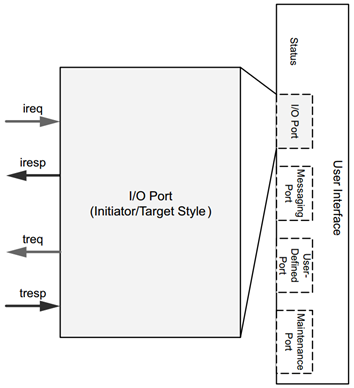

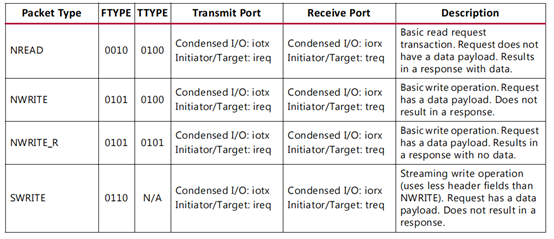

I/O 端口类型

| 类型 | 描述 |

|---|---|

| Condensed I/O | 单一 AXI4-Stream 通道发送/接收所有包 |

| Initiator/Target | 分离请求与响应,共 4 个 AXI4-Stream 通道: - ireq (本地请求) - iresp (远程响应) - treq (远程请求) - tresp (本地响应) |

顶层信号映射:

-

s_axis_ireq*→ireq -

m_axis_iresp*→iresp -

m_axis_treq*→treq -

s_axis_tresp*→tresp

物理层(PHY)

功能:

-

处理链路训练(Link Training)、初始化、协议

-

插入 CRC 与应答标识符

-

连接高速串行收发器(外部例化模块)

接口:

-

2 个 AXI4-Stream 通道连接传输层

-

1 个 AXI4-Lite 接口连接配置层

-

1 个串行接口连接收发器(FPGA 使用 GT 接口实现)

寄存器空间

| 类型 | 描述 |

|---|---|

| 能力寄存器(CAR) | 在逻辑层实现 |

| 状态寄存器(CSR) | 在逻辑层实现 |

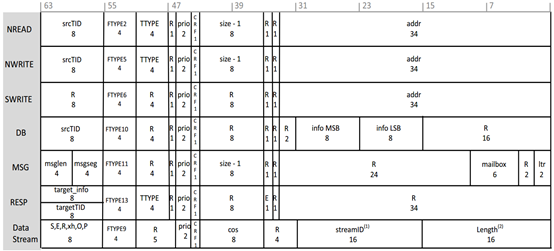

HELLO 包格式

标准化包头域,包头与数据分离传输:

-

Size 域:值 = 传输字节总数 - 1(有效范围 0~255 → 实际传输 1~256 字节)

-

限制:必须与 RapidIO 包中的 size/address/wdptr 域匹配,IP 核不会修正非法值。

注意 :AXI4-Stream 的

tdata为 8 字节(双字),需根据数据量是否小于 8 字节分别处理。

SRIO 事务类型及关系

1. 直接 I/O(DMA)事务

| 事务 | 特性 |

|---|---|

| NWRITE | 写操作,无需响应(效率最高) |

| NWRITE_R | 写操作,需响应(确保数据完整性,带宽利用率低) |

| SWRITE | 流式写操作,数据长度需为 8 字节整数倍(无响应,适用连续数据流) |

| NREAD | 读操作,从设备返回响应包携带数据 |

2. 消息传递事务

| 事务 | 特性 |

|---|---|

| DOORBELL | 短消息通知(邮箱号+少量数据,如中断触发) |

| MESSAGE | 长消息传输,数据路由到指定缓冲区(需软件解析) |

3. 维护事务

| 事务 | 用途 |

|---|---|

| MAINTENANCE READ/WRITE | 读写配置寄存器(初始化/错误处理) |

事务对比

| 维度 | 直接 I/O 事务 | 消息传递事务 |

|---|---|---|

| 效率 | 高(NWRITE/SWRITE 无响应) | 低(需软件介入) |

| 可靠性 | NWRITE_R/NREAD 通过响应保证 | 依赖软件处理 |

| 适用场景 | 硬件实时数据传输(DSP-FPGA) | 动态拓扑/软件交互(多处理器) |

事务类型表

详见 PG007 手册 P73。

总结

Xilinx SRIO IP核的事务类型覆盖了从高效硬件控制到灵活软件交互的全场景需求,用户需根据延迟、带宽、可靠性等指标选择合适类型。例如,实时数据采集可采用SWRITE,而系统配置则依赖MAINTENANCE事务。

-

直接 I/O:用于低延迟硬件控制(如实时数据采集用 SWRITE)。

-

消息传递:用于灵活软件交互(如系统通知)。

-

维护事务:用于设备配置管理。

本期分享结束,感谢大家看完,私信我可获取相关源码工程