基于 FPGA 的情绪感知系统设计方案:心理健康监测应用(一)

系列文章目录

FPGA+护理:跨学科发展的探索(一)

FPGA+护理:跨学科发展的探索(二)

FPGA+护理:跨学科发展的探索(三)

FPGA+护理:跨学科发展的探索(四)

FPGA+护理:跨学科发展的探索(五)

FPGA 在情绪识别领域的护理应用(一)

FPGA 在情绪识别领域的护理应用(二)

FPGA 在情绪识别领域的护理应用(三)

FPGA 在情绪识别领域的护理应用(四)

文章目录

- [基于 FPGA 的情绪感知系统设计方案:心理健康监测应用(一)](#基于 FPGA 的情绪感知系统设计方案:心理健康监测应用(一))

- 系列文章目录

-

- 一、项目概述

-

- [1.1 目标与背景](#1.1 目标与背景)

- [1.2 系统功能与架构](#1.2 系统功能与架构)

- [1.3 技术路线与创新点](#1.3 技术路线与创新点)

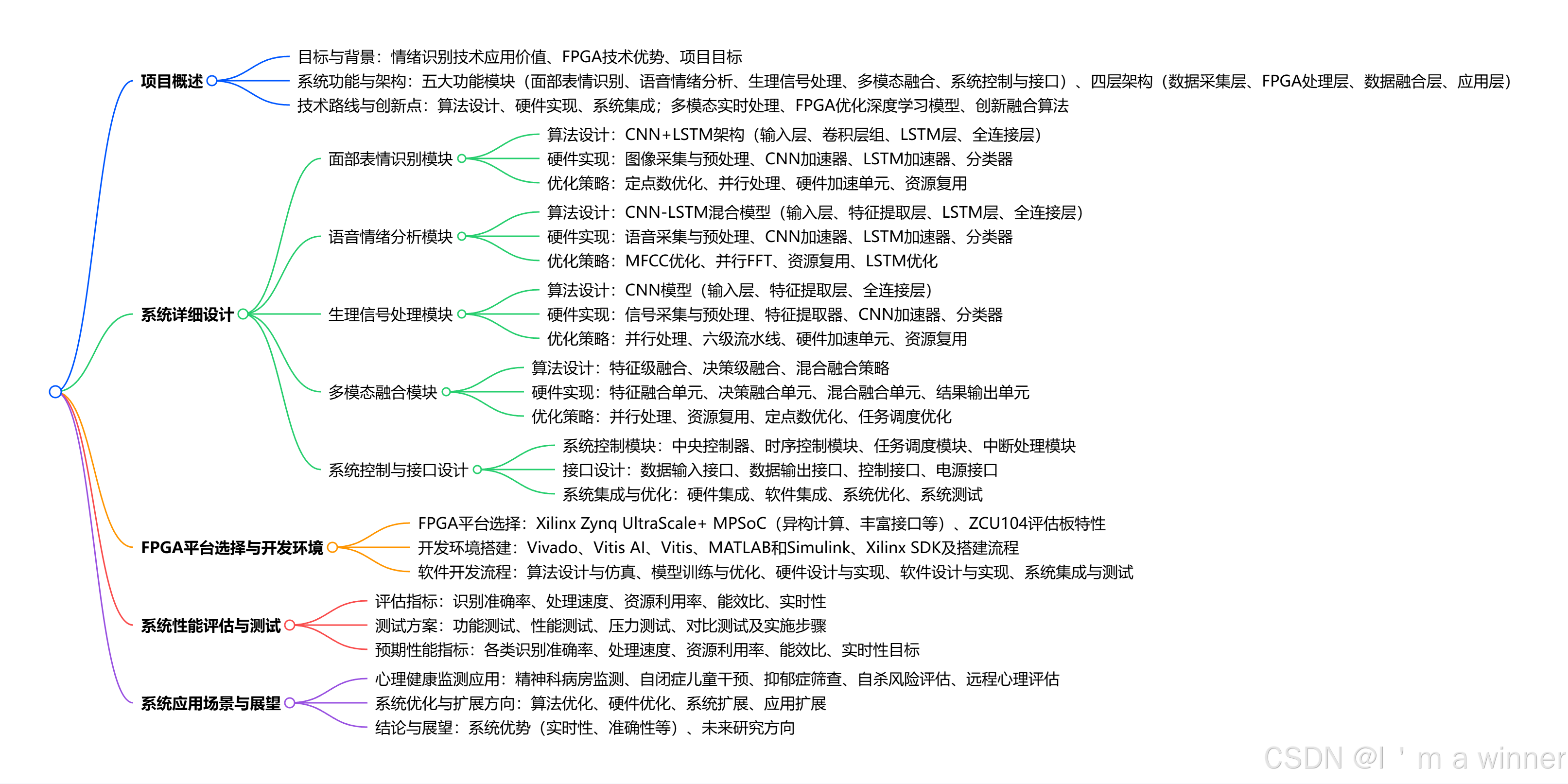

一、项目概述

1.1 目标与背景

情绪识别技术是情感计算领域的重要组成部分,它通过分析人类的生理信号、面部表情、语音特征等多种模态信息,实现对人类情绪状态的自动识别和分类(6)。在临床精神医学护理场景中,情绪识别技术具有重要的应用价值,能够帮助医护人员实时监测患者的情绪状态,辅助诊断和治疗方案的制定,提高护理质量和效率(6)。

随着现场可编程门阵列 (FPGA) 技术的快速发展,其在实时信号处理、并行计算和低功耗等方面的优势,使其成为情绪识别系统硬件实现的理想选择(6)。FPGA 凭借其可重构性、并行处理能力和低延迟特性,能够高效地处理情绪识别算法中的复杂计算任务,为临床精神医学护理提供实时准确的情绪识别支持(6)。

本项目旨在设计并实现一个基于 Xilinx FPGA 的多模态情绪感知系统,主要应用于心理健康监测和精神医学护理领域。系统将集成面部表情识别、语音情绪分析和生理信号处理三大核心功能,并探索多模态数据融合技术,以提高情绪识别的准确性和可靠性。

1.2 系统功能与架构

本系统主要实现以下功能模块:

-

面部表情识别模块:实时捕捉面部表情图像,进行预处理、特征提取和分类识别,判断情绪状态

-

语音情绪分析模块:采集语音信号,进行特征提取和情绪分类,识别语音中的情感信息

-

生理信号处理模块:采集并处理 EEG、ECG、EDA 等生理信号,提取情绪相关特征

-

多模态融合模块:融合不同模态的情绪识别结果,提高整体识别准确率

-

系统控制与接口模块:协调各模块工作时序,实现与外部设备的通信接口

系统的总体架构如图 1 所示:

+----------------+

| 数据采集层 |

| (摄像头、麦克风、生理传感器) |

+----------------+

|

+----------------+

| FPGA处理层 |

| (预处理、特征提取、分类识别) |

+----------------+

|

+----------------+

| 数据融合层 |

| (多模态融合算法) |

+----------------+

|

+----------------+

| 应用层 |

| (预警、决策支持、用户界面) |

+----------------+图 1:系统总体架构图

1.3 技术路线与创新点

本项目拟采用的技术路线主要包括:

-

算法设计:针对 FPGA 硬件特性优化的面部表情识别、语音情绪分析和生理信号处理算法

-

硬件实现:基于 Xilinx FPGA 的并行处理架构设计,充分利用 FPGA 的可重构特性和并行计算能力

-

系统集成:多模态数据融合方法,结合不同模态的优势,提高情绪识别的准确性

我们希望该系统能够实现:

-

基于 FPGA 的多模态情绪识别系统,实现面部表情、语音和生理信号的实时处理

-

针对 FPGA 硬件特性优化的深度学习模型,提高处理速度和资源利用率

-

创新的多模态融合算法,有效结合不同模态的情绪识别结果