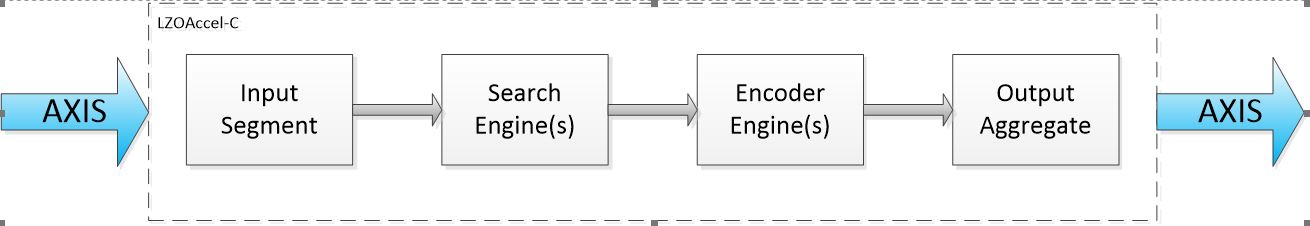

LZOAccel-C

LZO Data Compression Core/无损数据压缩IP Core

LZOAccel-C是一个无损数据压缩引擎的FPGA硬件实现,兼容LZO 2.10标准。

Core接收未压缩的输入数据块,产生压缩后的数据块。Core使用合适的头和尾封装了压缩后的数据载荷,所以用户不需要处理压缩后的数据块。输入的数据块可以被分段,并且不同数据块的分段可以交织输入Core。

Core的架构比较灵活,可以根据终端用户的需求很好地调整压缩率和吞吐率,可以在低成本的FPGA上实现超过16Gbps的吞吐率。

LZOAccel-C可以提供与当前流行的基于LZO 2.10软件应用相当的压缩率,并且可以通过软件模型分析处理速度和压缩率,方便地为特定的系统取得最好的速率和效率之间的权衡。

LZOAccel-C采用AMBA AXI4-Stream数据接口,非常易于被使用和集成。LZOAccel-C可以脱机、独立运行,释放CPU的数据压缩密集任务量。

内核特性:

- 使用LZO 2.10标准(oberhumer.com: LZO real-time data compression library)进行无损数据压缩

- 可配置的数据块分段和搜索窗口大小[8KB,16KB,32KB]

- 可配置的并行处理等级[搜索引擎的数量,1~32]

- 可配置的字典深度[8K,16KB],字典RAM类型[BRAM,URAM]

- LZO编码格式,压缩率和吞吐率可调整

- 压缩率和软件应用相当

- 无需处理器,脱机、独立运行

- 通过完全验证(Canterbury Corpus)的LZO IP

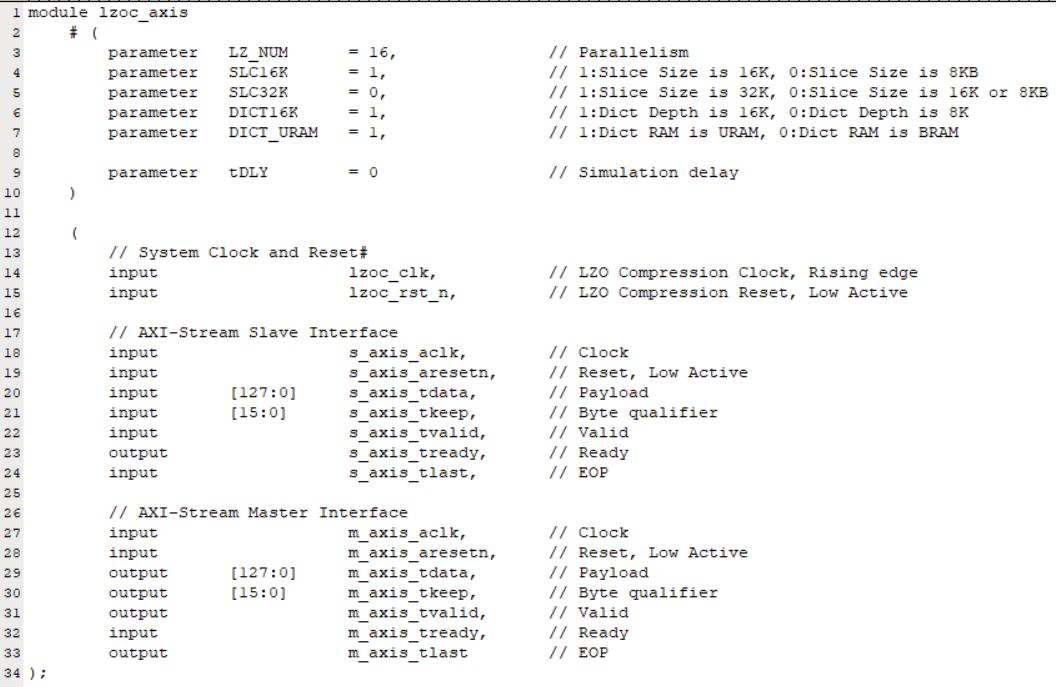

对外接口:

- 标准的AXI-Stream数据总线(128-bit数据宽度)

经典性能指标:

- 1Gbps压缩速率@1个搜索引擎@200MHz内核时钟

- 16Gbps压缩速率@16个搜索引擎@200MHz内核时钟

- 32Gbps压缩速率@32个搜索引擎@200MHz内核时钟

- 50%压缩率@ Canterbury Corpus

1个搜索引擎,16KB搜索窗口大小和字典深度配置的资源使用:

- XCKU060->LUTs:6877,FFs:2221,BRAM:26

- XCKU5P->LUTs:6877,FFs:2221,BRAM:10,URAM:2

16个搜索引擎,16KB搜索窗口大小和字典深度配置的资源使用:

- XCKU060->LUTs:110039,FFs:37790,BRAM:410

- XCKU5P->LUTs:110039,FFs:37790,BRAM:160,URAM:32

32个搜索引擎,16KB搜索窗口大小和字典深度配置的资源使用:

- XCKU060->LUTs:220028,FFs:73367,BRAM:820

- XCKU5P-> LUTs:220028,FFs:73367,BRAM:320,URAM:64

可交付资料:

- 详细的用户手册

- Design File:Post-synthesis EDIF netlist or RTL Source

- Testbench:Modelsim Testbench Source

- Timing and layout constraints,Test or Design Example Project

- 技术支持:邮件,电话,现场,培训服务

- Email:neteasy163z@163.com

LZO Compression IP Block Diagram