1.官方bug(显示问题不影响使用)

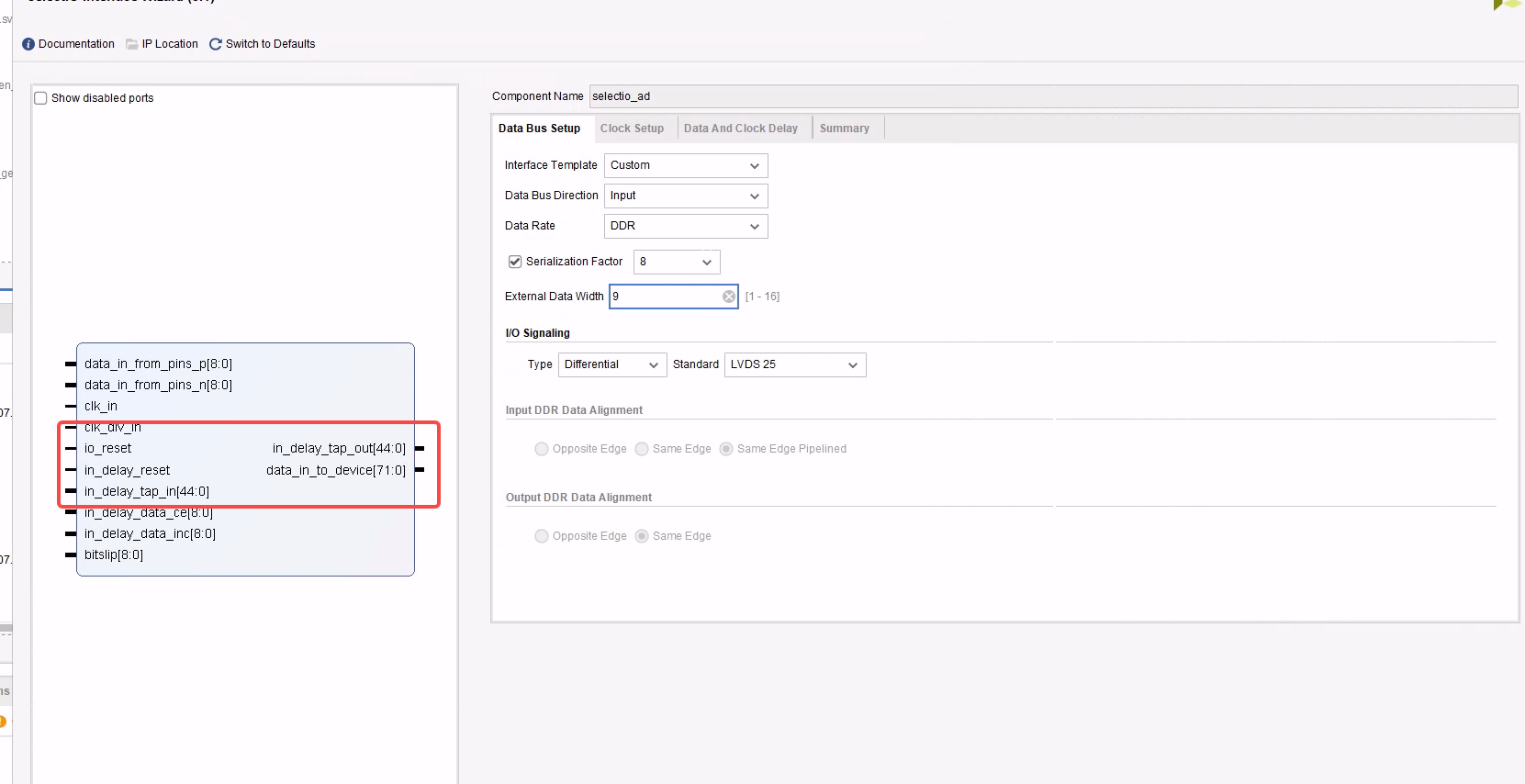

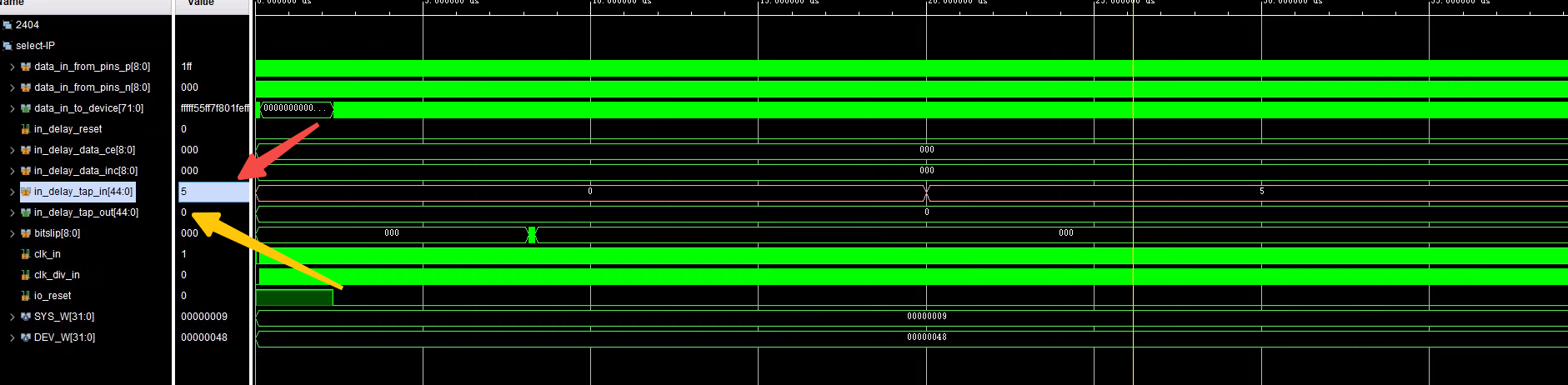

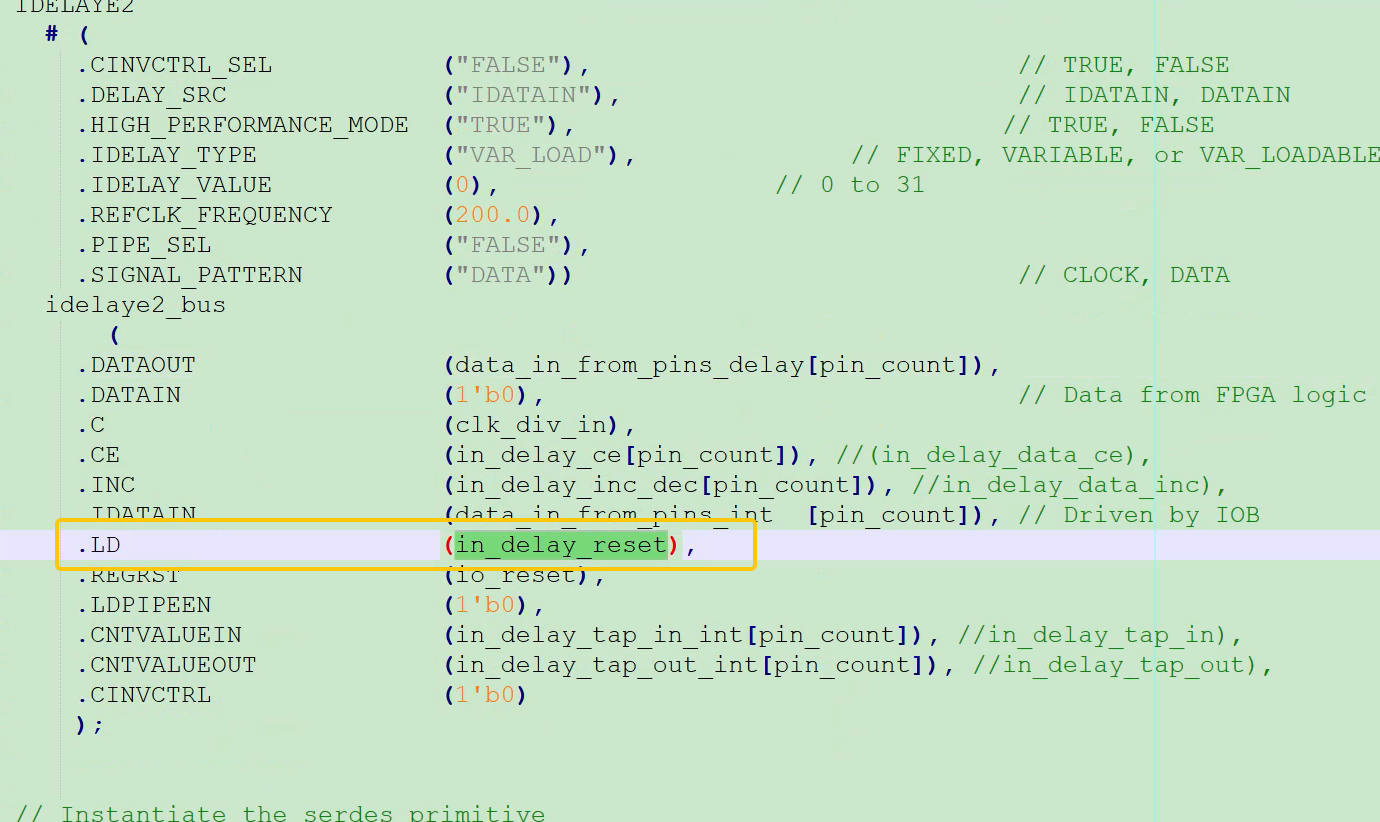

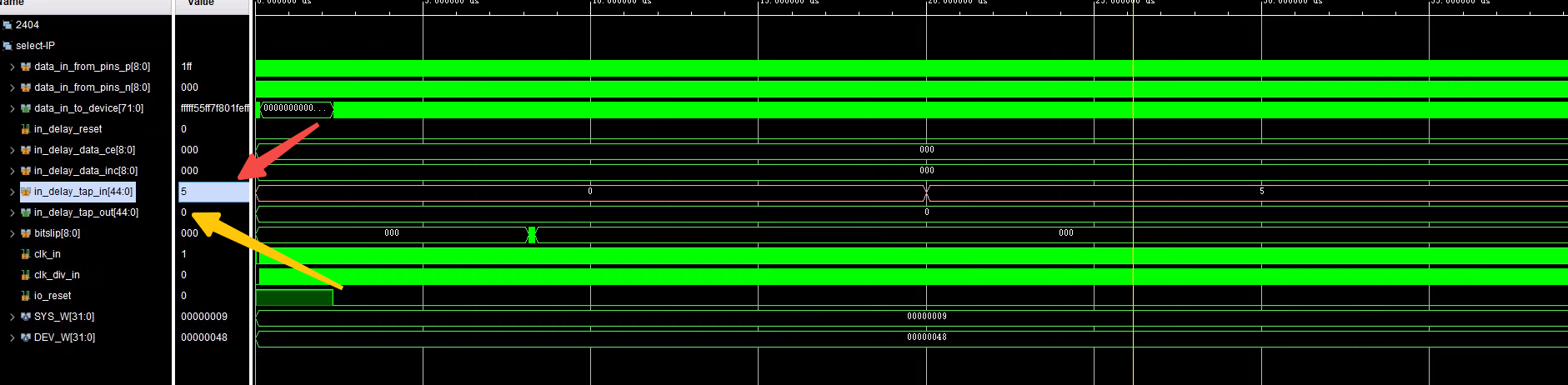

2.我们都知道IDELAYE2的IDELAY_TYPE("VAR_LOAD"), 为这个模式的时候,是可以自主写入idelay延迟进行IOdelay的。但这个IP启用了这个模式后,延迟输出CNTVALUEOUT却没有正确反馈。

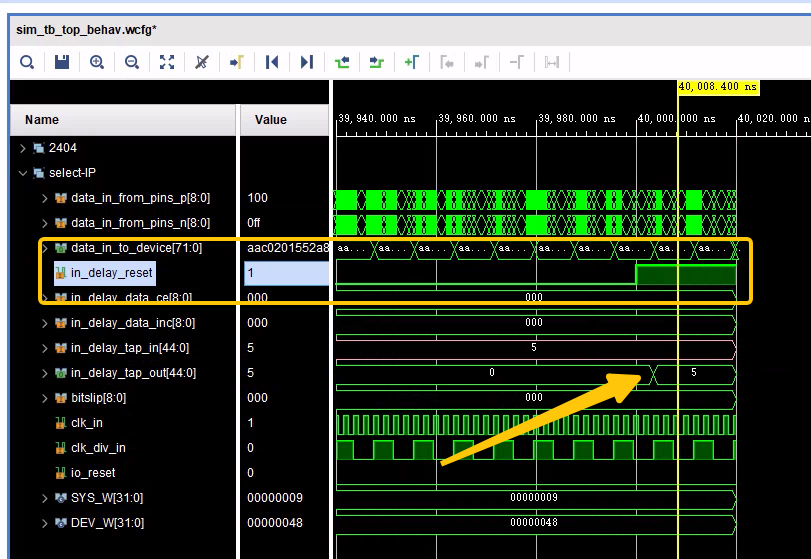

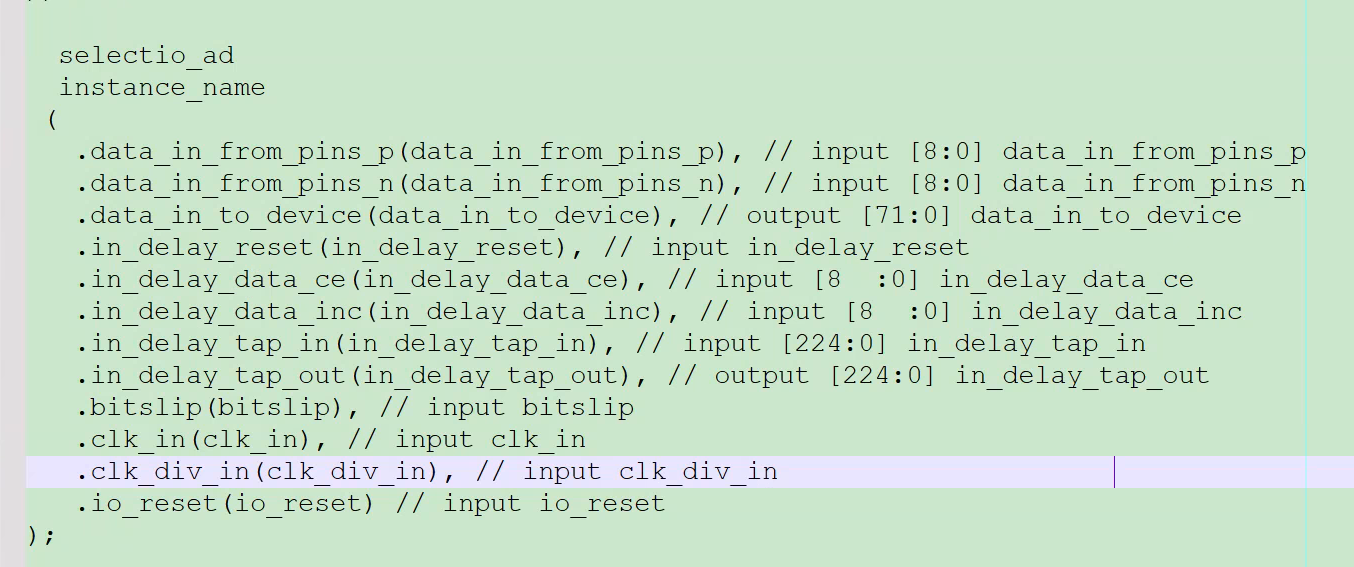

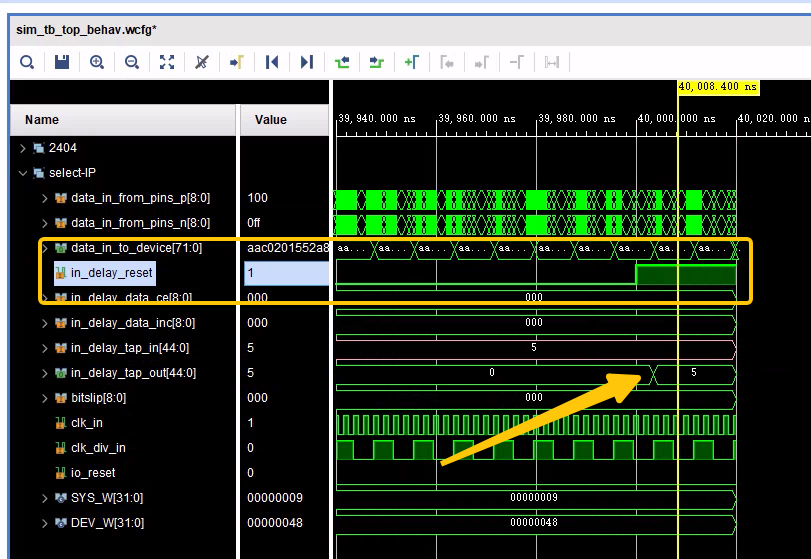

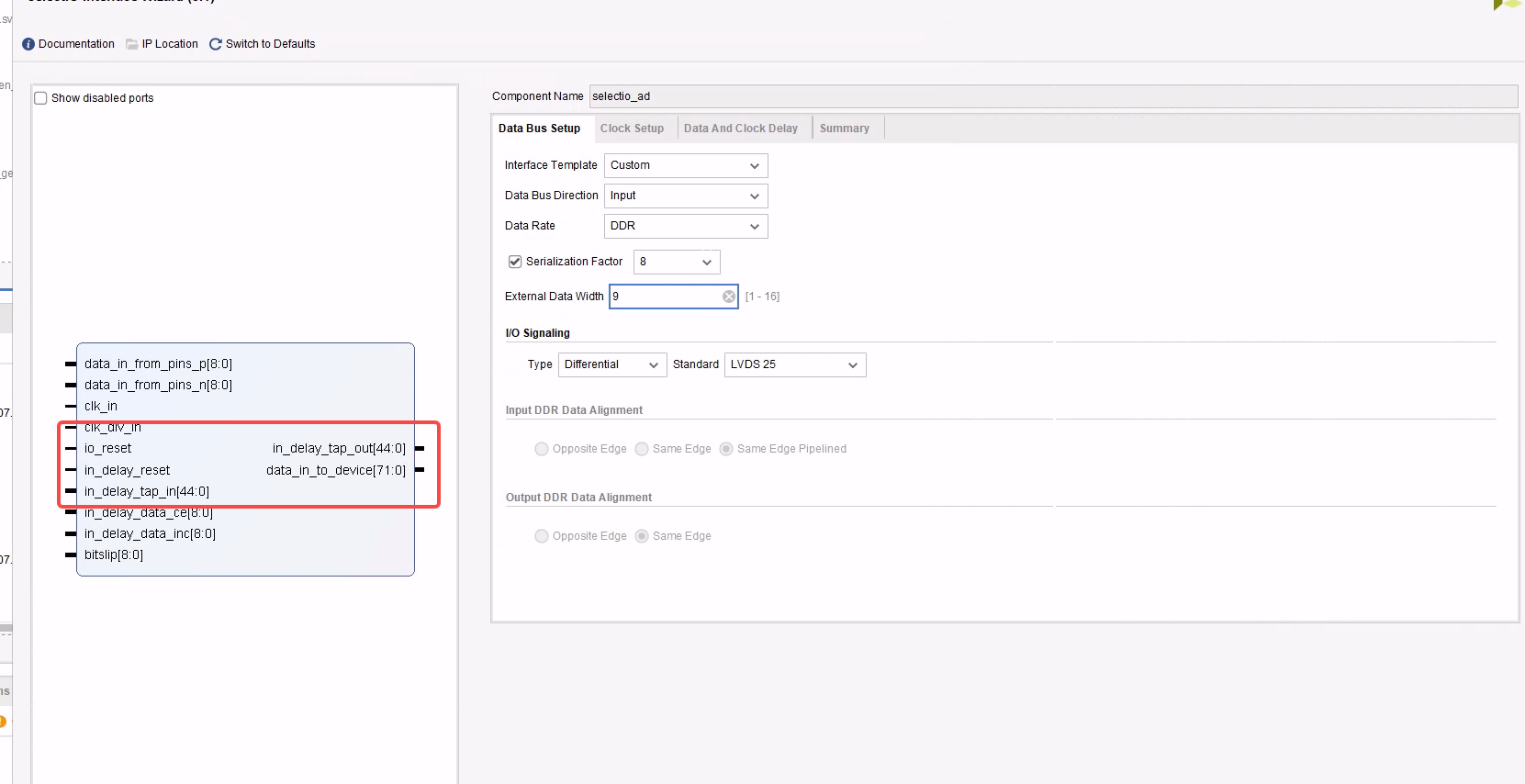

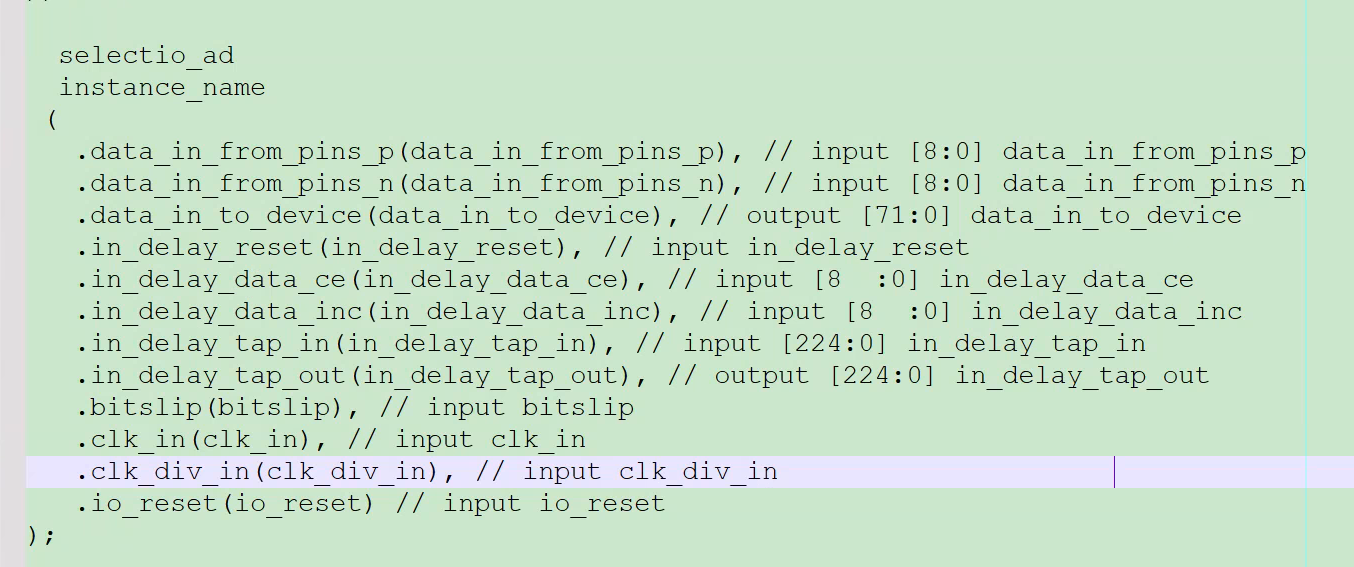

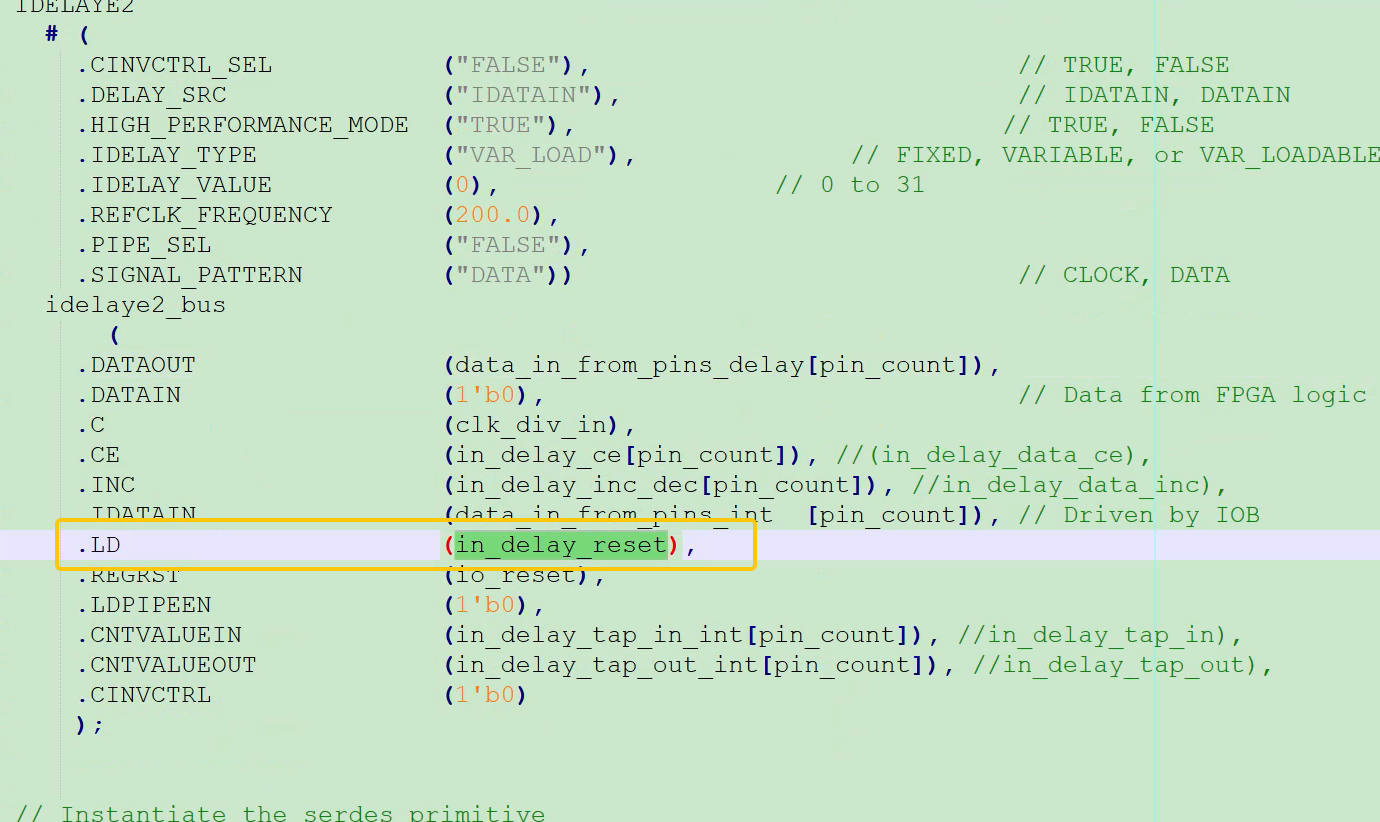

3.打开IP-顶层发现in_delay_reset信号作为了VAR_LOAD模式的LD信号。所以我们接下来试试着抬高一个周期的in_delay_reset信号。

4.输入延迟成功。

1.官方bug(显示问题不影响使用)

2.我们都知道IDELAYE2的IDELAY_TYPE("VAR_LOAD"), 为这个模式的时候,是可以自主写入idelay延迟进行IOdelay的。但这个IP启用了这个模式后,延迟输出CNTVALUEOUT却没有正确反馈。

3.打开IP-顶层发现in_delay_reset信号作为了VAR_LOAD模式的LD信号。所以我们接下来试试着抬高一个周期的in_delay_reset信号。

4.输入延迟成功。