高速接口基础

文章目录

前言

一、

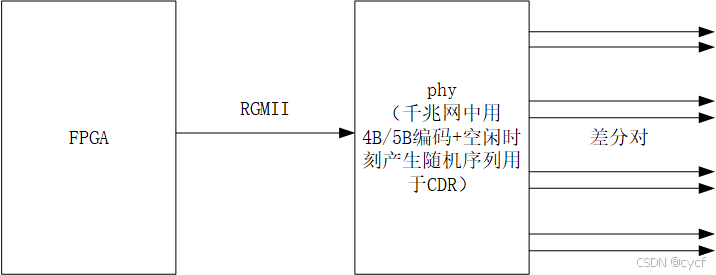

CDR:通过4B/5B编码进行时钟恢复。类似PLL去调整相位,调整的时钟的上升沿处于数据中点(最佳采样点)。

二、GT

serdes:串化。ser 串化 。des解串。

fpga内部硬核电路serdes:8bit转1bit,如果保持带宽不变,那么clk需要8倍。因此FPGA不支持这么高速率,因此使用专用硬件asic(硬核)

高速用串行:并行的线不容易保持严格等长(建立时间和保持时间需要都满足)

编码:8B/10B,均匀分布0和1。用于更好的恢复时钟(CDR)。连续的11111111111,不好恢复时钟和相位。

- K码:8bit拆 3+5=》4+6 。例:K28.5 。5为101。28为101000 ,则传输的数据为101_1 1100。

- D码:数据码 D16.2 。为010_100000

电平标准:CML。

发送通道和上层协议无关。软件协议和物理介质是无关的,光纤和铜轴都可以传

三、手册

手册:UG476