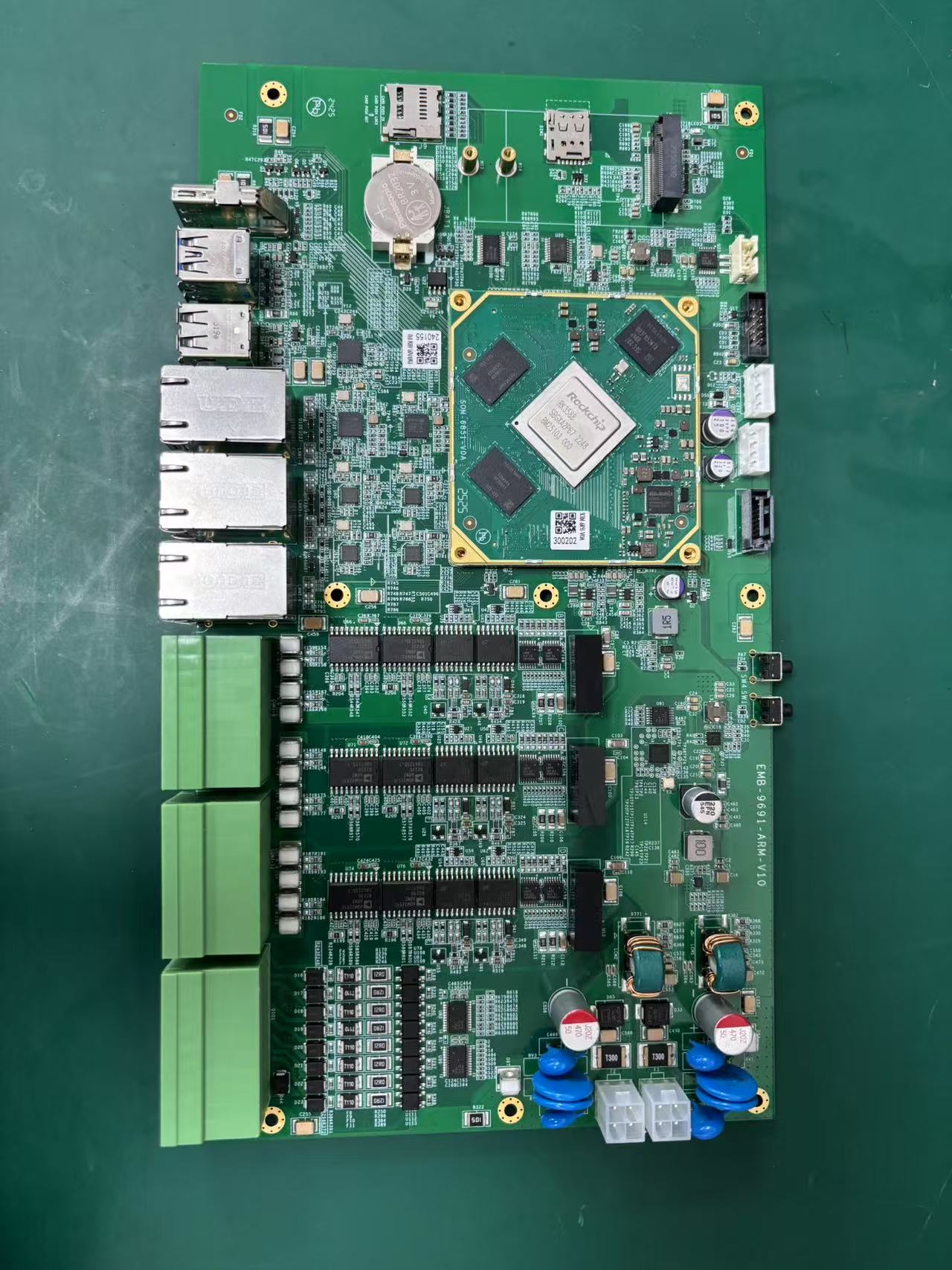

以下是基于RK3576+MCU+FPGA的工业自动化控制板解决方案的综合分析,结合异构计算架构与实时控制技术:

一、硬件架构设计

-

异构计算核心

- RK3576主控:四核Cortex-A72(2.3GHz)处理路径规划与AI视觉任务,四核Cortex-A53(2.2GHz)运行多传感器融合算法(如IMU/GPS数据同步),内置Cortex-M0硬实时核实现μs级PID控制(周期20μs)12。

- FPGA扩展:通过PCIe x4或FlexBus接口连接FPGA(如安路高云PGL25G),实现硬件加速任务(如LiDAR点云滤波、编码器信号解码),数据交换速率达280MB/s34。

-

工业接口配置

- 原生支持双CAN-FD(5Mbps)、16路PWM(100kHz)及8通道24-bit ADC(精度±0.05%),适配伺服驱动与高精度数据采集14。

- 扩展MIPI CSI-2接口支持4K@60fps视觉输入,双千兆网口实现EtherCAT/CANopen协议转换12。

-

安全与可靠性

- 硬件急停回路直连M0核GPIO(响应延迟<1ms),符合SIL2安全等级1。

- 宽温设计(-40℃~85℃)与抗50g冲击,通过MIL-STD-810G认证24。

二、软件协议栈实现

-

实时操作系统

-

采用Linux 6.1内核+RT-Preempt补丁或翼辉SylixOS(ASIL-D级),任务调度抖动<10μs12。

-

示例代码(FPGA-PID控制线程):

cCopy Code

RT_TASK motor_ctrl_task; void motor_control(void *arg) { while (1) { read_sensor_data(&imu_data); pid_calculate(&ctrl_output); pwm_set_duty(ESC_CH1, ctrl_output); rt_task_wait_period(); // 硬实时周期20μs } }

-

-

运动控制算法

- 支持8轴同步插补(轨迹误差<0.1mm),集成CODESYS V3.5 SP17运行时系统,兼容IEC 61131-3编程1。

- FPGA加速PID控制环(响应周期≤50μs),NPU(6TOPS算力)优化视觉SLAM(建图频率30Hz)24。

三、典型应用场景

-

工业机器人

- 多轴协同控制(如焊接、装配),通过FPGA实现μs级脉冲信号生成,支持EtherCAT总线扩展至32轴15。

-

AGV/AMR

- 融合LiDAR与视觉数据(最小检测距离0.5m),动态避障响应时间<50ms,符合ISO 3691-4:2020标准25。

-

无人机飞控

- 5G/WiFi 6E双冗余通信,MAVLink 2.0协议硬件加速,抗丢包率提升80%24。

四、性能对比与优势

| 指标 | 传统x86方案 | RK3576+FPGA方案 |

|---|---|---|

| 实时响应 | 500μs级 | <10μs级1 |

| 多协议兼容性 | 需协议转换卡 | 原生支持EtherCAT/CANopen1 |

| 轴控扩展能力 | 最大4轴 | 可扩展至32轴1 |

| 国产化率 | 依赖进口芯片 | 100%国产芯片2 |

该方案通过异构计算平衡性能与实时性,适用于高精度、高动态的工业自动化场景