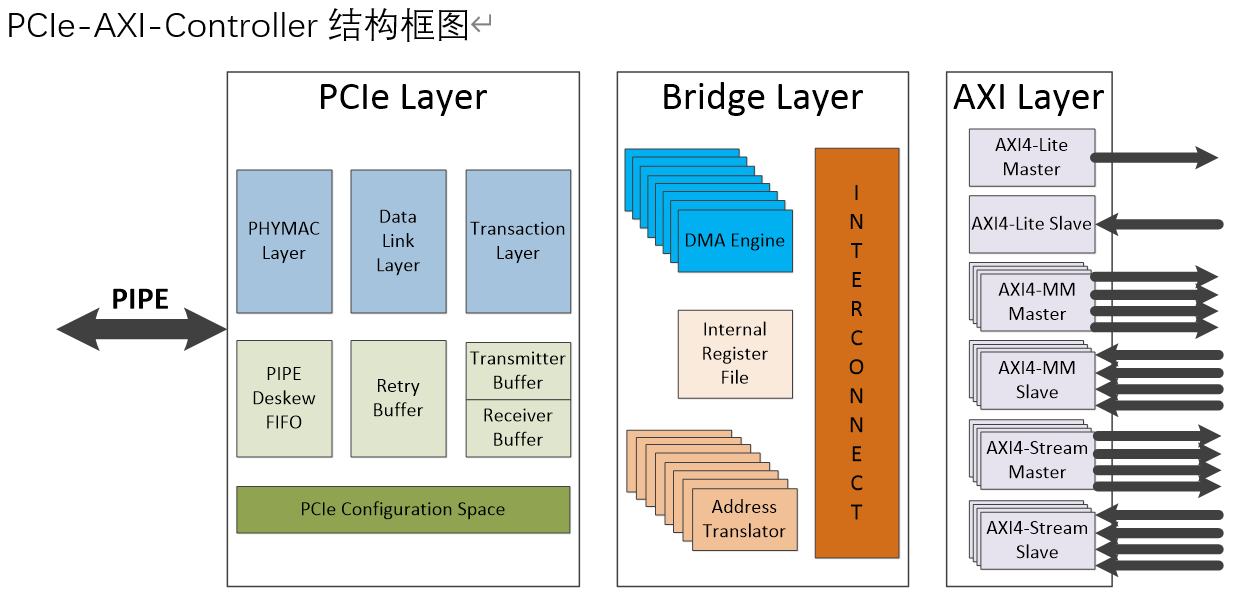

PCIe-AXI-Controller

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,实现PCIe PHY Layer,Data Link Layer以及Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

PCIe接口

- PHY Interface for PCI Express(PIPE):PIPE 4.4和PIPE 5.1

- 可与PIPE兼容的PHY集成

AXI接口:

- 1个AXI4-Lite Master接口:访问外部寄存器

- 1个AXI4-Lite Slave接口:访问内部Bridge配置寄存器

- 1个AXI4-MM Master描述符接口:访问AXI域的SGDMA描述符

- 4个AXI4-MM Master接口:访问AXI4 Slave设备,比如内存;C2H和H2C传输

- 4个AXI4-MM Slave接口:被AXI4 Master设备访问

- 4个AXI4-Stream Master接口:访问AXI4 Stream Slave设备,比如FIFO;H2C传输

- 4个AXI4-Stream Slave接口:被AXI4 Stream Master设备访问,C2H传输

PCIe特性:

- 支持PCIe Gen1(2.5GT/s),PCIe Gen2(5.0GT/s)和PCIe Gen3(8.0GT/s)

- 支持PCIe x16,x8,x4,x2和x1

- 支持Endpoint和Rootport模式

- 支持最大4KB payload size

- 1个Virtual Channel,最多32个Physical Functions

- 可配置的接收和发送缓冲区大小

- 支持SR-IOV功能,VF可达512个

- 支持32个MSI和INT消息

- 支持MSI-X

- 支持ASPM:L0s和L1

DMA特性:

- 8个独立的DMA引擎

- 支持CDMA和SGDMA

- 最大128个outstanding write和read request

- 可配置的DMA Source、Destination和Descriptor Type

- DMA长度无限制

可交付资料:

- 详细的用户手册

- Design File:Post-synthesis EDIF netlist or RTL Source

- Timing and layout constraints,Test or Design Example Project

- 技术支持:邮件,电话,现场,培训服务

- Email:neteasy163z@163.com

PCIe-AXI-Controller结构框图