UD FMC-704最高支持双通道3Gsps@14bit的采集。采集数据后,ADC芯片内部可以完成下边变频和抽取功能,FPGA内部再次进行抽取。

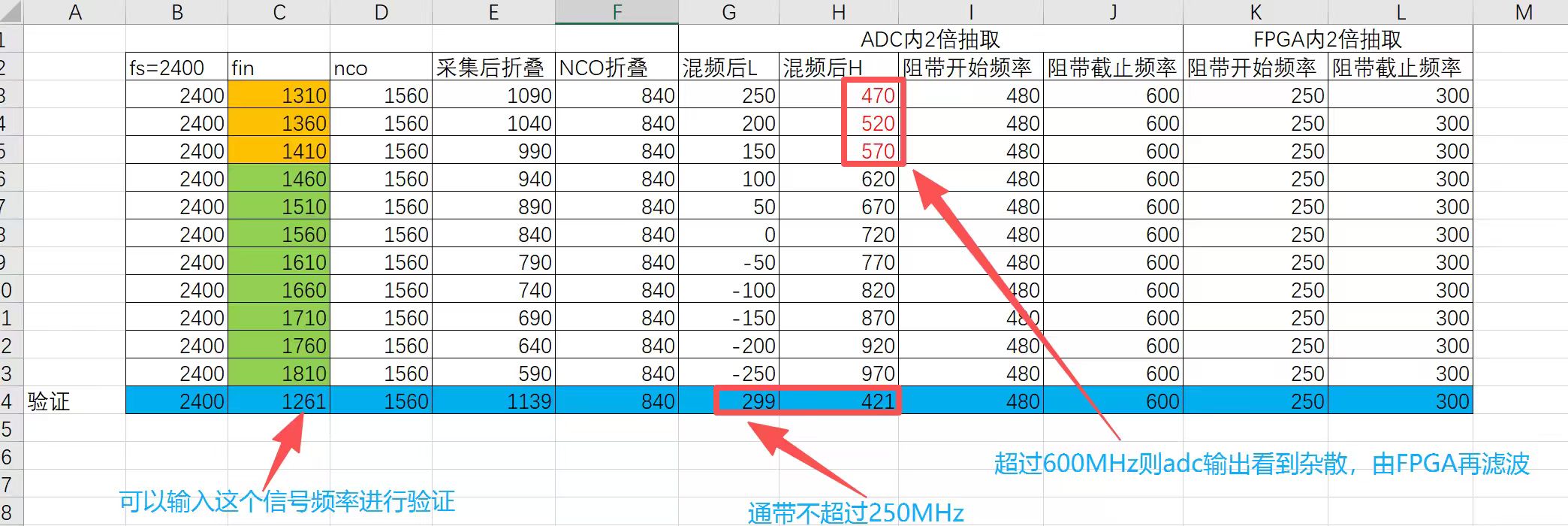

本项目采用采样率为2400MHz,输入信号的中心频率为1560MHz,需要采集500MHz带宽信号。由于1560MHz中心频率并不是理想的3/4点,NCO设置1560MHz中心频率后,对于±250MHz的带宽会产生混叠,计算列表如下:

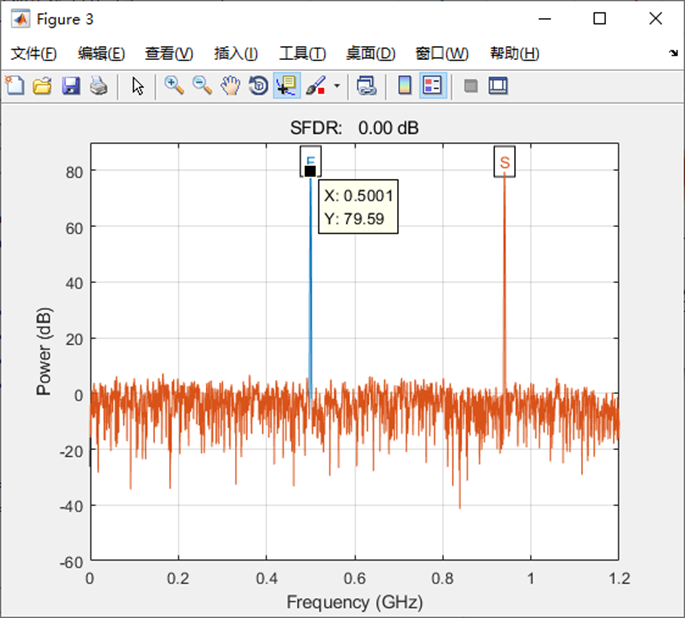

从上表计算来看,在输入1310MHz~1410MHz,ADC内部2倍抽取时,带内会看到2根频谱。在输入1310MHz时,实测情况如下:

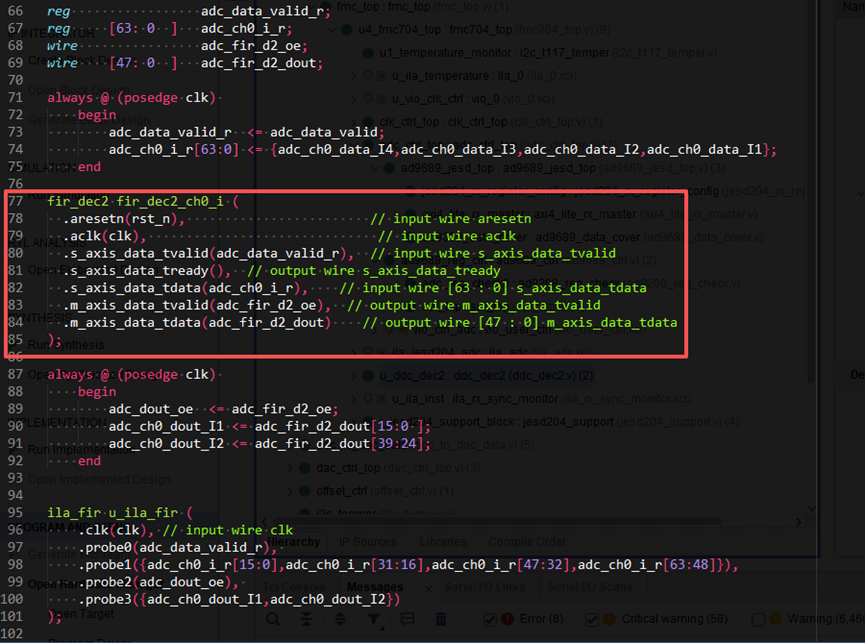

为了解决这个问题,在FPGA内部需要进行2倍抽取滤波。由于ADC输出DDC数据仍然是多相,则就需要进行多相抽取,可以调用xilinx的IP来实现。代码如下:

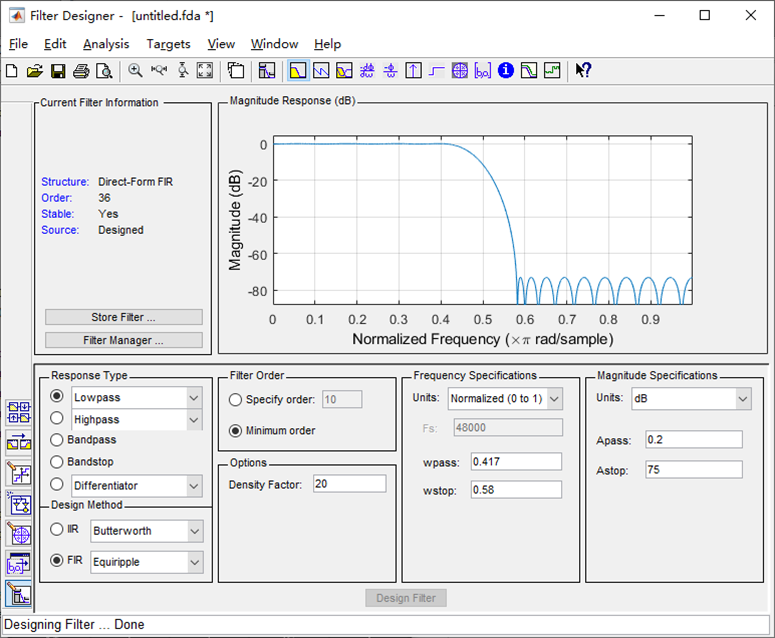

抽取滤波器先用matlab设置系数,假设矩形系数为1.2,则调用fdatool工具,系数设置为:

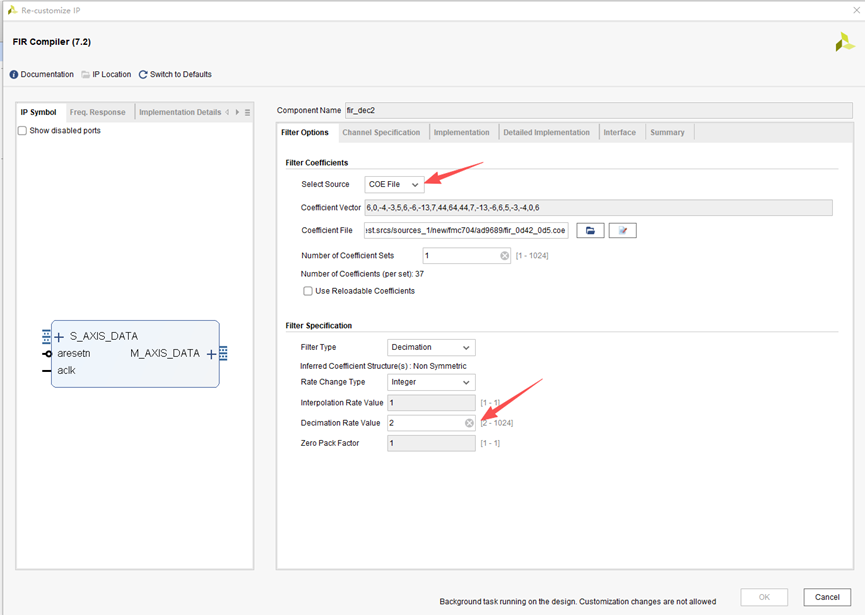

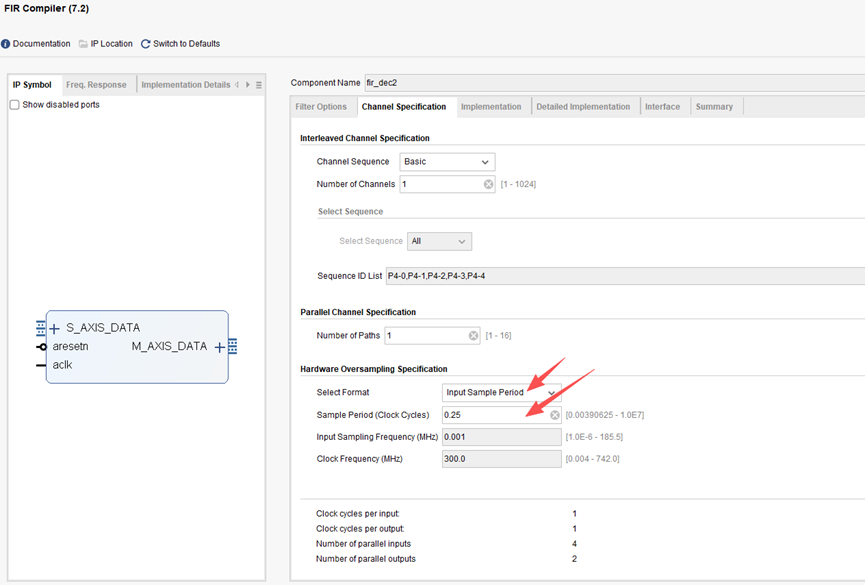

把生成的系数导出,在xilinx的FIR IP中可以进行调用。FIR IP的参数设置如下:

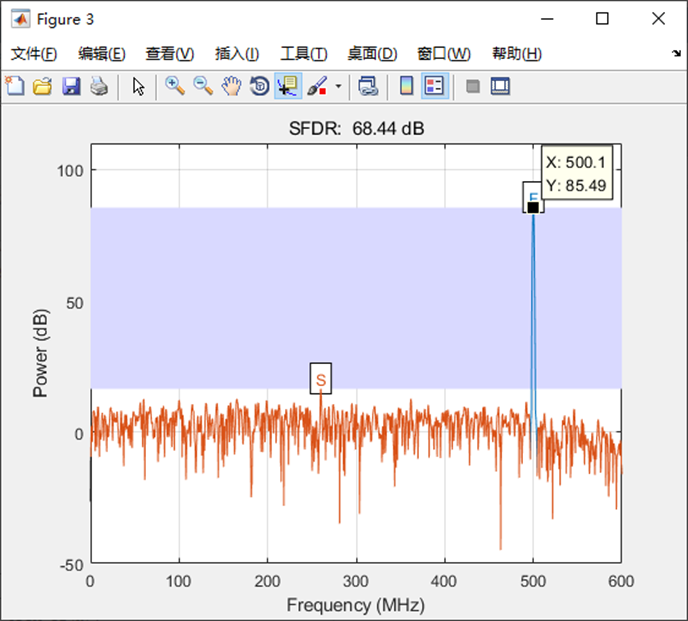

通过编译后,输入1310MHz时,滤波器输出测试情况如下:

验证平台:PCIE-402+FMC-704