继上一篇文章Giants Shoulder - Micron: LPDDR6 Power and Interface Features之后,本篇文章会继续从Interface和RAS为视角学习DDR的新系列:带你看巨人视角下的LPDDR

本期文档还是来自镁光的: LPDDR6 Power supply, Interface, and reliability features - Micron

Contents

先看目录,上一篇文章已经初步介绍了Power和Interface,本篇将从Interface的Link Protection继续:

Interface

Link Protection

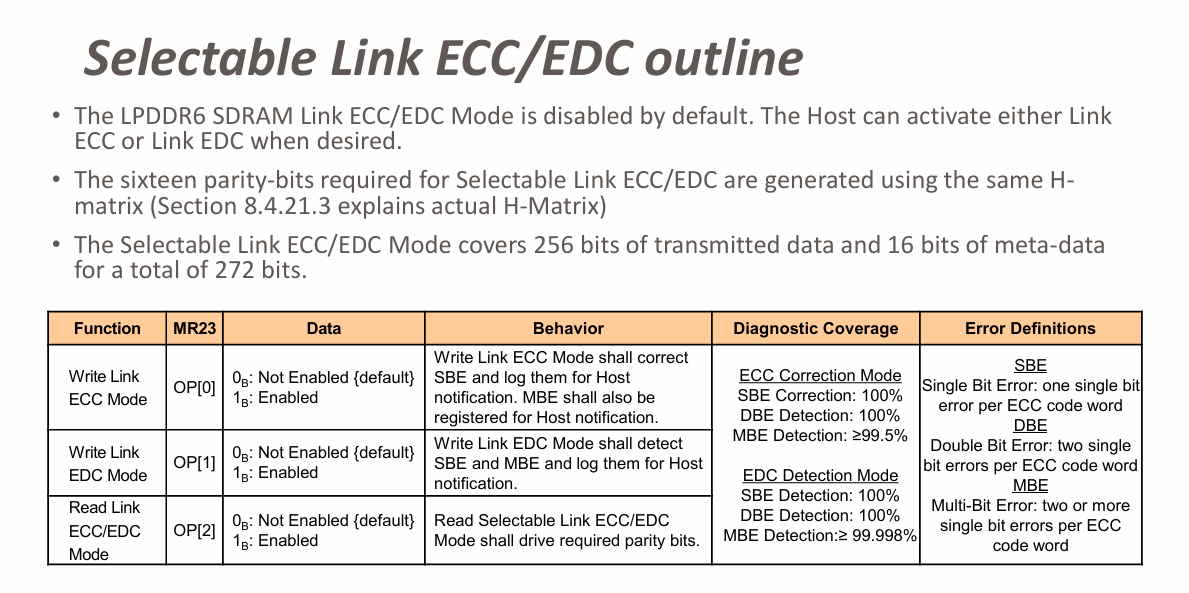

这一页是Link ECC/EDC的内容:

此功能在LPDDR6上默认关闭,ECC/EDC的16奇偶校验位由一个H矩阵生成,ECC/EDC模式覆盖256位传输数据和16位Meta数据,总计272位。 ·

下一页也是ECC/EDC内容,详细的也放在之后的文章分析吧。

Loopback Mode

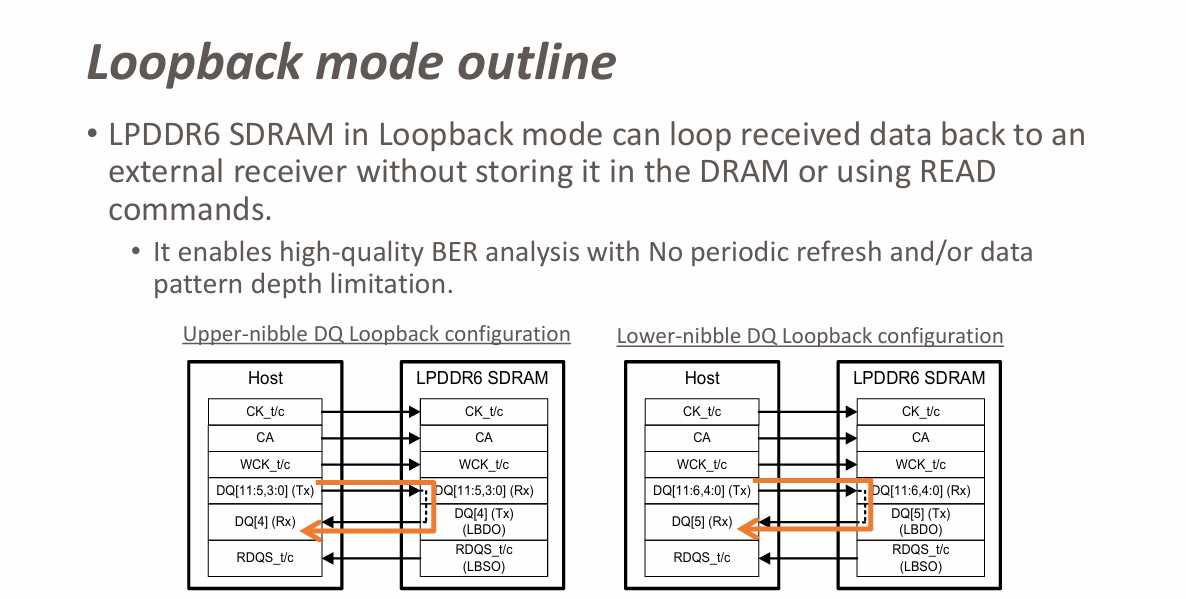

这一页也是LPDDR6独有的一个模式,LoopBack Mode:

提供的这个Loopback Mode能够不需要存储数据到DRAM或者READ命令来实现数据回读,Host的数据直接从DRAM的DQ Pins上走一遭就回到Host。

这样能够大大提高BER这类数据完整性的验证,避免了正常数据读写中的Refersh刷新或者数据深度的限制,直接验证链路可靠性。

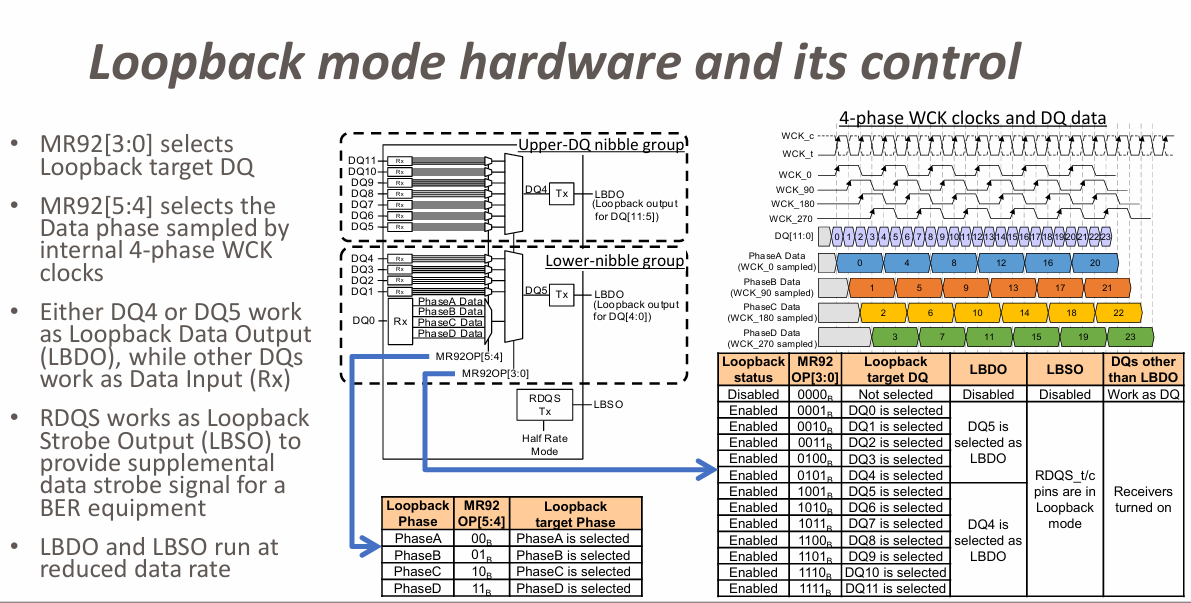

紧接着也简单介绍了Loopbak模式中MR寄存器相关的配置,由MR92控制数据输入DQ pin和不同的数据内容段落采样,至于DQ数据输出(LBDO)只有DQ4和DQ5供选择,RDQS则是继续作为采样时钟(LBSO)。

Loopback的更多SPEC详细内容也在后续文章介绍吧。

CA Bus Challenges

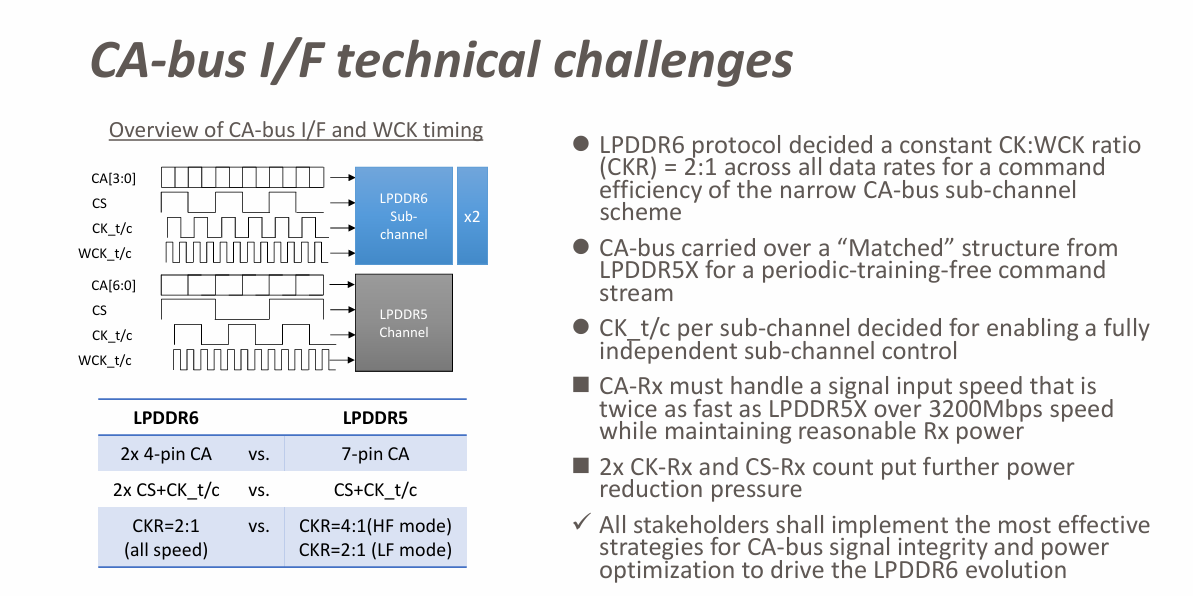

这一页的内容是围绕CA总线在LPDDR6上所面对的挑战:

相比LPDDR5,LPDDR6的CA从7-pin变化为2 x 4-pin,为2个Sub-Channel服务,并且修改为所有频率下统一2:1的CKR。

LPDDR6上的CA总线还是沿用了LPDDR5x上的架构,实现无需周期训练的命令流。

LPDDR6上的挑战包括了2倍速率的提升,2个Sub-Channel各自的CA总线都需要在保证稳定数据传输的前提下,尽可能降低功耗。

而速率的大幅提升势必会几何性增加数据稳定性和完整性的保持难度,如果增加更多的电路单元来保证数据完整性,又可能会给高频场景下的功耗过高和发热问题雪上加霜。

RAS

ALERT

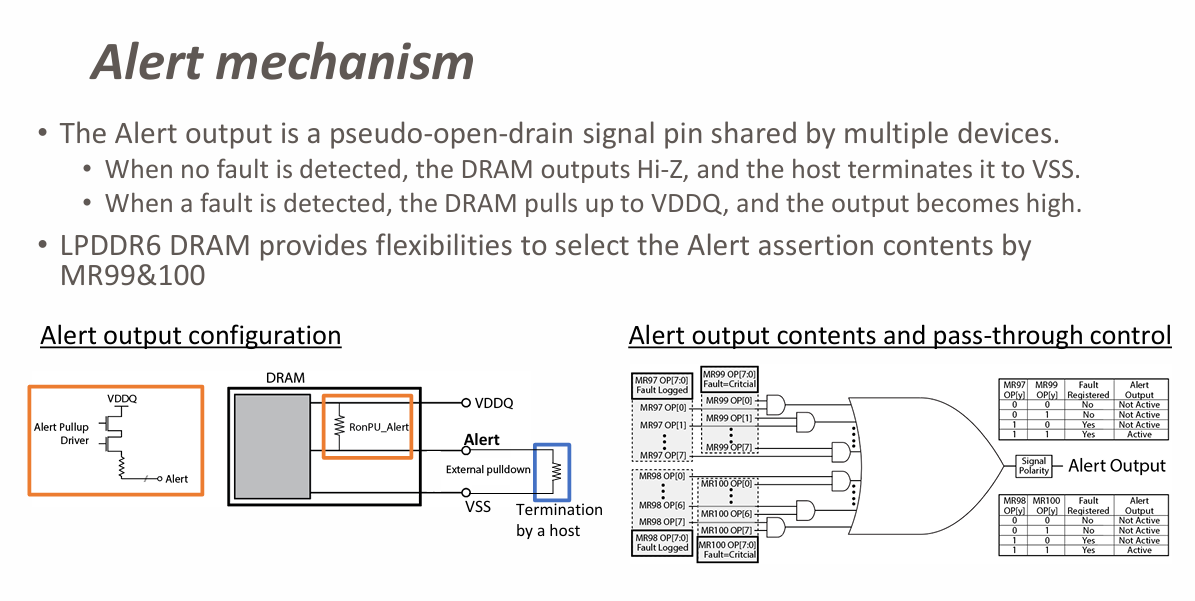

再往下就是可靠性的内容,先是LP6独有的ALERT机制:

首先ALERT机制在没有fault的时候,输出的Hi-Z会被Host端直接接地,检测到fault会拉高VDDQ,产生Alert信号。

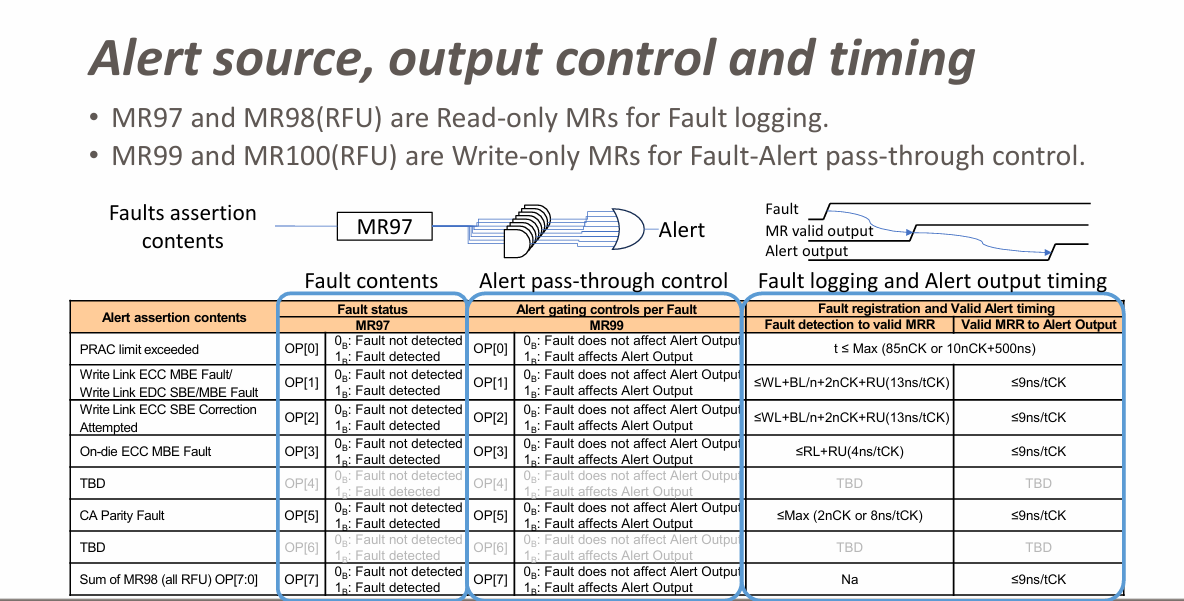

并且LPDDR6提供了MR97,MR98,MR99和MR100来配置实现多种灵活的报警方案。

其中MR97和MR98作为只读寄存器,提供错误日志信息。

MR99和MR100作为只写寄存器,用于控制这些不同类型的错误内容是否触发ALERT信号以及触发方式。

ECC

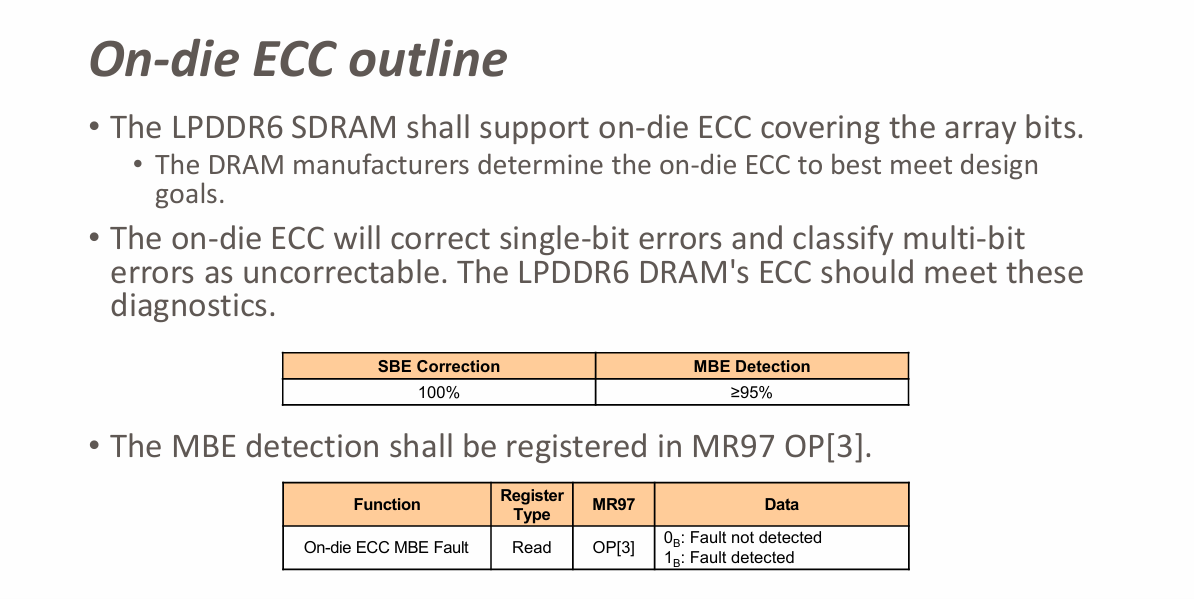

On-Die ECC的内容:

从DDR5的标准中移植过来的这项技术,能够自动修复Data Package中的Single Bit Error,也能够检测Multi Bit Error。

应该是因为带宽提升太大,数据的完整性必须保证,所以On-Die ECC也算是LPDDR6必须具备的一个功能了。

ECS

ECS的内容:

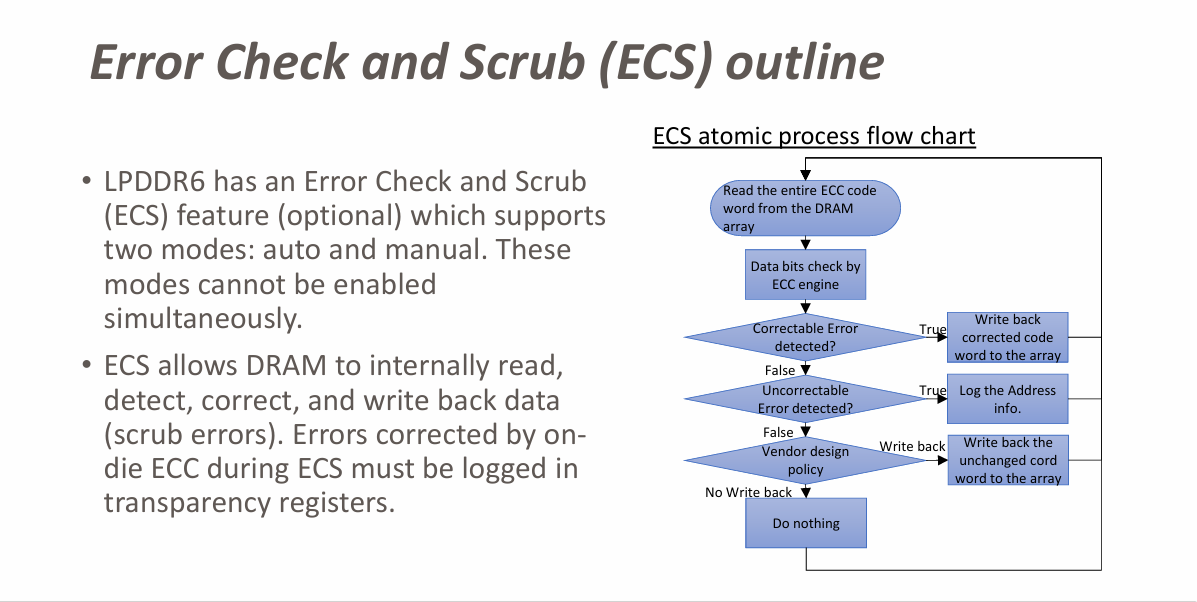

ECS的功能在LPDDR6上就是Optional了,提供了auto和manual两种模式,属于DRAM内部自检的一个功能。

通过On-Die ECC的code配合进行内部数据校验并修正,修正不了地址存起来。

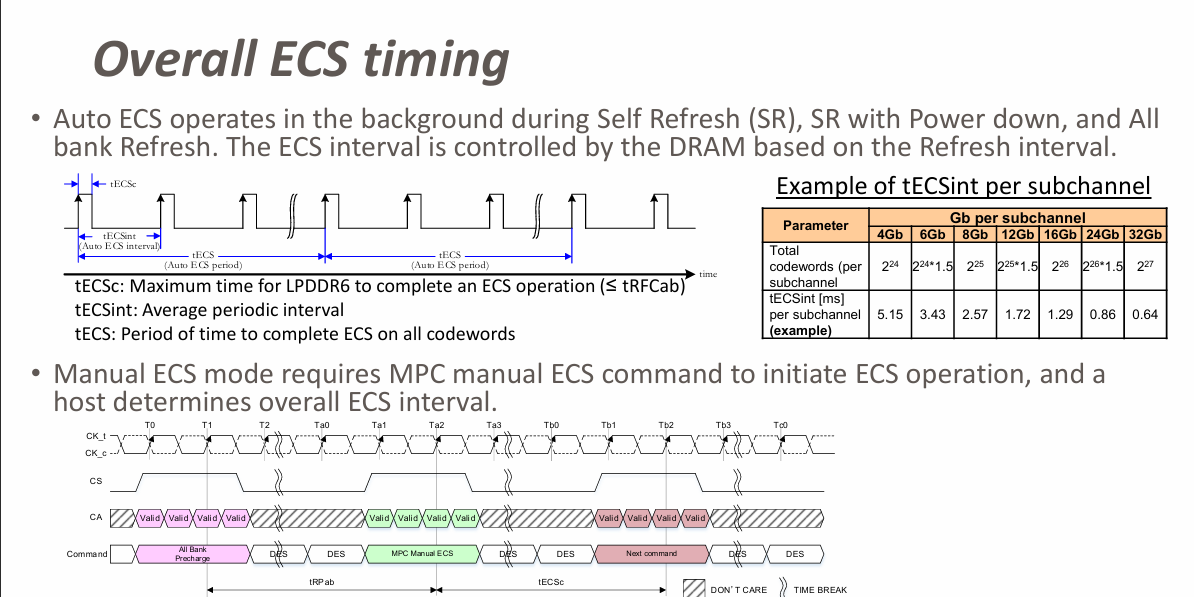

关于ECS的时序内容,这一页也提到了Auto ECS会在自刷新、全Bank刷新等阶段执行,由DRAM内部自行控制。

Manual ECS的行为则需要MPC Manual ECS命令来初始化才会执行。

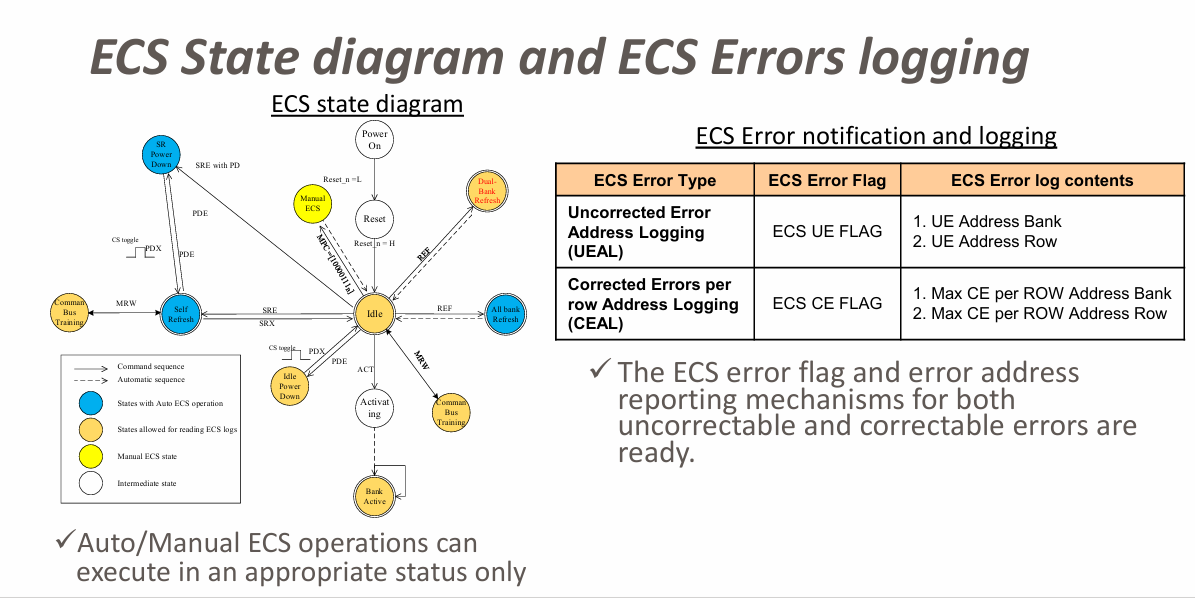

关于ECS的状态机,这一页也作了简单介绍,Manual ECS只能从IDLE状态进入,Auto ECS都是在刷新类行为才执行。

而ECS错误日志是能够同时记录可修正和不可修正的错误行和错误Bank信息。

MBIST

最后的MBIST的内容:

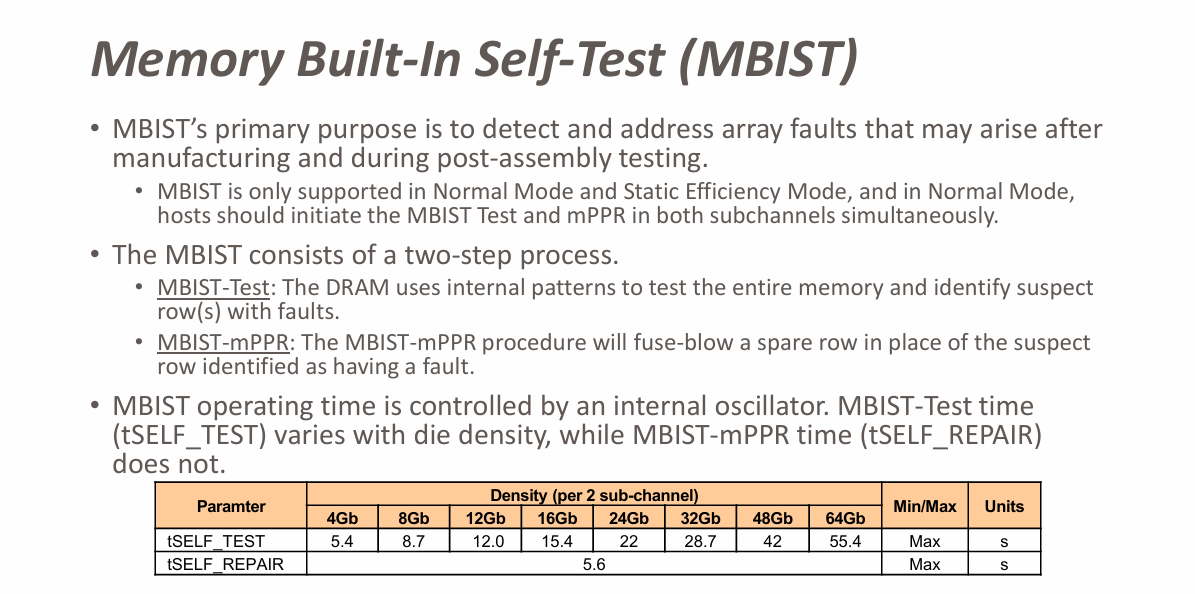

MBIST (Memory Built-In Self-Test) 在DDR5里已经通过了市场的验证,也是存储芯片验证中较为典型的检测方案。

通过生成一系列测试模式(如写 0、写 1、交替写等),将测试数据写入存储器,再读出并比较结果进行修复和记录。

主要用于验证片上存储器(如 SRAM、DRAM、嵌入式存储器)是否存在制造缺陷或运行故障,有兴趣的可以自行检索下。

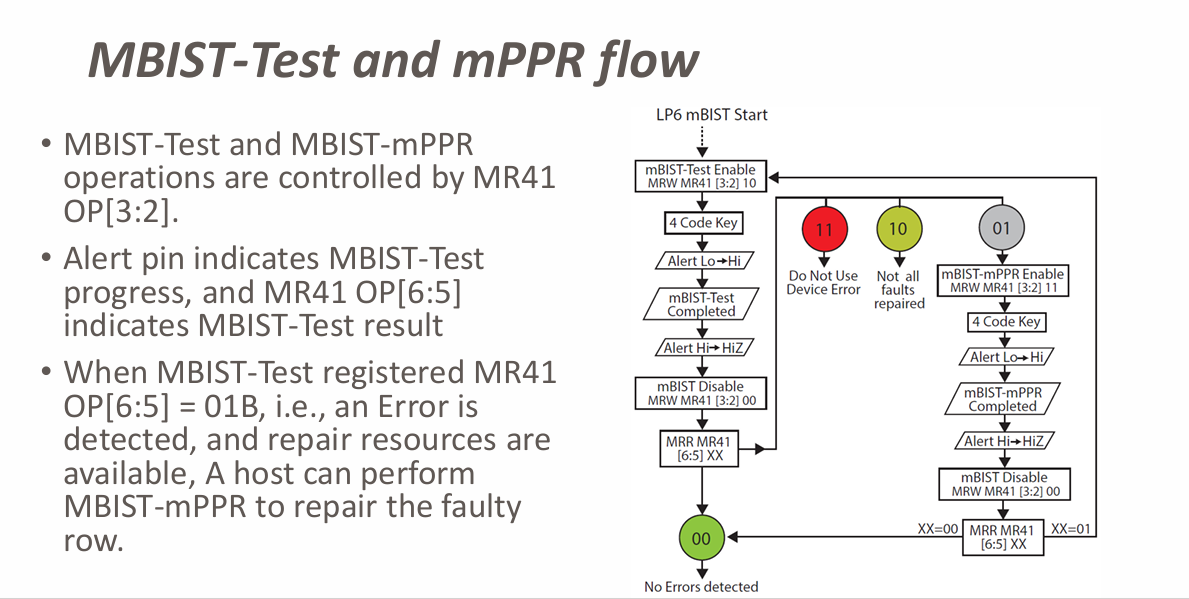

这里LPDDR6只支持Normal和Static两个模式,MBIST的自测分为DRAM内部Pattern读写校验和fuse熔断可疑行两部分,由MR41控制,并且结果也会保存于MR41寄存器。

LPDDR6中还提供了MBIST-mPPR功能,PPR功能在之前的文章LPDDR4 TTR/PPR/ECC/PASR/DBI提过,用于修复DRAM中的坏块。

这里也是类似,如果MBIST测出问题,并且也有可供替换的空间,就可以直接修复错误的行。