DDR 内存架构与 Linux 平台工作机制深度解析

文章目录

- DDR 内存架构与 Linux 平台工作机制深度解析

-

-

- DDR 技术原理与物理架构

-

- 1.1 物理结构:从 Channel 到 Cell

- 1.2 关键时序参数 (Timing Parameters)

- 1.3 技术演进:DDR2 到 DDR5

-

- Linux 平台实现

-

- 2.1 内存控制器驱动

- 2.2 初始化序列 (Initialization Sequence)

- 2.3 Linux 内存管理架构

-

- 性能调优实战

-

- 3.1 基准测试 (Benchmarking)

- 3.2 调优策略

-

- 参考文献

-

1. DDR 技术原理与物理架构

DDR (Double Data Rate) SDRAM 是现代计算机系统中不可或缺的主存储器技术。其核心优势在于能够在时钟信号的上升沿 和下降沿同时传输数据,从而在不增加时钟频率的情况下将数据传输速率翻倍。

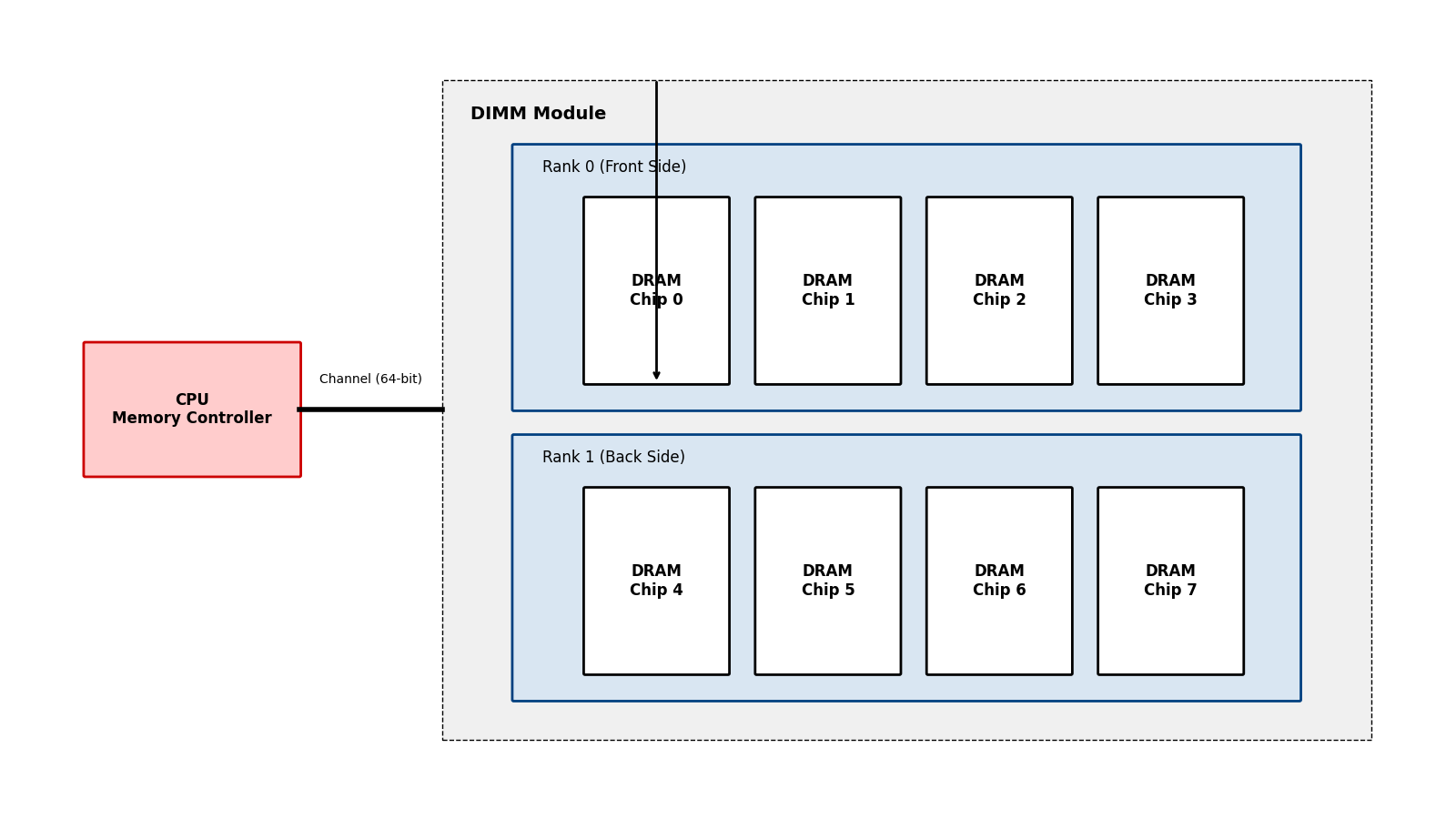

1.1 物理结构:从 Channel 到 Cell

DDR 内存的物理组织结构是一个层级化的树状结构,理解这一结构对于进行性能调优至关重要。

- Channel (通道): 内存控制器与内存模块之间的物理通路。双通道(Dual Channel)意味着有两个独立的 64-bit 数据通路,理论带宽翻倍。

- DIMM (Dual Inline Memory Module): 物理内存条。

- Rank: 内存条上的一组内存颗粒(Chips),共享同一组片选信号(CS#)。一个 DIMM 可能包含 1 个、2 个或 4 个 Rank。

- Chip (颗粒): 单个 DRAM 芯片。

- Bank: 芯片内部的独立逻辑单元。DDR3/4 通常有 8 个或 16 个 Bank。多个 Bank 可以并行工作以掩盖访问延迟。

- Row (Page) & Column : 每个 Bank 内部是一个二维矩阵。读取数据时,首先通过

ACTIVATE命令打开一行(Row),将其数据加载到 Row Buffer (Sense Amplifiers),然后通过READ命令读取指定的列(Column)。

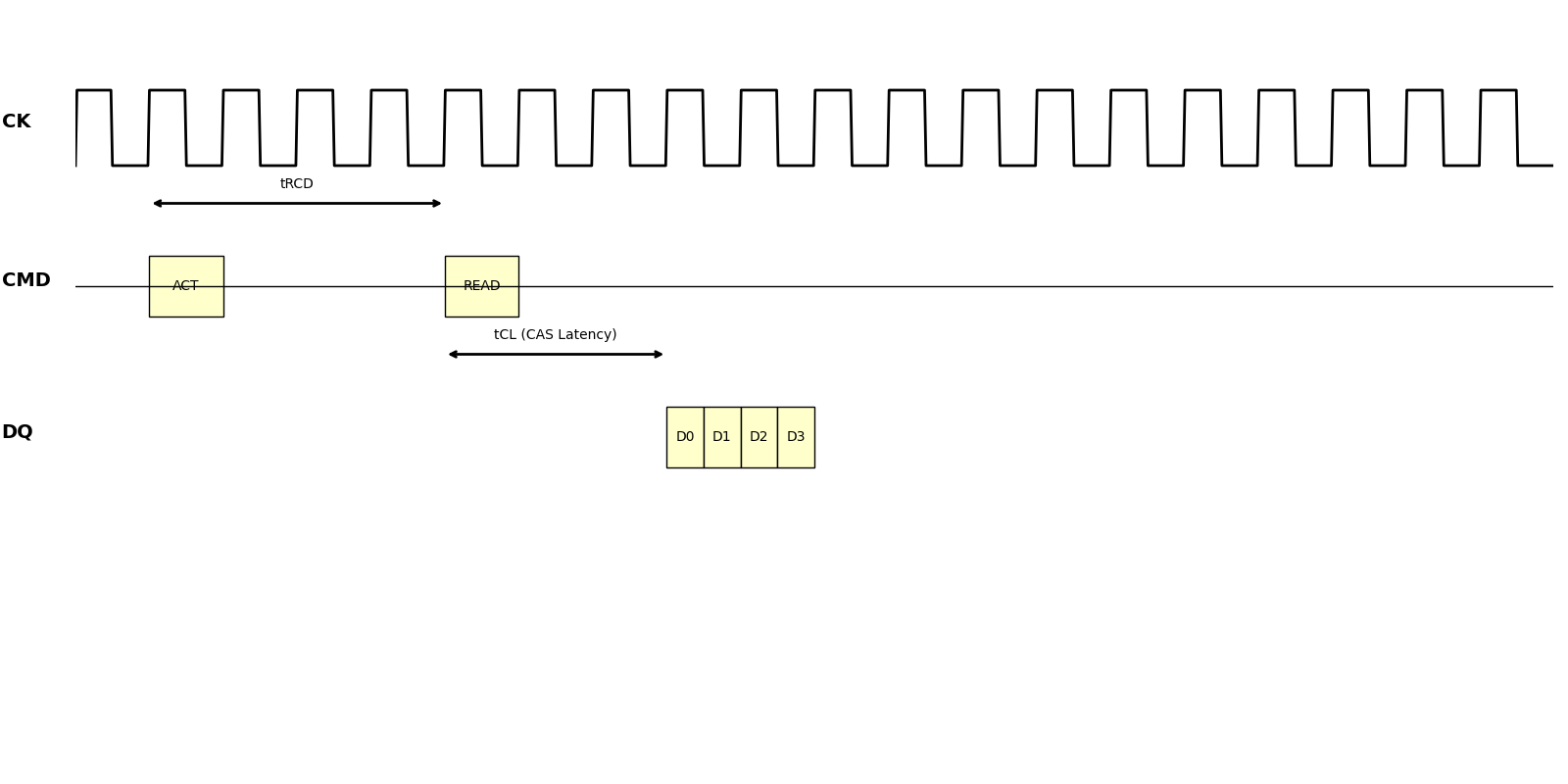

1.2 关键时序参数 (Timing Parameters)

DDR 的性能不仅取决于频率,还严重依赖于时序参数(Timings)。

- tCL (CAS Latency) : 发送

READ命令到数据开始输出的延迟时钟周期数。这是对性能影响最大的参数。 - tRCD (RAS to CAS Delay): 打开行(ACTIVATE)到可以发送读写命令(READ/WRITE)之间的最小延迟。

- tRP (Row Precharge Time): 关闭当前行(PRECHARGE)到可以打开下一行(ACTIVATE)的最小延迟。

- tRAS (Row Active Time): 一行数据被打开后,必须保持激活状态的最小时间。

典型读操作流程:

PRECHARGE: 关闭之前的 Row (耗时 tRP)。ACTIVATE: 打开新的 Row (耗时 tRCD)。READ: 发送读命令 (耗时 tCL)。DATA: 数据在总线上突发传输 (Burst Transfer)。

1.3 技术演进:DDR2 到 DDR5

| 特性 | DDR2 | DDR3 | DDR4 | DDR5 |

|---|---|---|---|---|

| 电压 (VDD) | 1.8V | 1.5V / 1.35V | 1.2V | 1.1V |

| Prefetch | 4n | 8n | 8n | 16n |

| Data Rate | 400-1066 MT/s | 800-2133 MT/s | 1600-3200 MT/s | 4800-8400+ MT/s |

| 关键改进 | On-Die Termination | Fly-by topology | Bank Groups | Dual 32-bit Channels, On-die ECC |

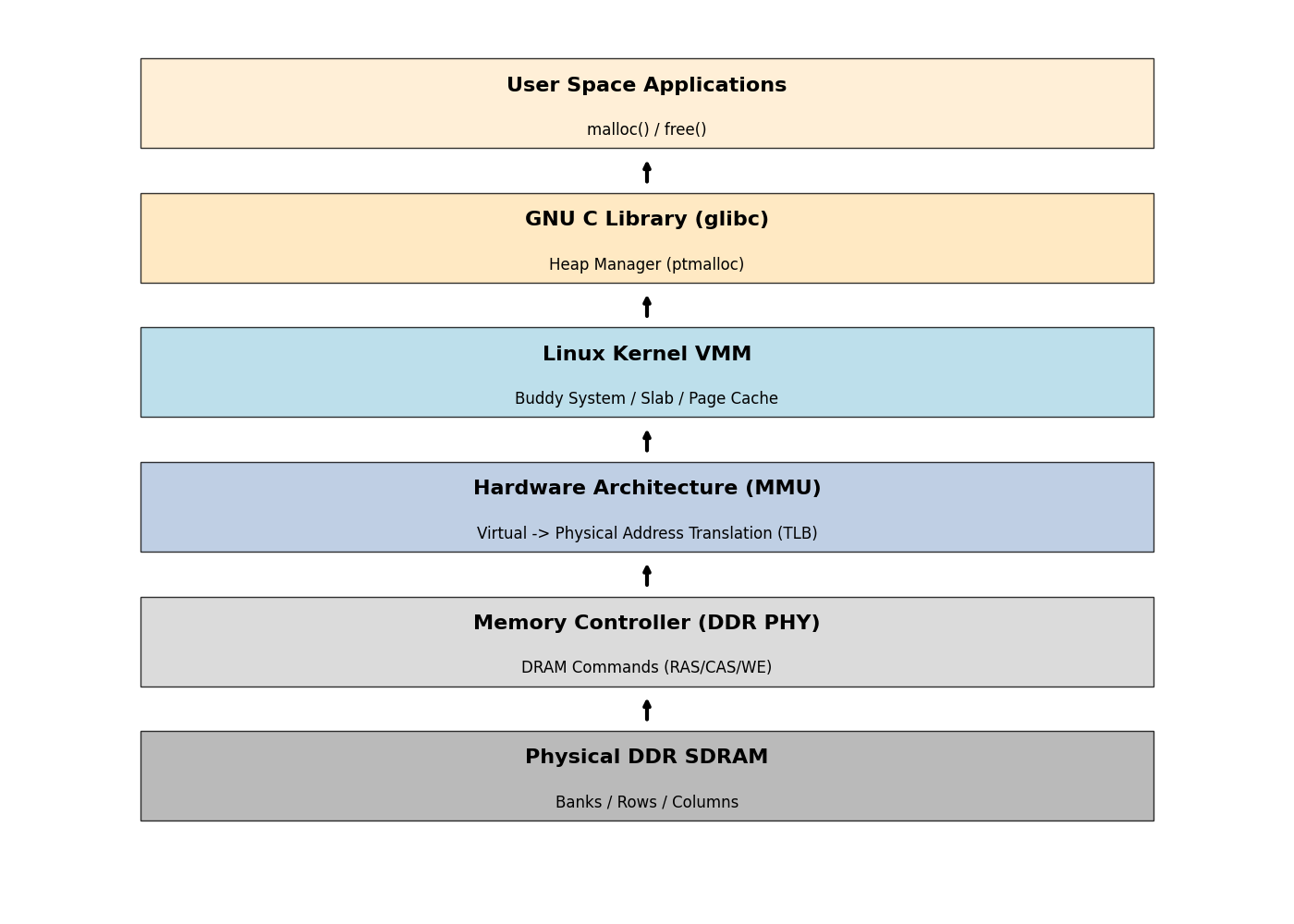

2. Linux 平台实现

在 Linux 系统中,DDR 的管理涉及从 Bootloader 初始化到内核内存管理子系统的全流程。

2.1 内存控制器驱动

内存控制器(DDR Controller, DDRC)驱动通常位于内核源码的 drivers/memory 目录中。它负责配置 DDRC 的寄存器以适配具体的颗粒参数。

主要职责:

- 配置时序参数(tCL, tRCD, etc.)。

- 执行 DDR Training(训练):自动校准数据眼图(Data Eye)、DQS 延迟等,以确保信号完整性。

- 处理动态频率调整(DDR DFS)。

2.2 初始化序列 (Initialization Sequence)

内存初始化通常在 Bootloader(如 U-Boot)的 SPL 阶段完成,因为主 U-Boot 和内核都需要运行在 DDR 上。

- Power On: 上电,时钟稳定。

- Reset: 复位 DDRC 和 PHY。

- Parameter Config: 写入 JEDEC 标准参数(来自 SPD EEPROM 或硬编码)。

- ZQ Calibration: 校准输出阻抗(Output Impedance)。

- Training :

- Write Leveling: 对齐时钟(CK)和数据选通(DQS)。

- Gate Training: 确定读取数据的有效窗口。

- Data Eye Training: 寻找最佳采样点。

- Enable: 使能控制器,DDR 进入 Ready 状态。

2.3 Linux 内存管理架构

- Physical Memory : 内核通过

memblock(启动早期)和buddy system(伙伴系统,启动后)管理物理页框(Page Frames)。 - Virtual Memory: 通过 MMU 页表(Page Tables)将虚拟地址映射到物理地址。

- Slab/Slub Allocator : 在 Buddy System 之上,管理小块内存对象(如

task_struct,inode)。

相关内核配置:

CONFIG_MEMORY_HOTPLUG: 支持内存热插拔。CONFIG_CMA: 连续内存分配器(Contiguous Memory Allocator),用于 DMA 设备。CONFIG_TRANSPARENT_HUGEPAGE: 透明大页,减少 TLB Miss。

3. 性能调优实战

3.1 基准测试 (Benchmarking)

使用 mbw 和 lmbench 测试内存带宽和延迟。

bash

# 安装 mbw

sudo apt-get install mbw

# 测试内存拷贝带宽 (256MB 数组)

# -t0: memcpy, -t1: dumb (for loop), -t2: memcpy with block size

mbw -n 10 256解读输出:

text

AVG Method: MEMCPY Elapsed: 0.04567 MiB: 256.00000 Copy: 5605.123 MiB/s

AVG Method: DUMB Elapsed: 0.08912 MiB: 256.00000 Copy: 2872.543 MiB/s3.2 调优策略

- Bank Interleaving (Bank 交错) :

- 确保内存控制器配置启用了 Bank Interleaving。这允许连续的内存访问分散到不同的 Bank,掩盖 tRP 和 tRCD 延迟。

- NUMA 优化 :

- 在多路服务器上,使用

numactl将进程绑定到本地内存节点,避免跨 Socket 访问(QPI/UPI 开销)。 numactl --cpubind=0 --membind=0 ./my_app

- 在多路服务器上,使用

- Huge Pages :

- 对于占用大量内存的应用(如数据库),开启 Huge Pages(2MB/1GB)可以显著减小页表大小,降低 TLB Miss 率。

echo always > /sys/kernel/mm/transparent_hugepage/enabled

- DDR 频率与时序 :

- 在 BIOS 或 Bootloader 中尝试更高的频率(如 DDR4-3200)或更紧的时序(Lower CAS Latency)。注意需进行稳定性测试(如 MemTest86)。

4. 参考文献

- JEDEC Standard No. 79-4B (DDR4 SDRAM Specification).

- Linux Kernel Documentation:

Documentation/vm/. - Ulrich Drepper, "What Every Programmer Should Know About Memory", 2007.

- Micron Technology, "DDR4 SDRAM System-Level Timing Overview", TN-40-02.