DDR的演进

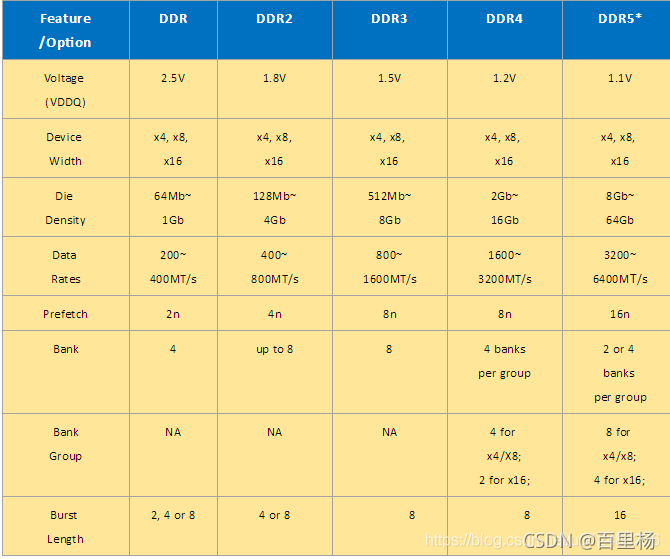

DDR发展到现在已经经历了五代。

- DDR (DDR1): 第一代 DDR 内存。奠定了双倍速率的基础。

- DDR2: 进一步提高了时钟频率和带宽,降低了工作电压(1.8V),改进了封装和信号完整性。引入了 Prefetch 技术(通常是 4-bit)。

- DDR3: 再次大幅提升频率和带宽,电压进一步降低到 1.5V(后期有 1.35V 低电压版 DDR3L)。Prefetch 增加到 8-bit。成为长期的主流标准。

- DDR4: 频率、带宽和容量(单条可达 32GB+)再次飞跃,工作电压降至 1.2V(也有 DDR4L)。改进了内部架构和可靠性。引入了 Bank Group 设计提升效率。

- DDR5: 当前最新一代主流标准。

- 核心电压进一步降至 1.1V。

- 带宽再次翻倍(甚至更高): 通过将每个内存模块(DIMM)的通道拆分成两个独立的 32-bit 子通道(相当于每个 DIMM 有 2 个 32-bit 通道),并显著提升基础频率。

- 容量巨大提升: 单条容量可达 128GB 甚至更高。

- 集成电源管理芯片: 将原本主板上的电压调节模块移到内存条本身,提高稳定性和供电效率。

- 更强的纠错能力: 支持片内 ECC(并非所有消费级条都有,但架构支持)。

- 更高的密度和能效比。

DDR到DDR5的主要变化主要表现在DDR的性能、容量、省电三个方面:IO的速率也越来越高,规范的工作电压越来越低,芯片容量越来越大。

除了电压,容量和IO的速率变化之外,还包含Bank、Bank Group、Prefetch和Burst Length的演进,bank数越来越多,到DDR4出现bank group,prefetch也从2n增加到4n、8n。

- Device Width:颗粒位宽,常见为4/8/16bit。

- Die Density:颗粒密度,也就是容量,随着DDR代数迭代,容量越来越大。

- Bank:DDR4以前是没有Bank Group的,所以该值就表示整个颗粒中Bank数量。但是在DDR4和DDR5中,就表示每个Bank Group中Bank的数量,整个颗粒Bank数量 = Bank Group * Bank。

- Bank Group:Bank分组数量,该特性只存在于DDR4和DDR5中。

DIMM、Chip、RANK、CHANNEL

DIMM

DIMM(Dual Inline Memory Module)双列直插内存模块,也就是我们常见的内存条。

Chip

Chip是内存条上的一个芯片,俗称内存颗粒。

RANK

我们知道,CPU与内存之间的数据接口位宽是64bit,也就意味着CPU在一个时钟周期内会向内存发送或从内存读取64bit的数据。

可是,单个内存颗粒的位宽仅有4bit、8bit或16bit,个别也有32bit的。显然发送方和接收方的位宽必须一致,不能说我发了64位数据出来,你才收到前面的16位,后面的就丢掉了。因此,必须把多个颗粒并联起来,组成一个位宽为64bit的数据集合,才可以和CPU互连。

我们可以,把这样一个由多个颗粒组成的64bit位宽集合,称为一个RANK。

比如,128MB内存芯片,其位宽为8bit,那么需要8块芯片才能组成64bit位宽,将这些芯片焊接到一块DIMM上,插到主板上就可以使用了。这时,该DIMM的总容量就是128MB*8=1GB。

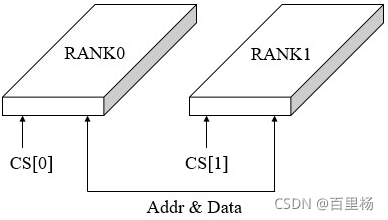

假设,该主板只有一个DIMM插槽,并且我们还想将DIMM扩容至2GB,并且还只能使用128MB,位宽为8bit的内存颗粒。那么应该如何实现呢?

回答:在一个DIMM上放两个RANK,然后用片选信号来选择访问RANK0或RANK1,RANK0和RANK1的其他信号线全部连在一起。

为了保证和CPU的沟通,一个DIMM中至少要有一个RANK。但是,为了保证有一定的内存容量,经常是采用一个DIMM两个RANK的结构。

CHANNEL

内存控制器(Memory Controller)是计算机系统内部控制内存并且负责内存与CPU之间数据交换的重要组成部分。

CHANNEL即内存通道,实际上是一种内存的带宽加速技术。一个DDR控制器中可能有一个内存通道,也可能有两个内存通道。最常见的是双通道,民用级电脑都支持,服务器还有3通道和4通道等。

内存通道实际是对应一组时钟、命令、地址、数据线,这组总线也就是所谓的内存通道。一般一个内存通道,可以连接若干个DIMM(多个DIMM通过片选控制)。

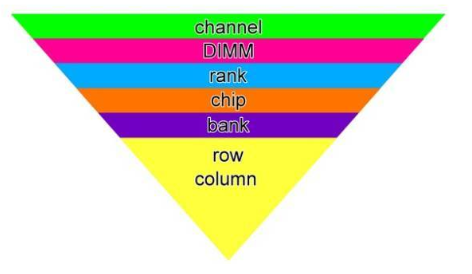

从内存控制器到内存颗粒内部逻辑,笼统上讲从大到小为:channel>DIMM>rank>chip>bank>row/column:

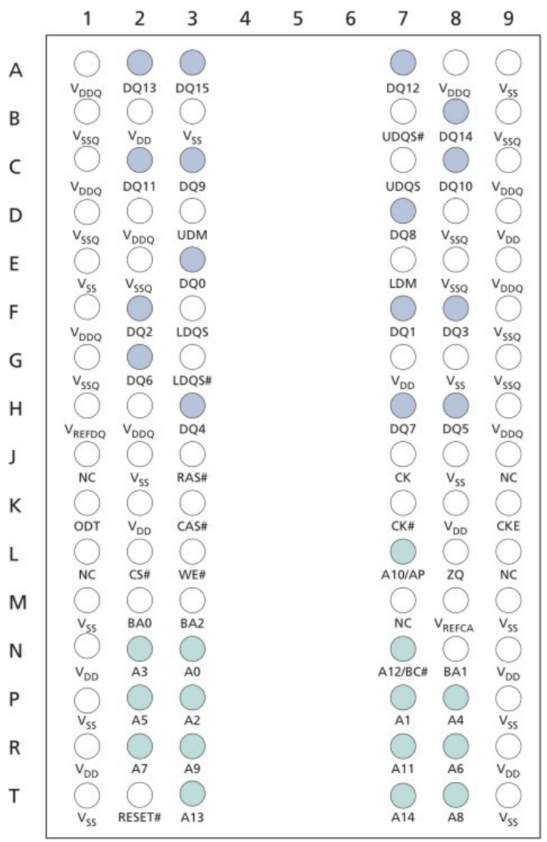

DDR的引脚定义(以DDR3/MT41J256M16HA-15E为例)

- CK、CK#:差分时钟输入

- CKE:时钟使能输入。CKE为高时,使能时钟正常工作;CKE为低时,使能Power-down模式或自刷新功能。

- CS# :片选信号

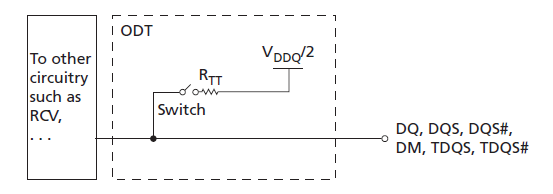

- ODT:阻抗匹配使能。ODT使能DDR3内部的终结电阻,当其为高时有效,优化DQ/DM/DQS 的信号质量。

- RAS#、CAS#、WE# :命令输入。定义 DDR3 芯片的操作命令。

- LDM、UDM:写入数据掩码。在写入操作时,如果DM信号为高,则写入数据被屏蔽;如果DM 信号为低,则写入数据正常锁存;LDM控制DQ0~DQ7,UDM控制DQ8~DQ15。

- BA[2:0]:BANK地址输入。在激活、读取、写入或预充电命令操作时,提供 BANK 地址;在加载模式寄存器命令的时候,决定设置哪种模式寄存器。

- A[14:0]:地址输入。在激活命令的时候提供 Row 地址; 在读取/写入命令的时候提供Column 地址和预充电位(A10) ;

在加载模式寄存器命令的时候提供 op-code;

Row 地址:A[14:0] ;

Column 地址:A[9:0] ;

A12/BC#:当在模式寄存器中使能后,A12 在读取/写入命令的时候决定是否执行突发突变(burst chop)功能。 - RESET#:复位输入。

- DQ[15:0] :数据总线。

- LDQS、 LDQS#:低字节数据选通。

作为输出信号时,与读取的数据同步,边沿对齐;

作为输入信号时,与写入的数据同步,中心对齐;

LDQS#是否使用,需要在模式寄存器中设置。 - UDQS、 UDQS#:高字节数据选通。

作为输出信号时,与读取的数据同步,边沿对齐;

作为输入信号时,与写入的数据同步,中心对齐;

UDQS#是否使用,需要在模式寄存器中设置。 - VDD:供电电源:1.5V±0.075V。

- VDDQ:DQ 供电电源:1.5V±0.075V。

- VREFCA:电源 控制、命令和地址信号的参考电压。

- VREFDQ:电源 数据信号的参考电压。

- VSS:电源 地。

- VSSQ:电源 DQ 地。

- ZQ:输出驱动校正的外部参考点。

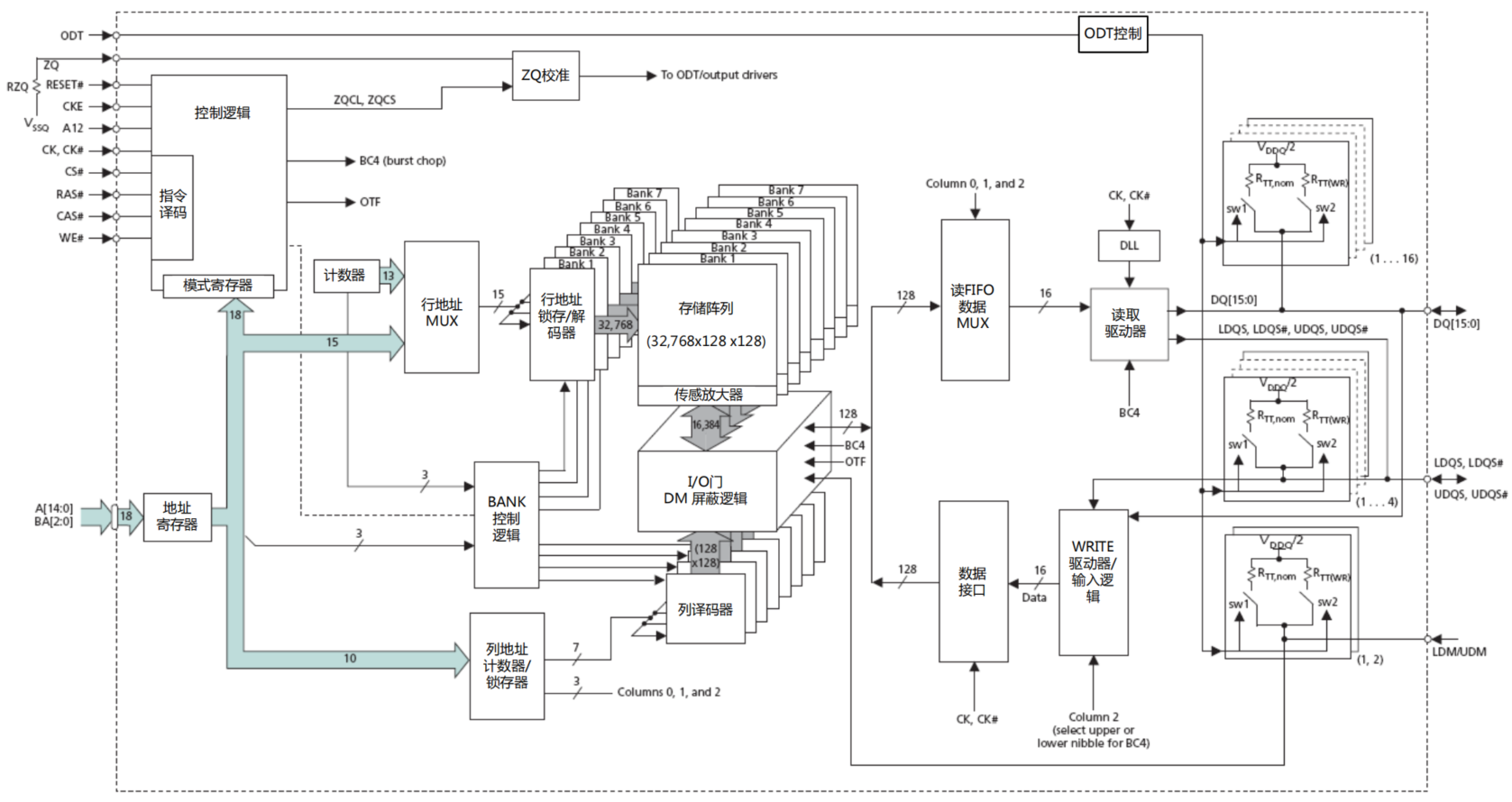

DDR3框图

固定突发长度(BL):8

4-bit 突发突变(Burst Chop)功能

功能说明

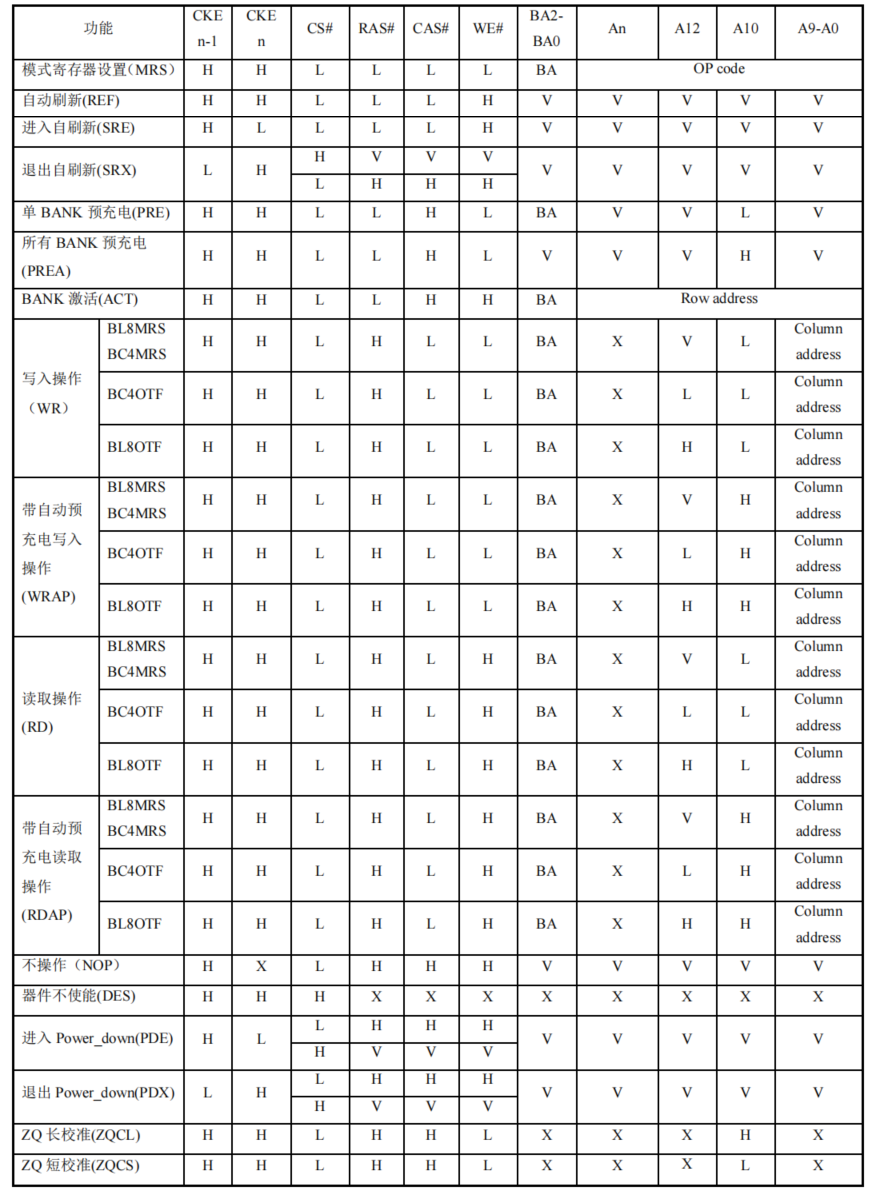

命令真值表

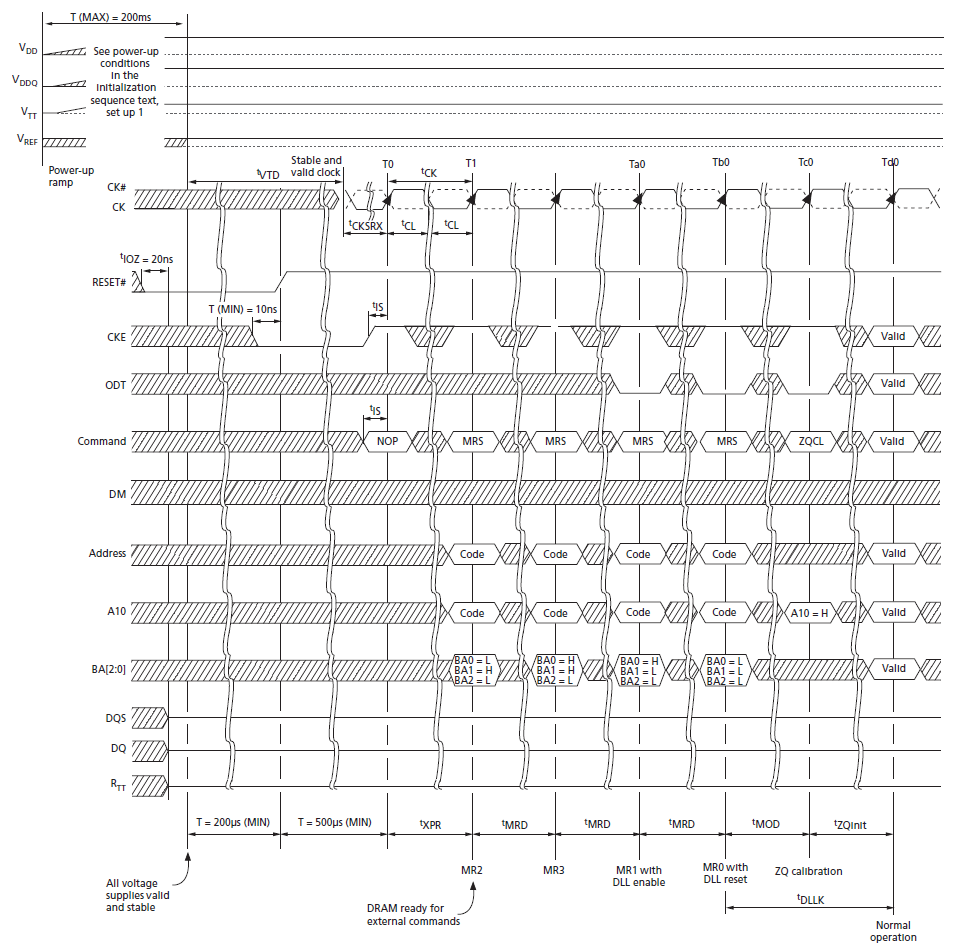

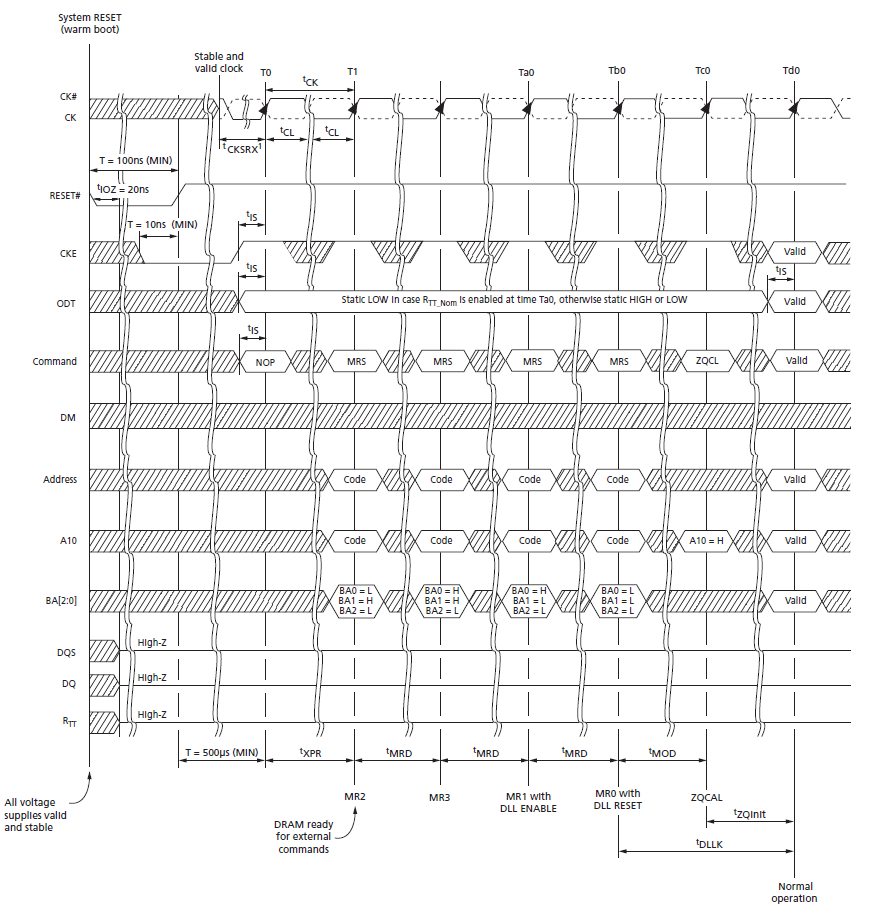

芯片初始化

DDR3 芯片在上电以后,必须运行初始化时序对芯片进行必要的功能配置后,才能进行正常的读写操作,其初始化时序如图 9 所示。

需要把MR2、MR3、MR1、MR0配置好。

模式寄存器(MR0-MR3)

模式寄存器(MR0-MR3)用来定义 DDR3 SDRAM 的工作模式,利用加载模式寄存器(MRS)命令进行设置,芯片会一直保持所设置的信息直到重新设置、芯片复位或掉电,重新设置模式寄存器不会修改芯片内部所存储的数据。

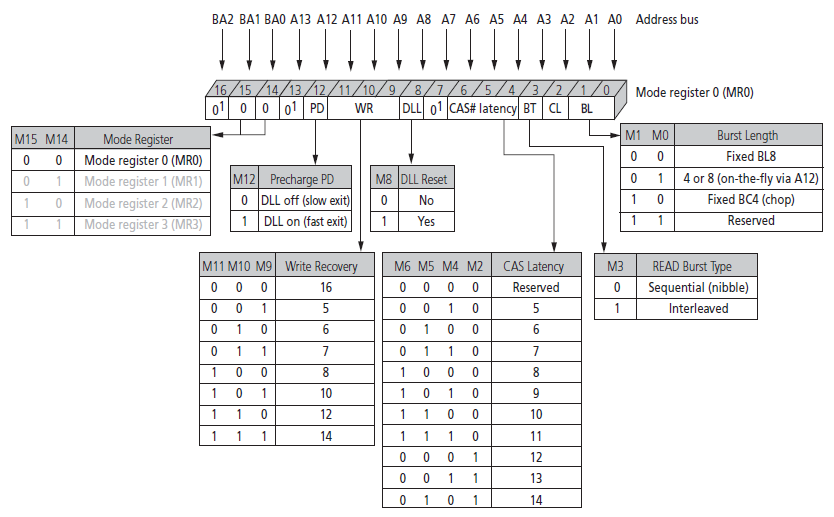

MR0 模式寄存器

MR0 模式寄存器用来定义 DDR3 SDRAM 的突发长度(Burst Length)、突发类型(Burst Type)、CAS 延迟(CAS latency)、操作模式、DLL 复位、写恢复和预充电 Power_down 模式,如图 5 所示。

① Burst Length(BL):突发长度。DDR3 的读写操作都是突发类型的,突发长度决定了在读取操作或写入操作中列空间的最大个数,可根据要求设置为 4(突变模式),8(固定)或利用 A12 管脚在读写命令的时候进行设置(on-the-fly)。

② Burst Type:突发类型。突发类型分为 sequential 或 interleaved,只在读取操作中有用。由 M3 决定。

③ CAS Latency(CL):列地址选通脉冲时间延迟。指在读取数据时,读取命令到数据输出需要等待的时钟周期数,可设置为 5~11。

④ DLL Reset:DLL 复位设置,当设置 M8 为 1 时,激活 DLL 复位功能。

⑤ Write Recovery:定义写恢复时间,WR= tWR/tCK,可设置为 5~12。

⑥ Precharge Power-Down 模式:当 M12 设置为 0 时,在预充电 Power-Down模式下,DLL 关闭,芯片处于待机模式;当 M12 设置为 1 时,在预充电 Power-Down模式下,DLL 打开,芯片处于快速退出预充电 Power-Down 模式。

⑦ Mode Register Definition:模式寄存器定义,由 BA1 和 BA0 决定 LMR 命令所操作的模式寄存器属于哪种模式寄存器。

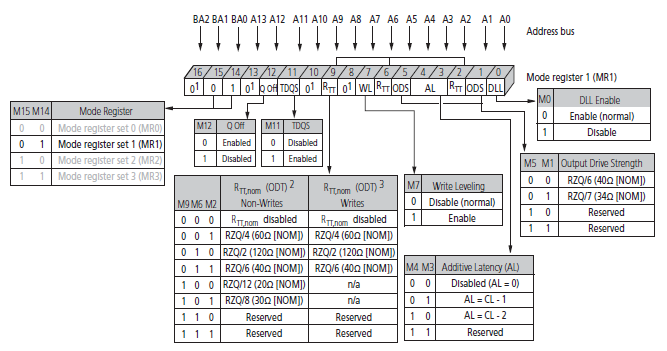

MR1 模式寄存器

MR1 模式寄存器定义 DDR3 SDRAM 额外的一些设置,有数据输出使能(QOFF)、 DLL 使能/禁止、 ODT 的电阻值、写入均衡控制、 CAS 附加延迟设置和输出驱动强度选择等,如图 6 所示。

① DLL Enable/Disable: DLL 使能控制。在正常操作时, DLL 必须被使能,在上电初始化的时候进行使能设置。

② Output Drive Strength:输出驱动强度。正常情况下设置为 RZQ/7( 34Ω[NOM]),为了校准输出驱动阻抗,外部需要有 RZQ 电阻(240Ω± 10%)连接到ZQ 管脚上。

③ CAS# Additive Latency(AL): CAS 附加延迟,可设置为 0、 CL-1、 CL-2。

④ RTT: ODT 电阻的设置和 RZQ 电阻相关,可按需求设置。

⑤ WL: 写入均衡功能使能,通过 MR1[7]设置。

⑥ TDQS 使能控制:只有在 8bit 模式下才使用。

⑦ 数据输出使能控制: M12 设置是否正常输出, M12=0 时正常输出,否则输出禁止。

⑧ Mode Register Definition:模式寄存器定义,由 BA1 和 BA0 决定 LMR 命令所操作的模式寄存器属于哪种模式寄存器。

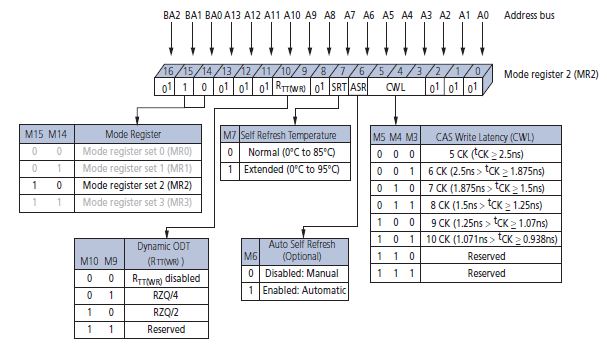

MR2 模式寄存器

MR2 模式寄存器定义了 DDR3 SDRAM 的其他一些设置,有 CAS 写入延迟、自动自刷新(ASR)、温度自刷新(SRT)、动态 ODT 等,如图 7 所示。

① CWL: CAS 写入延迟。定义在写入操作中,在附件延迟( AL)后增加的CWL 延迟时钟数,可设置为 5~8。

② ASR:自动自刷新使能。

③ SRT:自刷新温度范围使能。

④ 动态 ODT:动态 ODT 使能。如果动态 ODT 使能,则在写入操作的时候,DRAM 从正常的 ODT 模式切换到动态 ODT 模式进行工作。

⑤ Mode Register Definition:模式寄存器定义,由 BA1 和 BA0 决定 LMR 命令所操作的模式寄存器属于哪种模式寄存器。

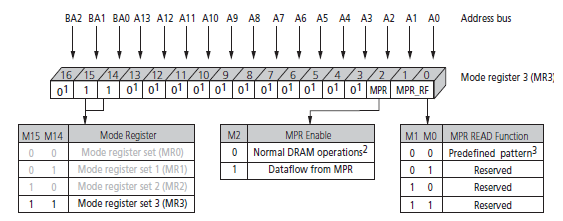

MR3 模式寄存器

MR3 定义了 MULTIPURPOSE REGISTER(MPR)功能的控制位,如图 8 所示。

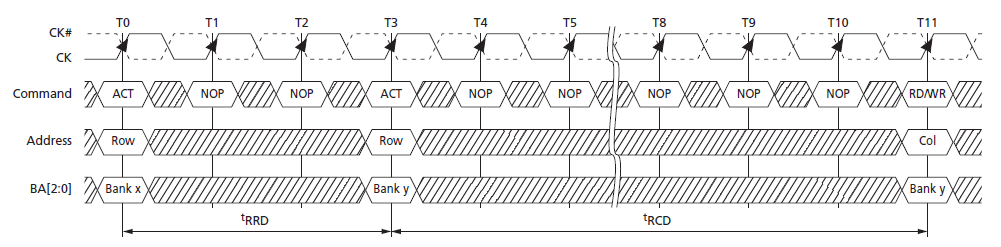

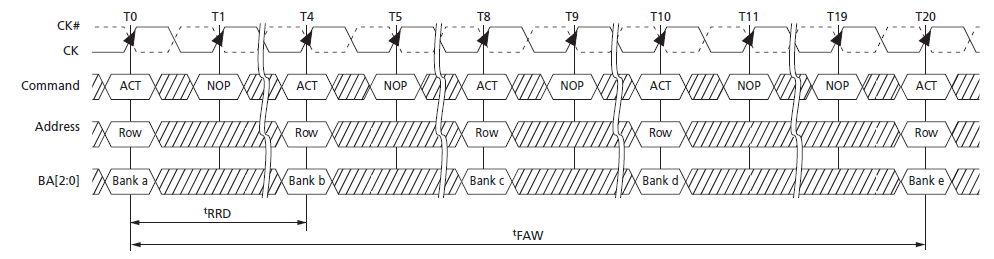

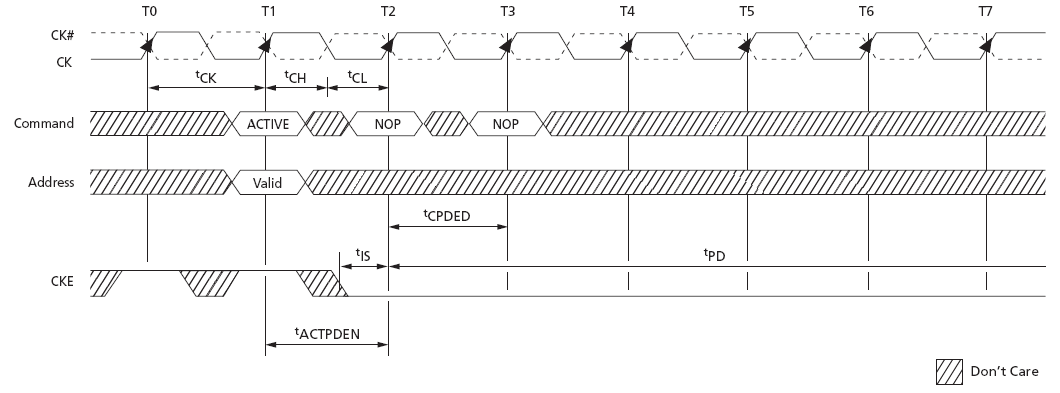

激活操作

激活操作(ACTIVATE)是指在读取或者写入操作之前,芯片需要将要操作的Bank 和 Row 进行激活,方便后续的操作。激活操作是通过激活命令实现的,在激活命令经过时间 tRCD 后,可以进行读取或写入操作,而在不同 Bank 之间激活命令的间隔时间是 tRRD,如图 10 所示。

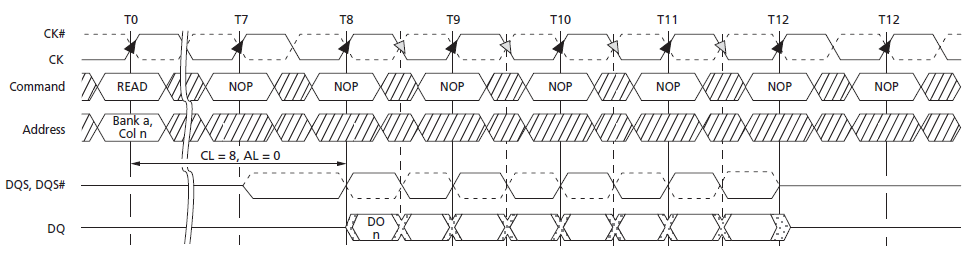

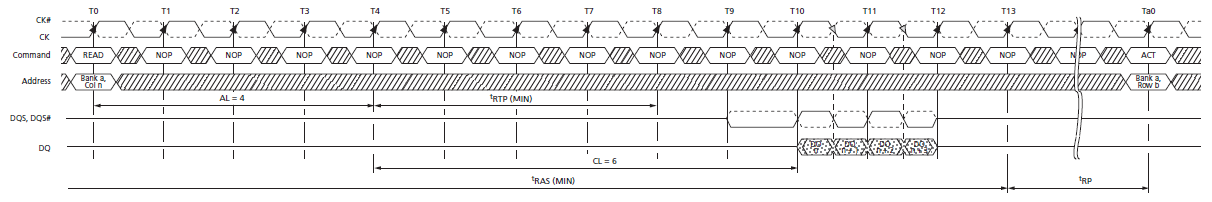

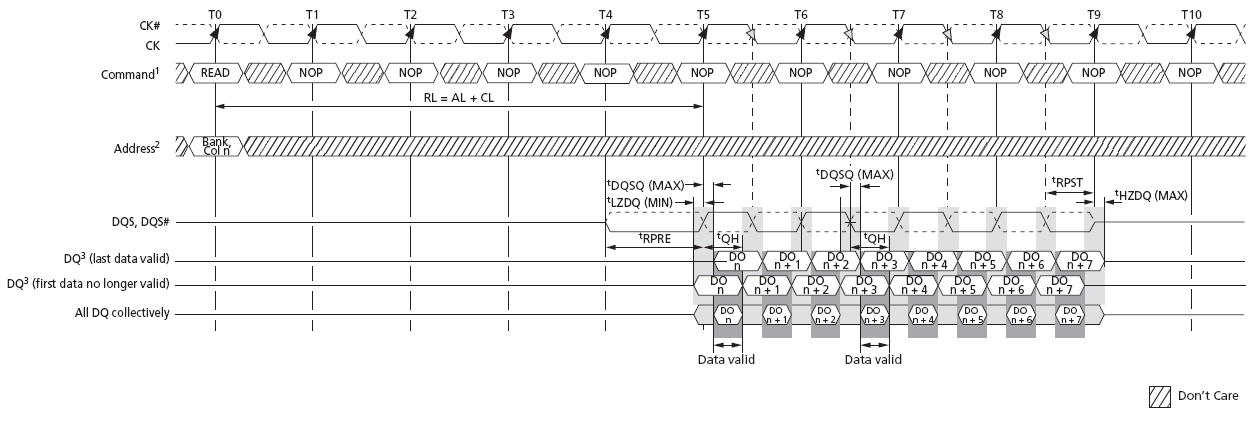

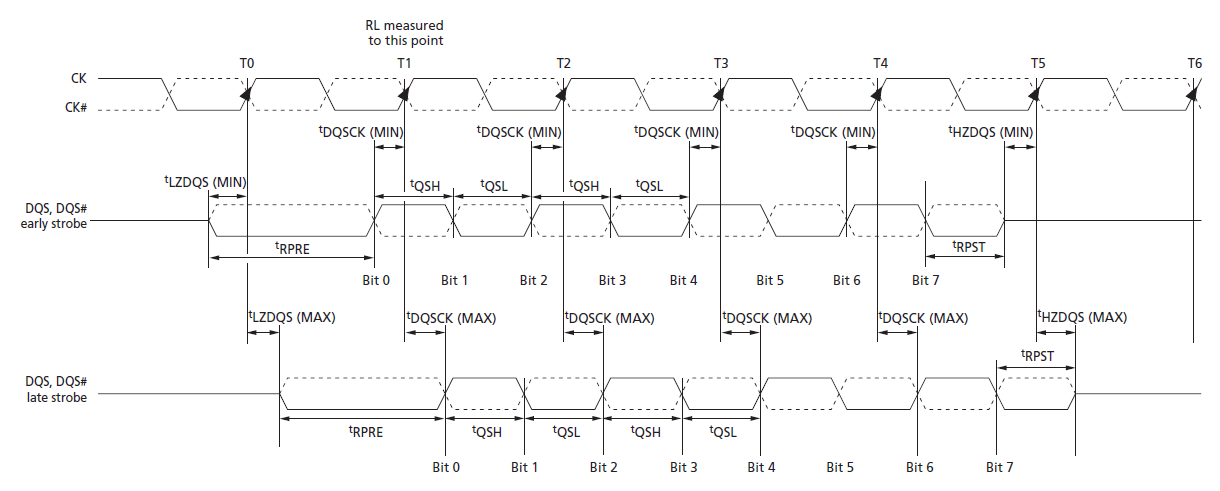

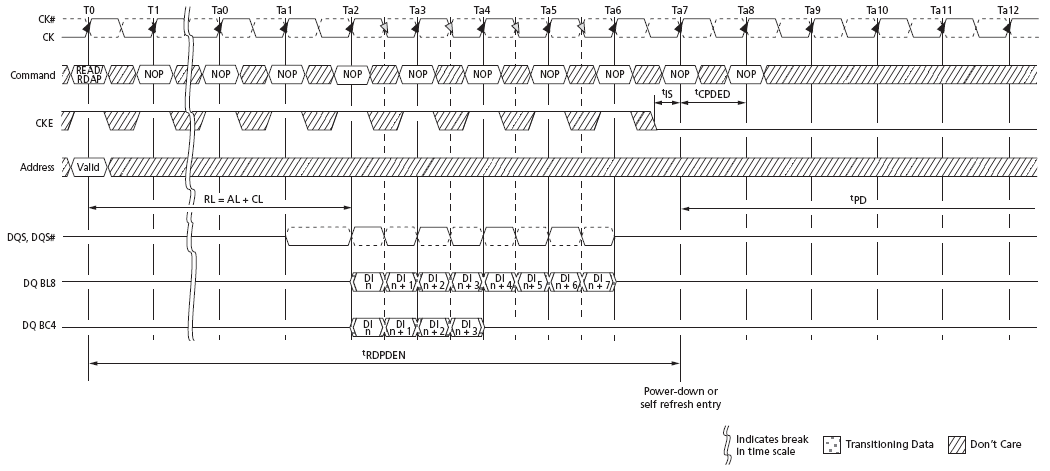

读取操作

突发读取操作是通过读取命令实现的,在读取命令中提供开始读取数据的Column 和 Bank,然后经过读取延迟(Read Latency)后,连续读出指定数量的数据。RL 的值由 AL 和 CL 定义, RL=AL+CL。 AL 和 CL 的值可通过 MRS 命令进行定义。图 11 展示了 CL=8, AL=0 设置下的 RL 时序。

在读取操作中, DQS/DQS#与输出数据同步,在 DQS/DQS#的上升/下降沿都会读取到数据。 DDR3 SDRAM 的突发读取操作不允许中断或者删减。在突发读取操作后,需要添加一个预充电(PRECHARGE)命令,来关闭激活的 Row。根据 A10管脚的不同,决定了预充电命令需要手动添加还是自动添加。在读取操作时,如果地址线 A10 为高,则在读取操作后自动会加一个预充电命令;而如果地址线 A10为低,则需要在读取命令之后,按照要求添加一个预充电命令,相应时序波形如图12 和图 13 所示。

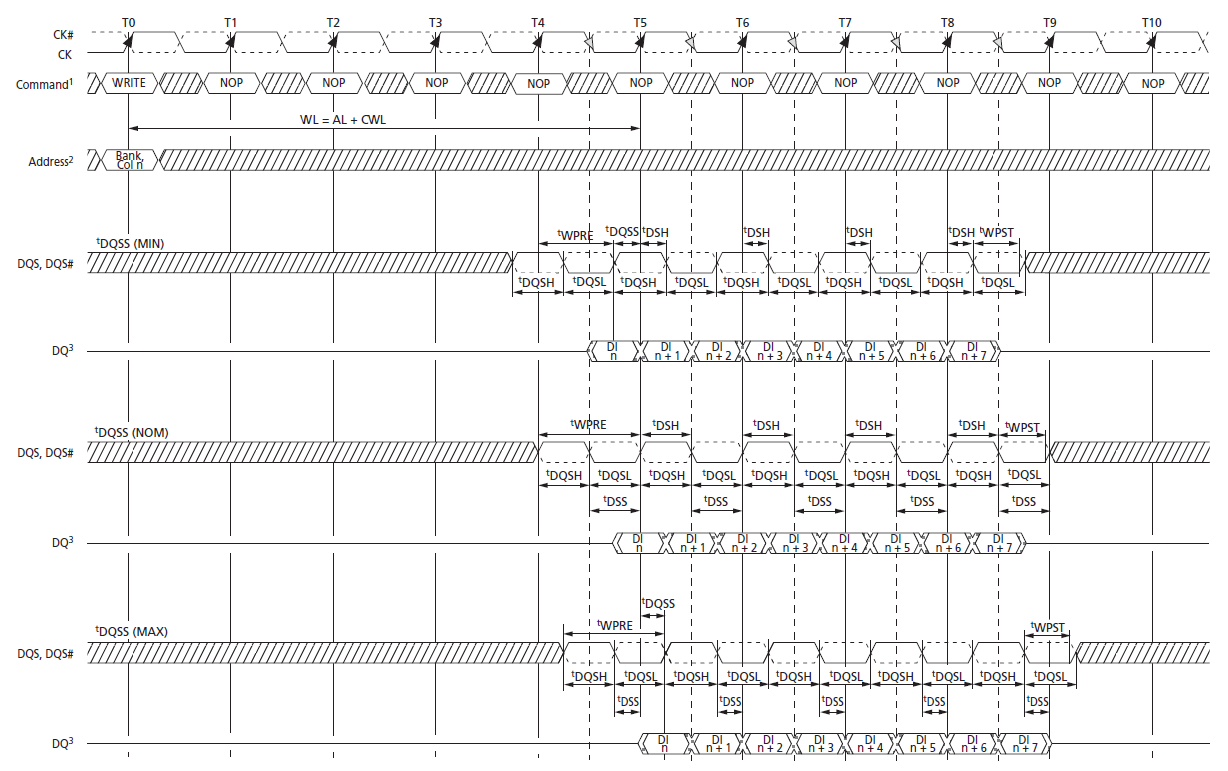

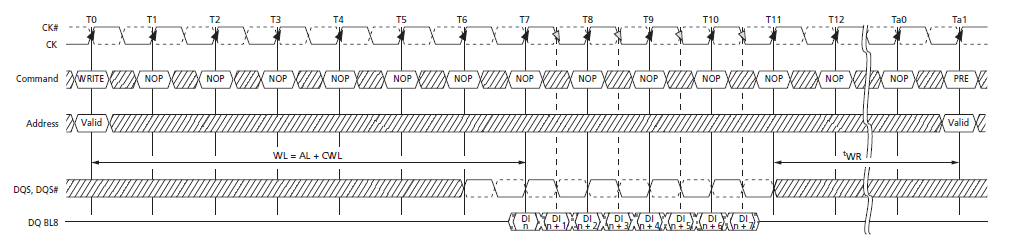

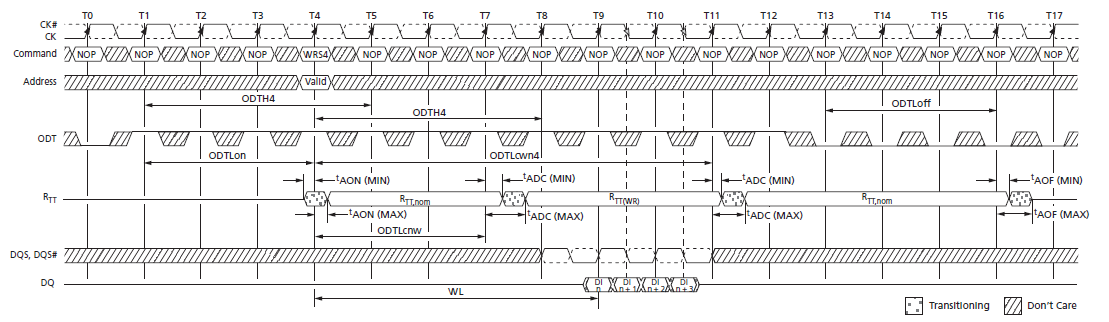

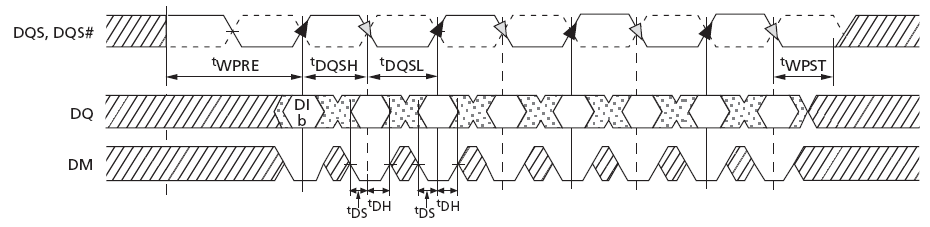

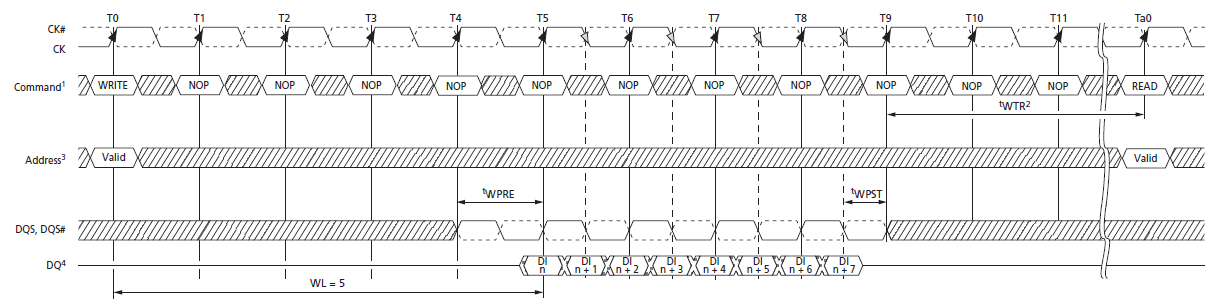

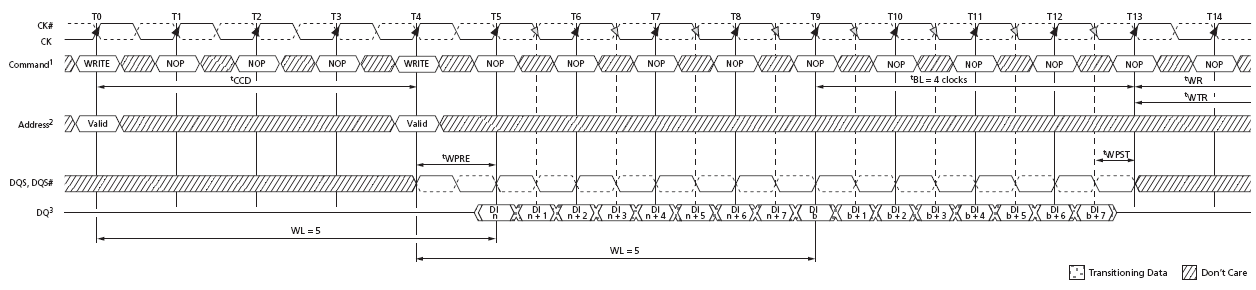

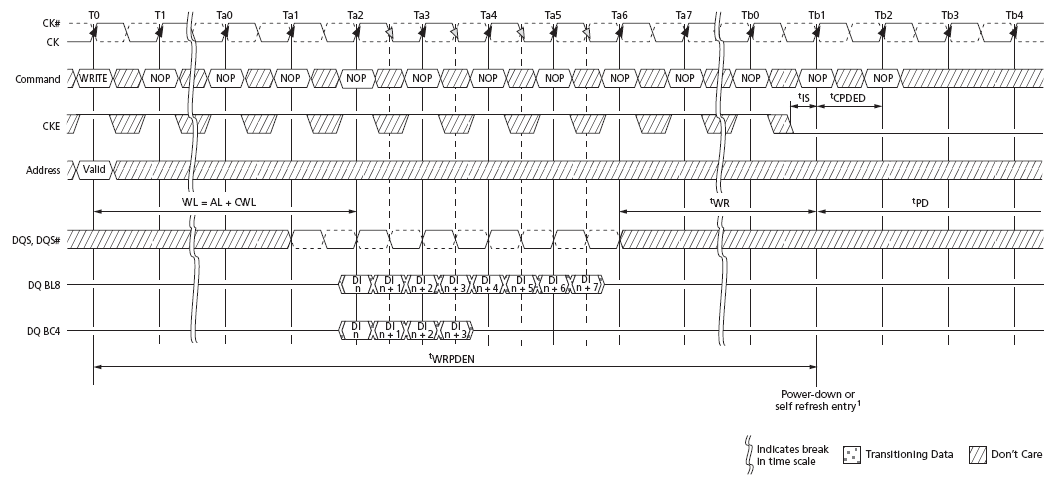

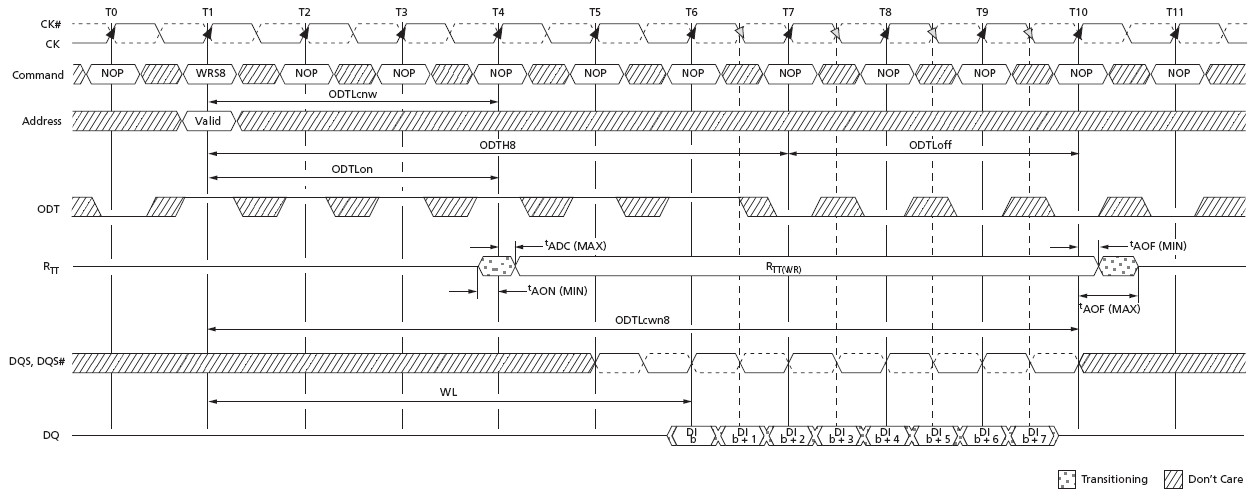

写入操作

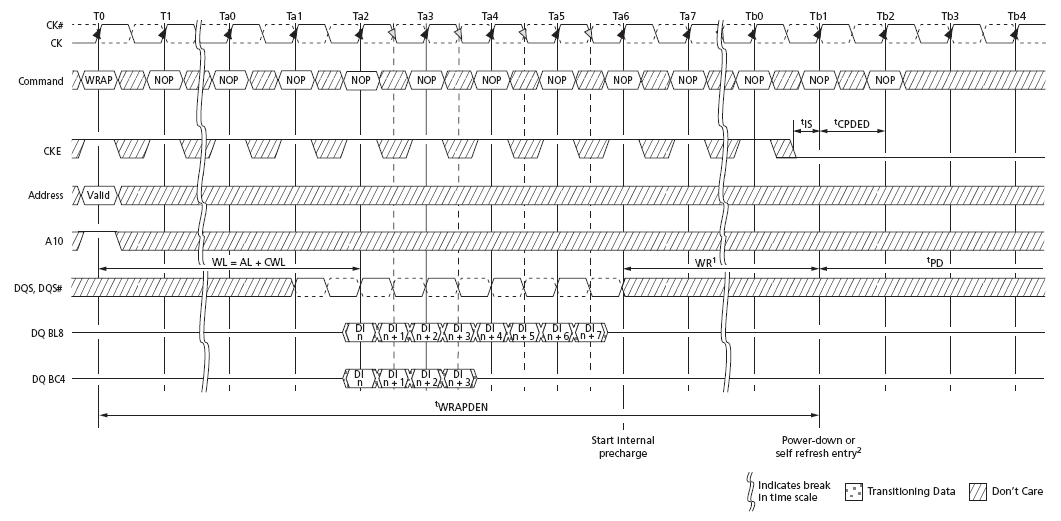

突发写入操作通过写入命令实现, DDR3 利用 WL(Write Latency)来表明其延迟时间,与读取操作的 RL 功能一致,而WL=AL+CWL。在写入操作的时候,提供要写入的起始 Column 地址和 Bank 地址,同时是否加入自动预充电命令。如果加入自动预充电命令,则完成突发写入操作以后,就会自动关闭激活的 Row。

在突发写入操作中,第一个可用的输入数据在 WL 延时后的 DQS 的第一个上升沿被锁存,而后续的输入数据在每个 DQS 的上升沿/下降沿被锁存。

在写入命令和 DQS 的第一个上升沿之间的时间为 WL±tDQSS,图 14 中所表示的即为 tDQSS 的值处于正常情况和极限情况下的突发写入操作时序。

图 15 是当 BL=8 时的写入操作到预充电时序,可以看出,数据写入之后,需要等待 tWR 延时后才能加入预充电命令。

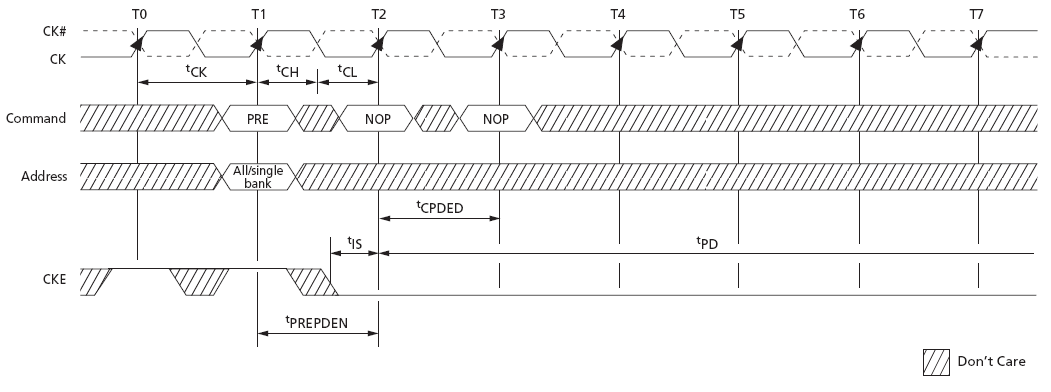

预充电操作(PRECHARGE)

预充电命令是用来关闭某个 BANK 已经激活的 Row 或者所有 BANK 已经激活的 Row。 A10 管脚用来检测是所有激活的 Row 被预充电还是单个 BANK 的 Row 被预充电,当 A10 管脚为高时,表明所有激活的 Row 都需要被预充电, BANK 地址无意义;而 A10 管脚为低时,单一 BANK 的 Row 被预充电,这时 BANK 地址所指代的就是需要预充电 Row 的 BANK 地址。

一旦 BANK 被预充电以后,则整个 BANK 的 Row 都被关闭,处于空闲状态,如果后续需要对 Row 进行读写操作,则需要重新激活后才能使用。

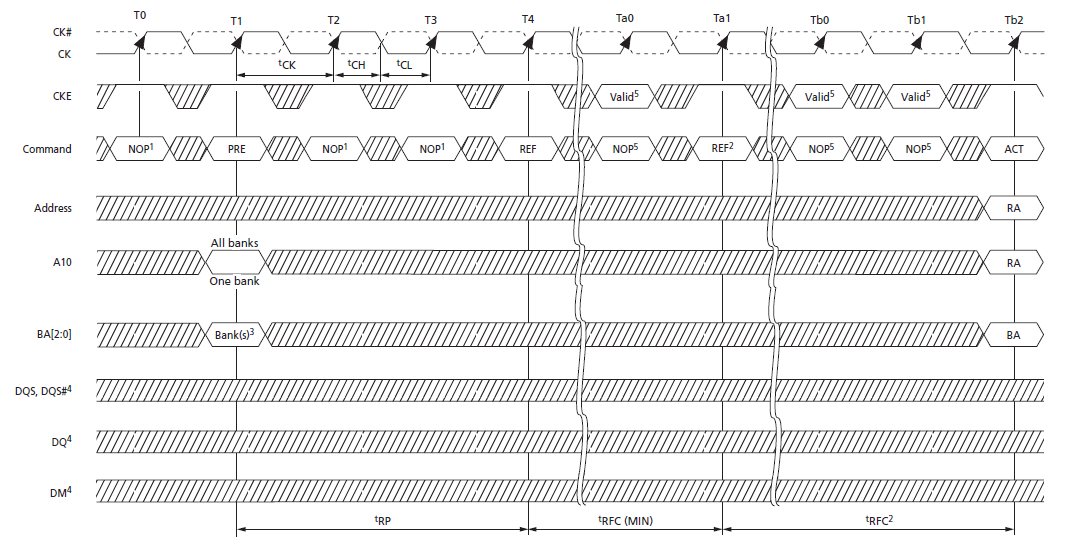

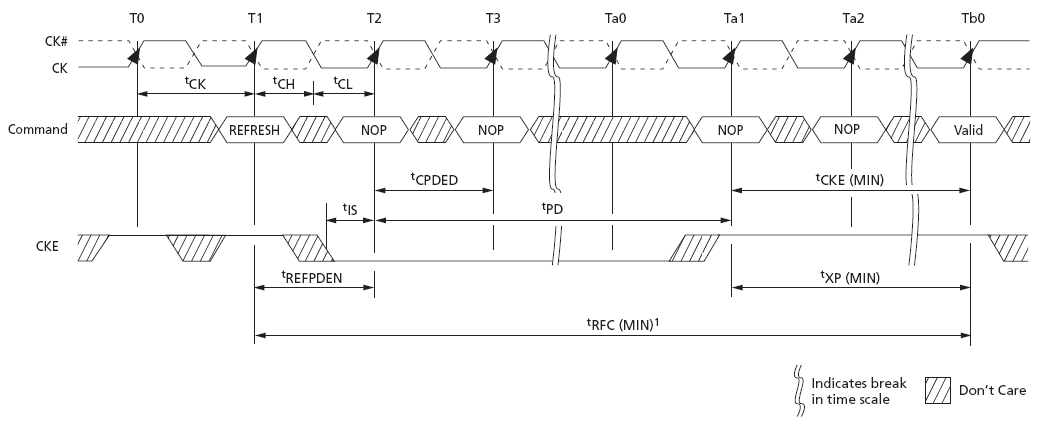

刷新操作(REFRESH)

DRAM 需要每隔一段时间执行一次刷新操作,以保证存储数据不丢失。刷新操作时,地址由内部刷新控制器自动产生。刷新操作时序如图 16 所示。

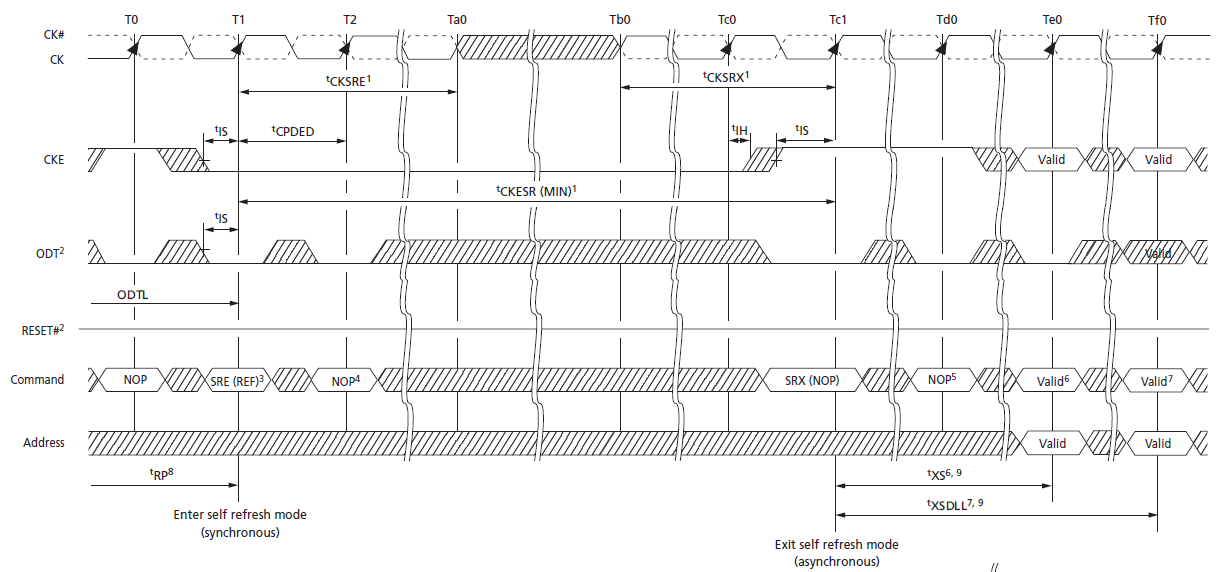

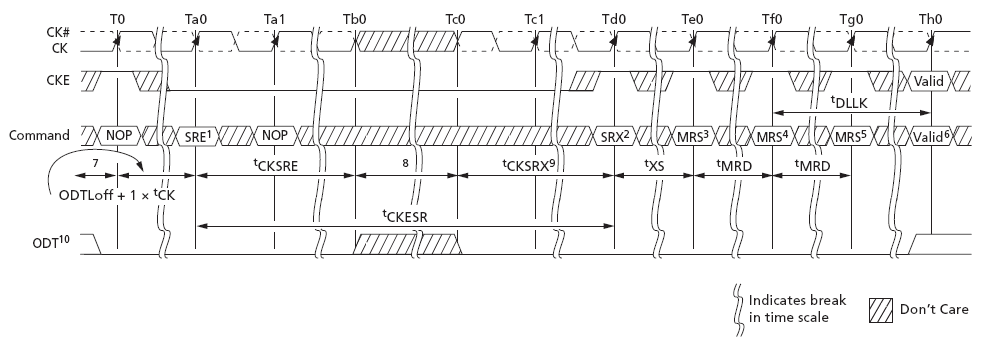

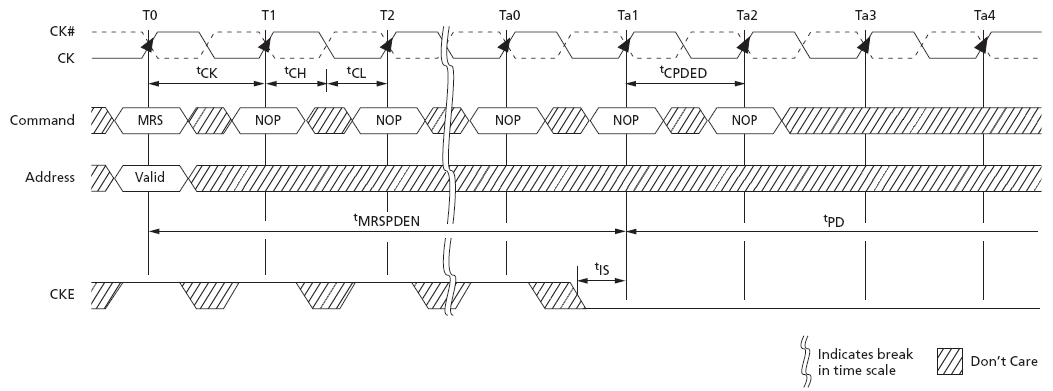

自刷新操作(SELF REFRESH)

自刷新操作也是用来刷新 DRAM 以保存所存储的数据。在自刷新方式下,为了降低功耗,刷新地址和刷新时间全部由器件内部产生。只有通过 CKE 变低才能激活自刷新方式,其他的任何输入都将不起作用。给出退出自刷新方式命令后必须保持一定节拍的空操作输入,以保证器件完成从自刷新方式的退出。如果在正常工作期间采用集中式自动刷新方式,则在退出自刷新模式后必须进行一遍集中的自动刷

新操作,以保证 DRAM 的数据不丢失。自刷新时序图如图 17 所示。

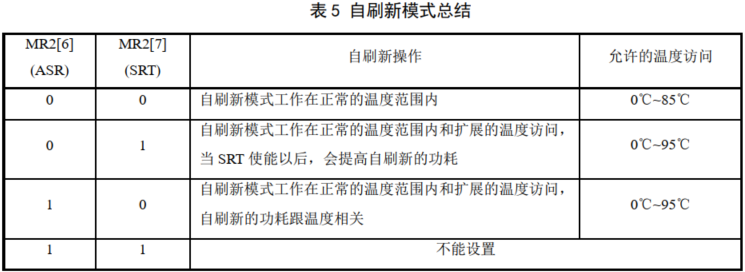

DDR3 SDRAM 采用了两项新的自刷新设计功能,称为自动自刷新( ASR,Automatic Self-Refresh)和自刷新温度范围(SRT, Self-Refresh Temperature)。当开始 ASR 之后,将通过一个内置于 DRAM 芯片的温度传感器来控制刷新的频率,因为刷新频率高的话,耗电就大,温度也随之升高,而温度传感器则在保证数据不丢失的情况下,尽量减少刷新频率,降低工作温度。自刷新温度范围(SRT, Self-Refresh Temperature)可通过模式寄存器选择两个温度范围,一个是普通的温度范围(例如0℃至 85℃),另一个是扩展温度范围,比如最高到 95℃。对于 DRAM 内部设定的这两种温度范围, DRAM 将以恒定的频率和电流进行刷新操作,其对应的设置和功

能说明见表 5。

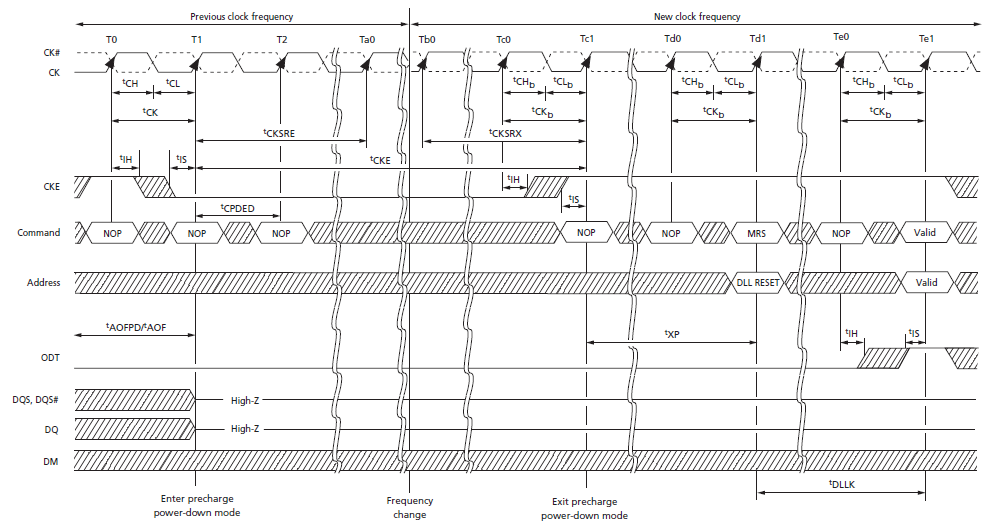

输入时钟频率改变

在 DDR3 初始化以后,外部时钟必须保持稳定,才能保证芯片正常工作。如果

需要改变外部输入的时钟频率,只有两种方式:自刷新模式或预充电 Power-down

模式。在自刷新模式下,外部时钟无意义,则可以在退出自刷新模式之前,改变输

入的时钟频率。而在预充电 Power-down 模式下, CKE 为低,同样外部时钟不使能,

则可以改变输入时钟频率,当在退出预充电 Power-down 模式以后,必须执行一次

MRS 命令,设置复位 DLL,如图 18 所示。

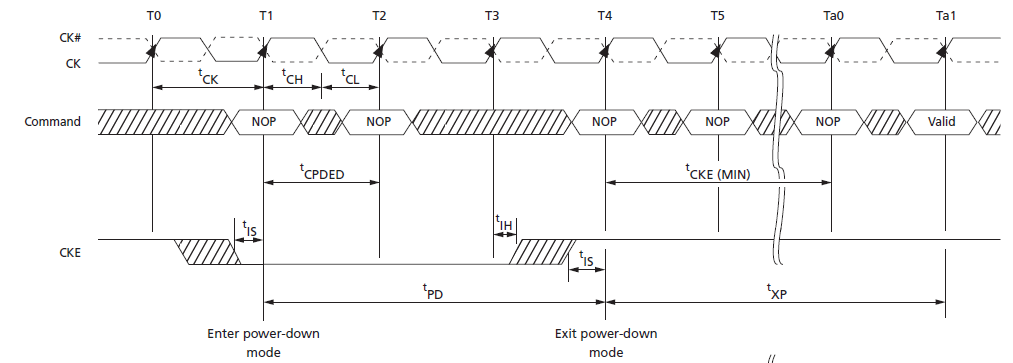

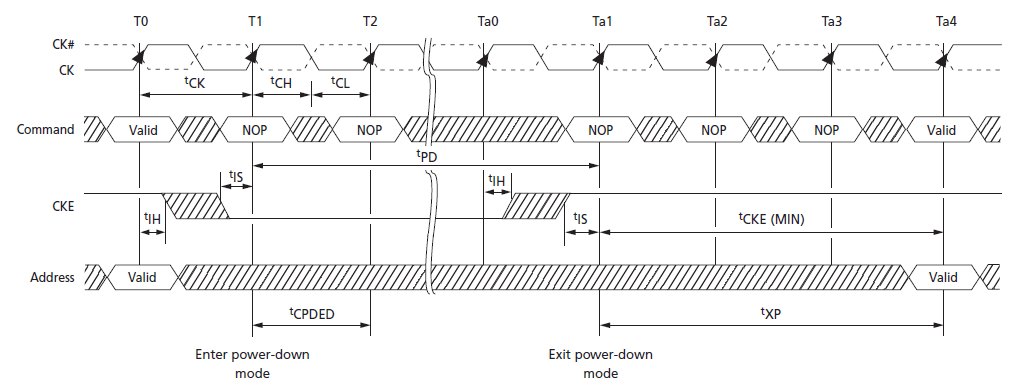

Power-Down模式

当 CKE 拉低后执行 NOP 或 DES 指令,芯片就进入 Power-down 模式。进入

Power-down 模式以后,芯片禁止所有的输入输出信号,包括 CK、 CK#、 ODT、 CKE

和 RESET#。

假如 Power-Down 模式发生的时候,所有 BANK 处于空闲状态,此时的

Power-Down 模式称为预充电 Power-Down,如图 19 所示;而当 Power-Down 模式发

生的时候,有任何 Row 激活在任意 BANK,此 Power-Down 模式称为激活

Power-Down,如图 20 所示。

复位操作

当外部复位管脚 RESET#拉低,保持 100ns 的时间,芯片就执行复位操作。在

此过程中,芯片输出禁止, ODT 关闭,芯片复位。当退出复位操作以后,芯片必须

重新初始化后才能工作,内部计数器也复位,而芯片内部数据也会变化。复位时序

图如图 21 所示。

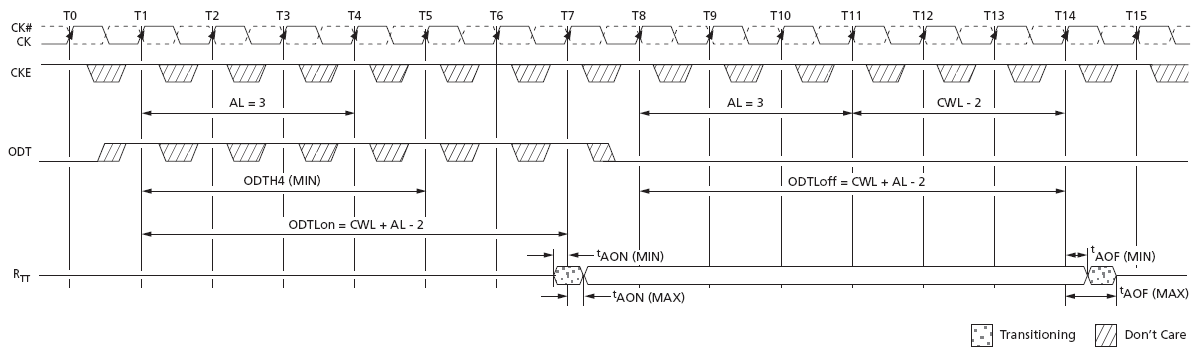

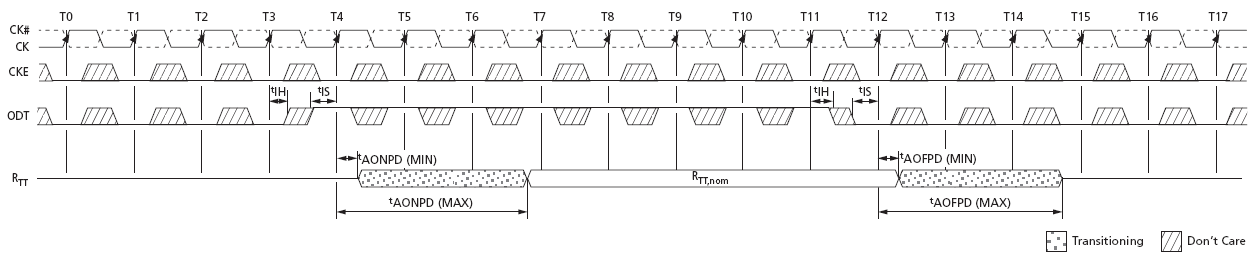

终端电阻(ODT)设置

DRAM 存储控制器利用终端电阻(ODT)功能打开或者关闭 DRAM 芯片某些

信号的终端电阻,包括 DQ、 DQS、 DM 信号,用来提高 DRAM 存储器的信号完整

性,其示意图如图 22 所示。

终端电阻 RTT 的电阻值在模式寄存器中进行设置。当芯片进入自刷新模式或者

在模式寄存器中将 ODT 功能禁止时,外部的 ODT 控制管脚就无意义。 ODT 包括普

通 ODT 模式和动态 ODT 模式,正常情况下 DRAM 都工作在普通 ODT 模式,此时

的 RTT 电阻值为 RTT.nom;当写入命令或者需要 ODT 功能转换的时候,就会用到

动态 ODT 模式,此时的电阻值变为 RTT.WR,当完成写入命令以后, RTT 值又回到

RTT.nom,如图 23 所示。

时序图

图 24 数据输出时序

图 25 数据输入时序

图 26 DQS 时序-读取操作

图 27 tFAW 时序

图 28 写入操作到读取操作时序序(BL8)

图 29 连续写入操作(BL8)

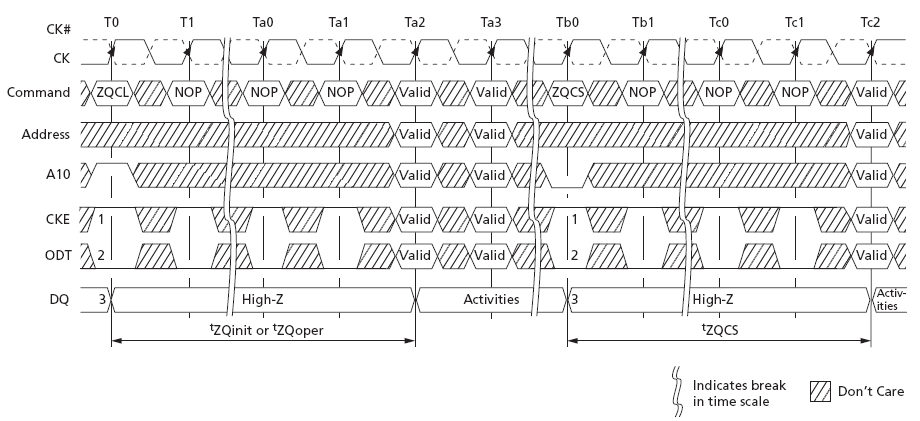

图 30 ZQ 校准时序((ZQCL and ZQCS)

图 31 DLL Disable 模式到 DLL enable 模式

图 32 读命令/读命令加预充电后进入 Power-Down 时序(RDAP)

图 33 写命令后进入 Power-Down 时序

图 34 写命令加自动预充电后进入 Power-Down 时序(WRAP)

图 35 刷新后进入 Power-Down 时序

图 36 激活后进入 Power-Down 时序

图 37 预充电后进入 Power-Down 时序

图 38 模式寄存器设置后进入 Power-Down 时序

图 39 同步 ODT 时序

图 40 异步 ODT 时序

图 41 动态 ODT 时序

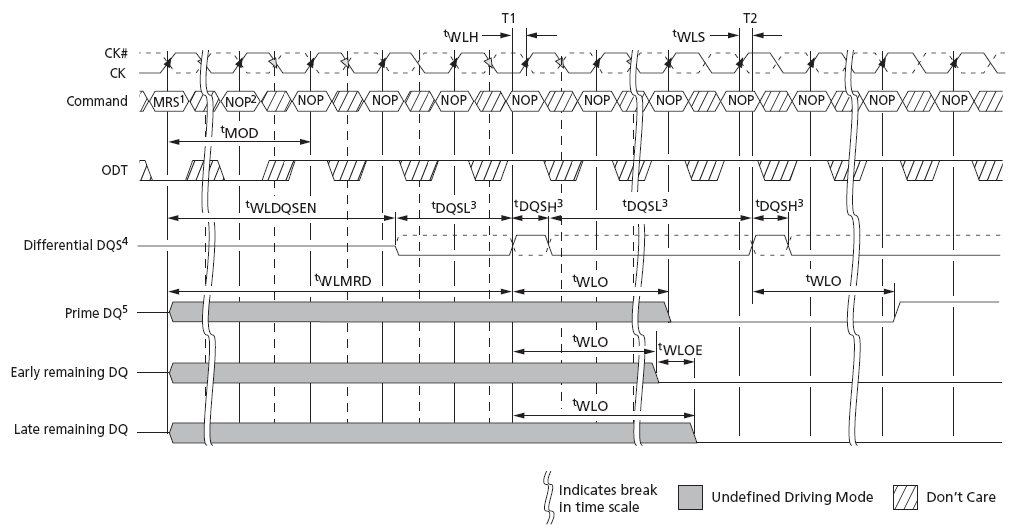

图 42 写入均衡时序