时钟周期约束(三)

文章目录

- 时钟周期约束(三)

- 时钟周期约束知识点速查表

-

- [1. 主时钟(Primary Clock)------"时间基准尺"](#1. 主时钟(Primary Clock)——“时间基准尺”)

- [2. 生成时钟(Generated Clock)------"派生时钟"](#2. 生成时钟(Generated Clock)——“派生时钟”)

- [3. 同一端口多时钟------"多模式"](#3. 同一端口多时钟——“多模式”)

- [4. 时钟特性调整------"微调尺"](#4. 时钟特性调整——“微调尺”)

- [5. 快速验收脚本](#5. 快速验收脚本)

时钟周期约束知识点速查表

1. 主时钟(Primary Clock)------"时间基准尺"

| 知识点 | 一句话要点 | 示例/Tcl |

|---|---|---|

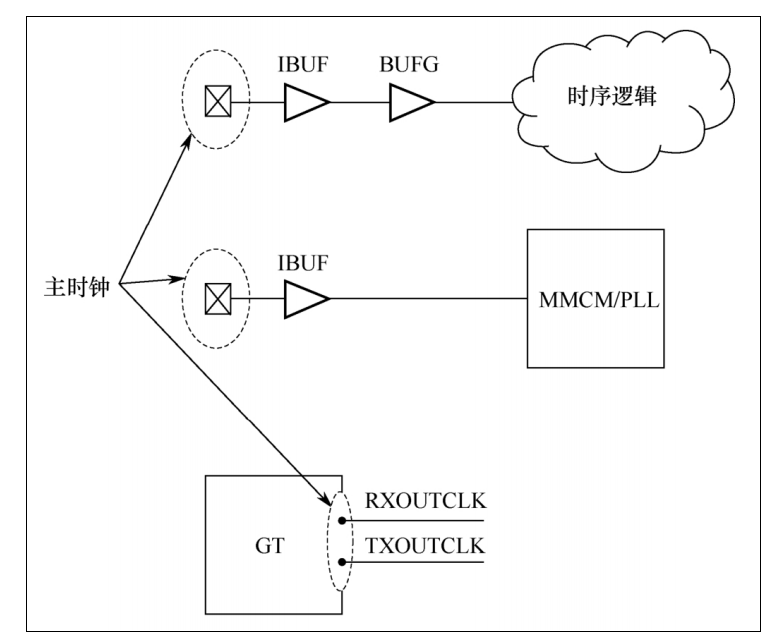

| 定义 | 进入 FPGA 的第一级时钟:引脚或 GT 输出(注意这个是GT输出,不是gt_ref_clk,也不是经过example中mmcm输出的log_phy,而是rx/txoutclk,这个是硬核GT输出的,可以理解为GT中有个晶振,来根据gt_ref_clk产生的rx/txoutclk,因此是主时钟) | create_clock -name clk200 -period 5 [get_ports clk_p] |

| 差分时钟 | 仅约束 P 端,N 端自动跟随 | [get_ports clk_p] 即可 |

| 三要素 | 源、周期、占空比 | -waveform {0 2.5} 可省,默认 50/50 |

| 抖动 | 输入不确定性 | set_input_jitter clk200 0.15 |

| 时钟组 | 异步场景先声明(默认都是同步时钟,需要进行时序分析,如果设置组了,相当于都FALSE了,一般情况不建议用组) | set_clock_groups -async -group clk200 -group clk125 |

- 命令get_ports决定了时钟源

- 在约束时,例如SRIO IP中GT的的 XDC 用 get_ports 只是"图省事、图通用",工具照样能把时钟约束透;换成 get_pins 也能用,但既麻烦又容易因为层级变动而失效,所以官方模板干脆统一写 get_ports。

- 有些IP中本身含有XDC,会进行时序约束,我们不必再约束一遍

2. 生成时钟(Generated Clock)------"派生时钟"

| 场景 | 命令关键选项 | 注意 |

|---|---|---|

| MMCM/PLL 自动输出 | 只需主时钟;工具自动推导 | report_clocks 看 A 属性 |

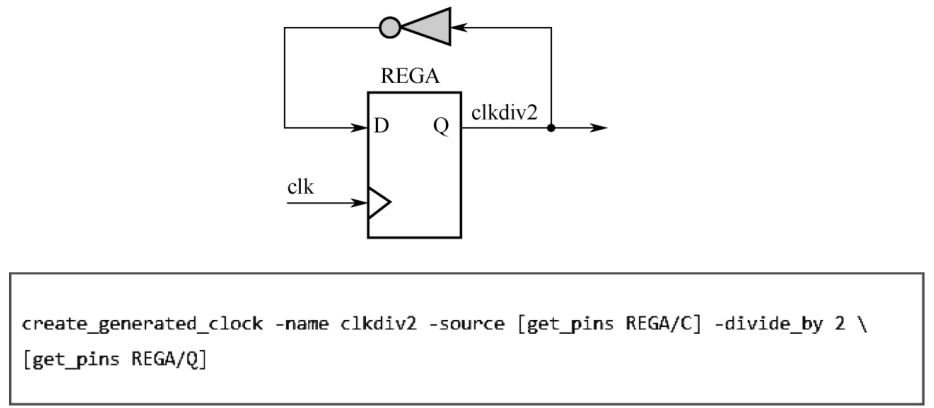

| 用户逻辑分频 | -divide_by N 或 -edges {1 3 5} |

-source 必须指向主时钟引脚(注意FF的C口指定为时钟源,如下图约束,Q指定为衍生时钟pins ))或单元 CLKPIN;另外,get_pins用于指定时钟源 |

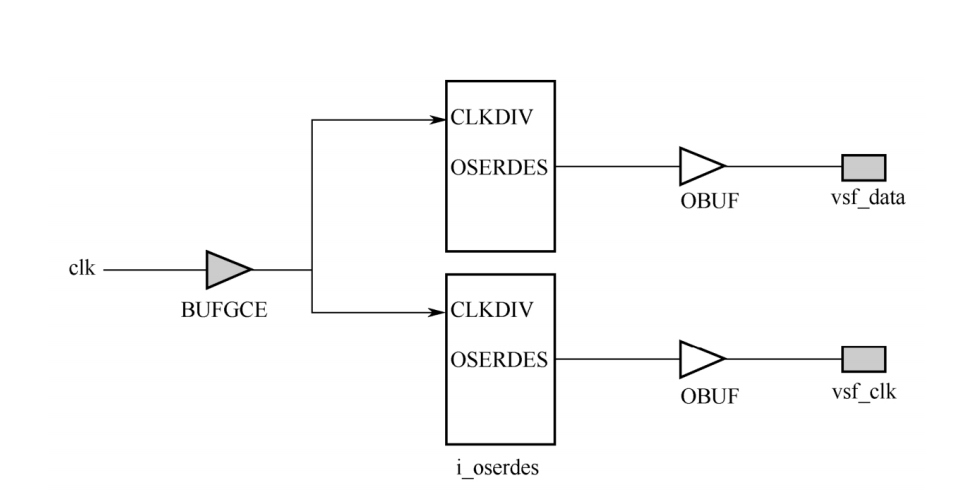

| 随路时钟 | OSERDES 输出 | -divide_by 1 并指定相同延迟路径 |

| 重命名自动时钟 | 用 create_generated_clock -name 覆盖原名称 |

仅对自动时钟有效,用户逻辑时钟不可重命名 |

| 维度 | 系统同步(System Synchronous) | 源同步(Source Synchronous) |

|---|---|---|

| 时钟来源 | 板级全局时钟(晶振→BUF→所有芯片) | 发送端 FPGA 随路输出时钟(与数据同方向) |

| 时钟数 | 1 个,全网共享 | 1 对/组,每方向独立 |

| 数据方向 | 单向或双向 | 通常单向,高速双向用两套随路时钟 |

| 最高频率 | 一般 ≤ 200 MHz(FR4 走线极限) | 轻松 400 MHz+(DDR 可 800 Mbps) |

| 举例 | SPI、I²C、传统 SRAM、MCU 并口 | DDR、SDR SDRAM、Camera LVDS、GMII RGMII |

源同步设计中的随路时钟,。随路时钟是指与数据同时生成的时钟,且同时给到接收端,以生成该数据在接收端的采样时钟。在源同步设计中,为了确保输出数据与输出时钟(随路时钟)具有相同的延迟,通常让二者经过同样的电路单元(如这里的OSERDES)后再输出。

3. 同一端口多时钟------"多模式"

| 目的 | 命令片段 | 解释 |

|---|---|---|

| 双模式测试 | create_clock -name clk_slow -period 10 [get_ports clk] create_clock -name clk_fast -period 6.667 [get_ports clk] -add |

第二句必须 -add |

| 互斥存在 | set_clock_groups -physically_exclusive -group clk_slow -group clk_fast |

告诉工具不会同时出现 |

| 含生成时钟 | 同上再加 -include_generated_clocks |

防止子时钟仍被分析 |

4. 时钟特性调整------"微调尺"

| 参数 | 命令 | 应用示例 |

|---|---|---|

| 输入抖动 | set_input_jitter <clock> <value> |

0.1~0.2 ns 常见 |

| 额外不确定性 | set_clock_uncertainty -setup 0.5 [get_clocks clk200] |

轻度过约束,增时序预算 |

| 双向不确定 | -from A -to B 可不对称 |

跨时钟域单独加压 |

5. 快速验收脚本

tcl

# 1. 查遗漏

report_clock_networks -name clk_overview

# 2. 查自动/生成时钟属性

report_clocks

# 3. 查时钟组/交互

report_clock_interaction

# 4. 查不确定量

report_timing -setup -max_paths 1 -input_pins