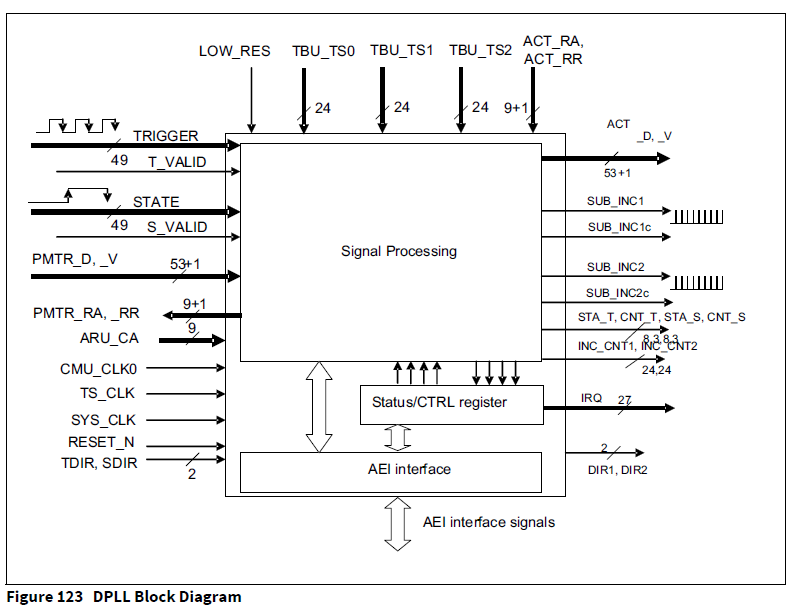

1、主要框图

2、主要信号说明

以下对各信号简单说明

注意TIM1 CH0使用的是TIEM****测量模式

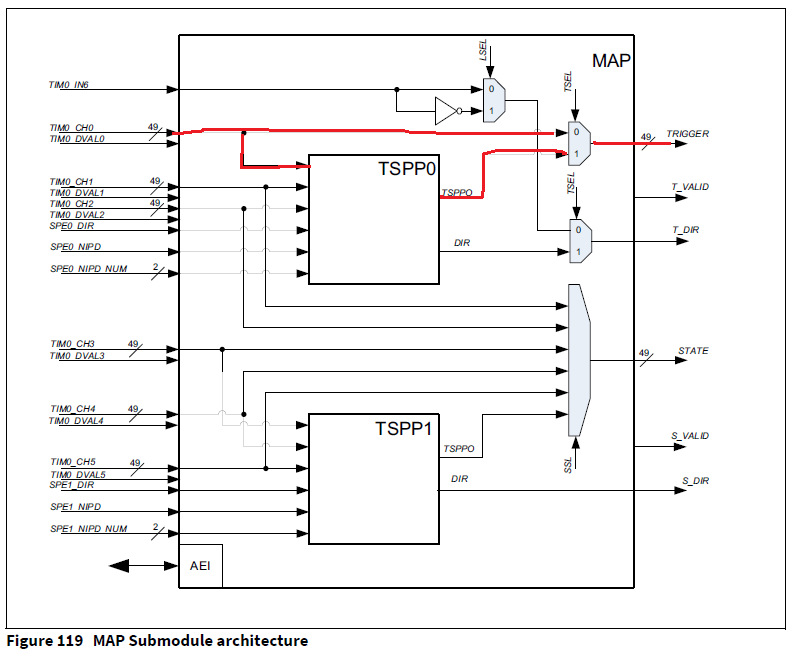

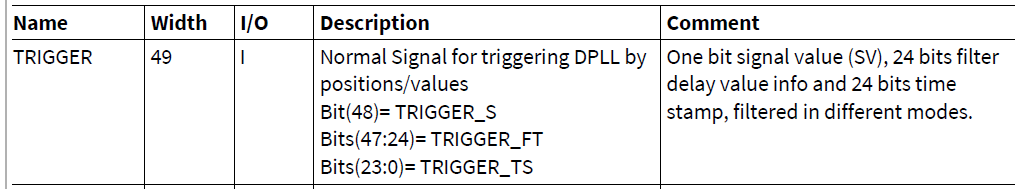

2.1、TRIGGER(49bit)

来自TIM0_CH0或来自TSPP0处理TIM0_CH0后的信号TSPPO。本文只讨论来自TIM0_CH0的信号。

其中

bit0~bit23是时基,链接到ARU_OUT(23:0),即TBU_TS0存到GPR0;

bit47~bit24是时基,链接到ARU_OUT(47:24),即TBU_TS0存到GPR1;

bit49是信号值,链接到ARU_OUT(48),即TIM0 CH0采集的信号是上升沿还是下降沿。当也原始信号出现上升沿时,整个ECNT计数器值总是奇数,而当也原始信号出现下降沿时,它总是偶数,可以通过判断ECNT寄存器的bit0(即ARU_OUT(48))判断是上升沿还是下降沿。

总结:TRIGGER代表测量的来自TIM0_IN0(原始的信号)经过滤波等处理后TIM0_OUT0的信号。其中bit48代表上升沿(0)还是下降沿(1),bit47~24代表TBU_TS0,bit23~0代表TBU_TS0。

2.2、T_VALID

TRIGGER值的有效性,未理解含义,未理解实际怎么使用。

2.3、STATE

类似于TRIGGER,STATE代表测量的来自TIM0_IN1(原始的信号)经过滤波等处理后TIM0_OUT1的信号。

2.4、S_VALID

STATE值的有效性,未理解含义,未理解实际怎么使用。

2.5、PMTR_D

3、主要功能

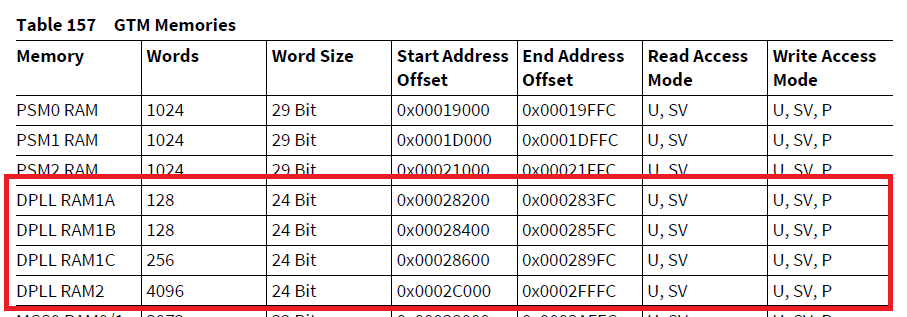

3.1、DPLL RAM

DPLL模块自带RAM模块,各子功能RAM的地址和大小如下图。主要有RAM1A,RAM1B,RAM1C,RAM2四块RAN区域。

注意:以下地址为相对地址。

以下为GTM模块的地址0xF0100000u。举例DPLL_RAM2的绝对地址是:

0xF0100000u+0x0002C000 = 0xF012C000

4、主要寄存器

4.1、TIM0 CH0主要寄存器

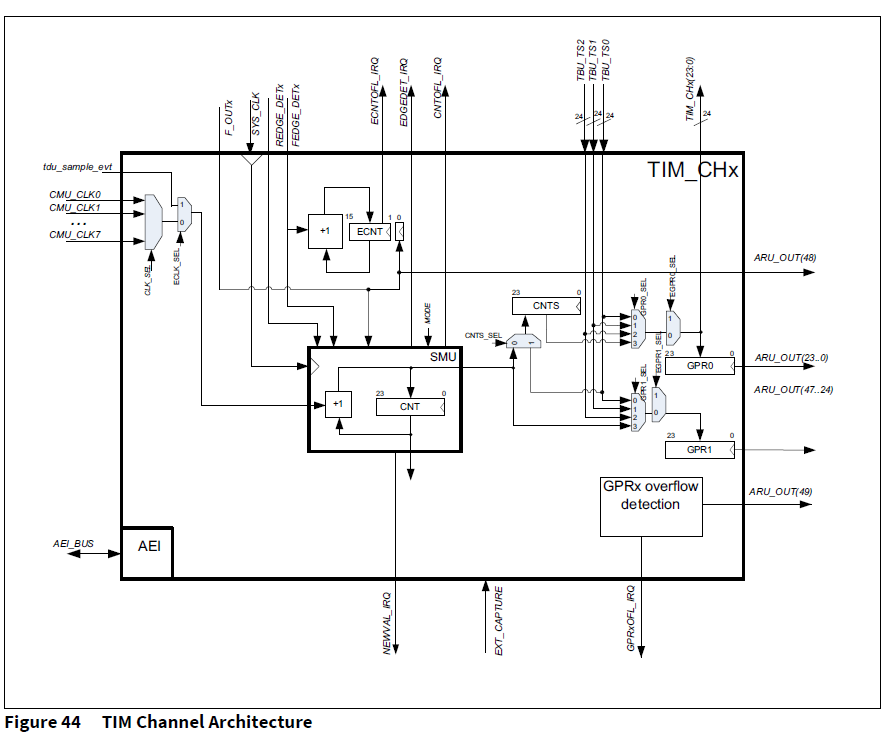

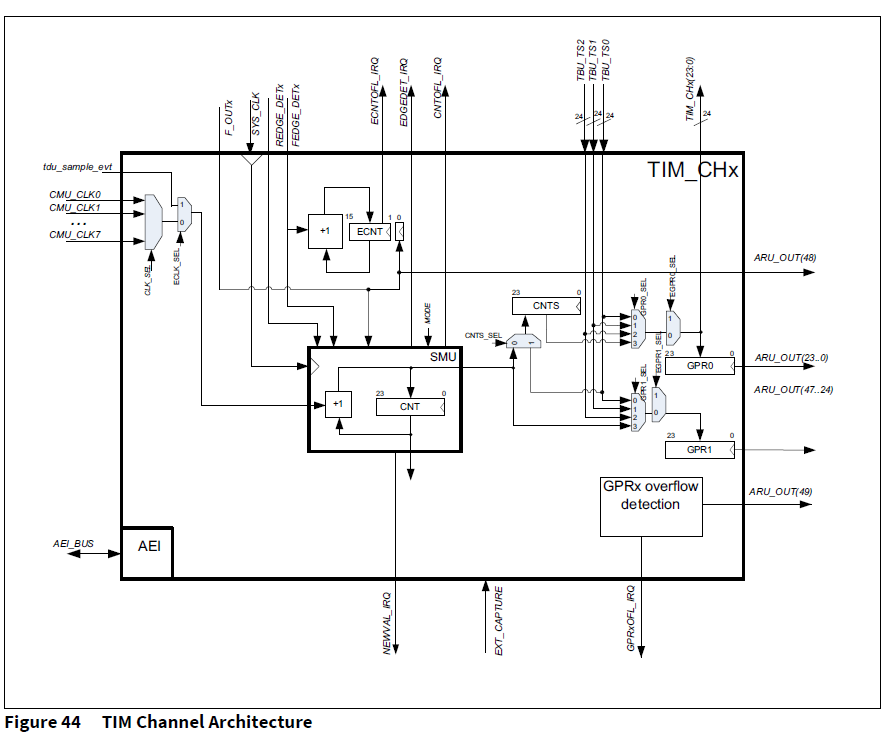

主要基于下图涉及的寄存器讲解

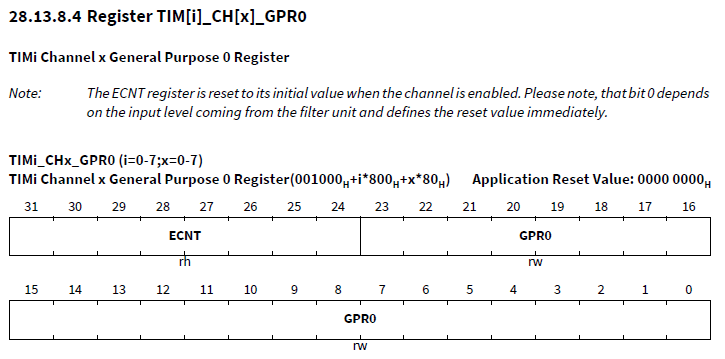

4.1.1、GPR0寄存器

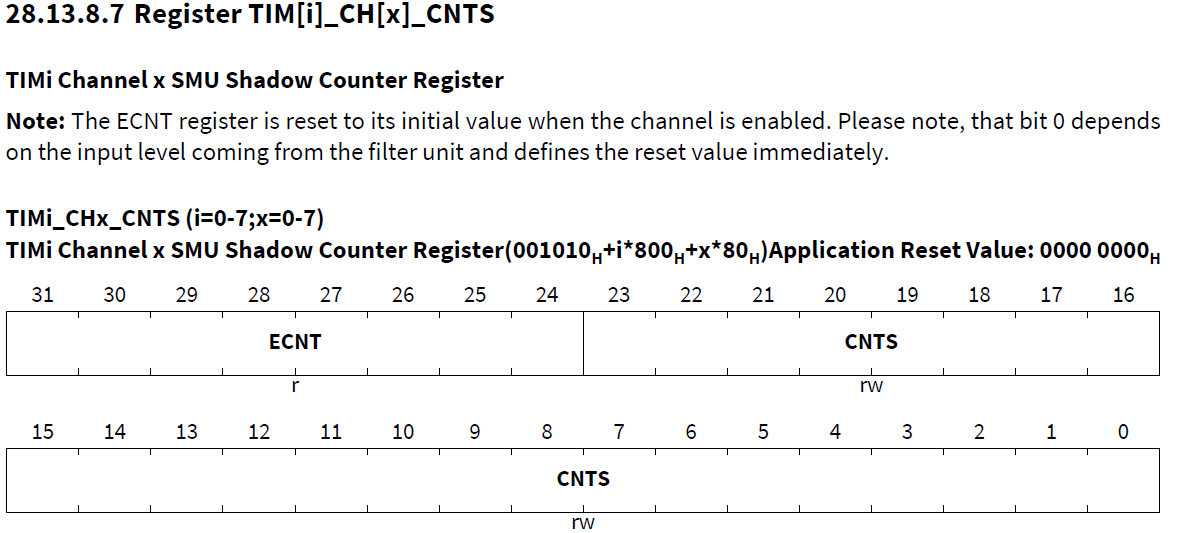

包含了8bit的ECNT边沿检测和24bit的GPR0寄存器。

8bit ECNT只读,为奇数时表示上升沿,偶数时表示下降沿;

24bit GPR0寄存器的值可以来源于以下4种可能:

24bit CNTS寄存器(影子寄存器);

24bit TBU_TS0;

24bit TBU_TS1;

24bit TBU_TS2;

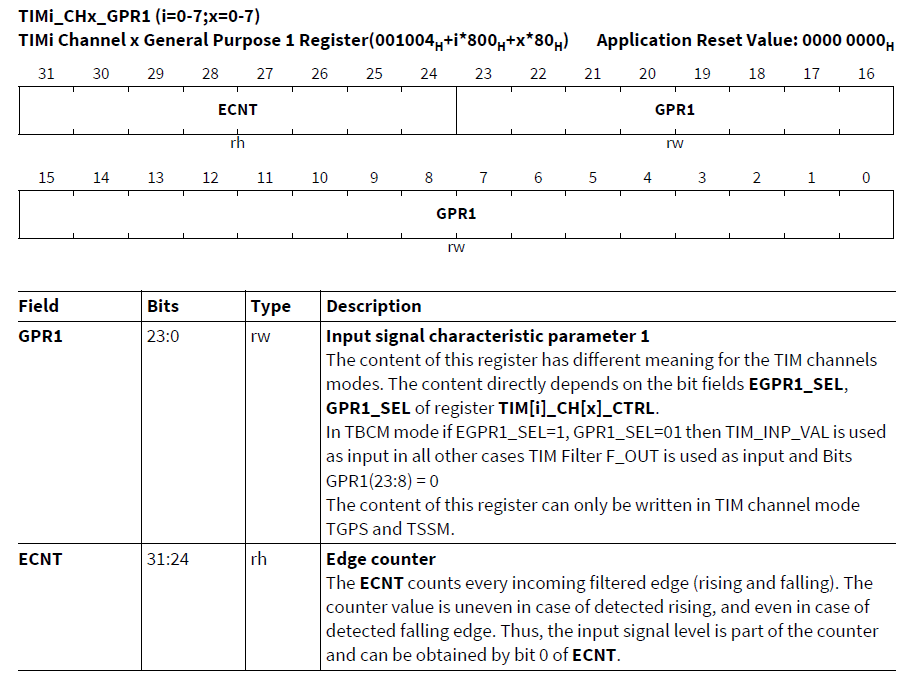

4.1.2、GPR1寄存器

包含了8bit的ECNT边沿检测和24bit的GPR1寄存器。

8bit ECNT只读,为奇数时表示上升沿,偶数时表示下降沿;

24bit GPR1寄存器的值可以来源于以下4种可能:

24bit SMU的CNT寄存器;

24bit TBU_TS0;

24bit TBU_TS1;

24bit TBU_TS2;

4.1.3、CNTS寄存器

包含了8bit的ECNT寄存器、24bit的CNTS影子寄存器

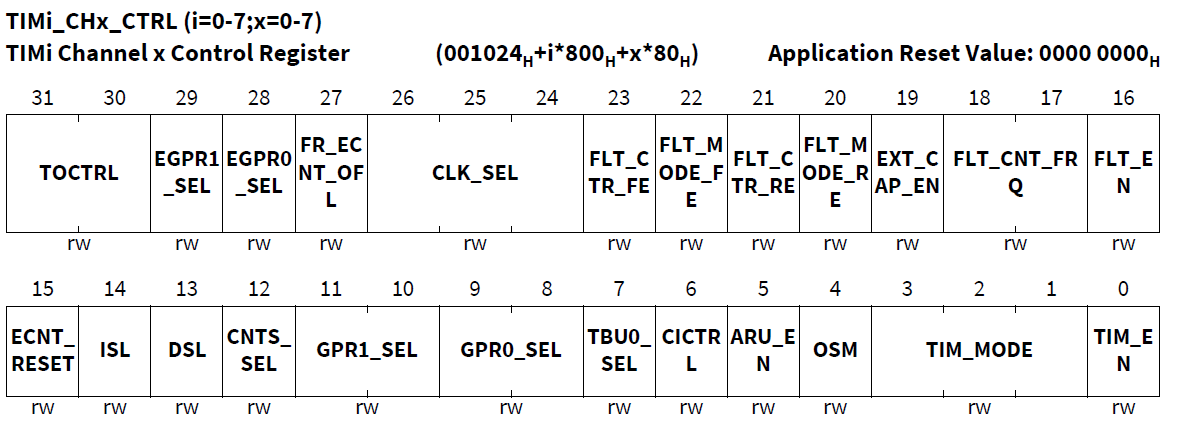

4.1.4、控制寄存器

**bit0:**TIM_EN,TIM channel x enable,通道使能

**bit1~bit3:**TIM_MODE,TIM channel x mode,通道模式,有6种模式,TPWM、TPIM、TIEM、TIPM、TBCM、TGPS和TSSM。

**bit4:**OSM,One-shot mode,连续采集模式还是一次采集模式

**bit5:**ARU_EN,GPR0 and GPR1 register values routed to ARU,GPR0和GPR1寄存器是否通过ARU传输

**bit6:**CICTRL,通道输入使用本通道还是上一个通道

**bit7:**TBU0_SEL,使用TBU_TS0(共27bit)的高24bit还是低24bit存储GPR0和GPR1寄存器的值

**bit8~bit9:**GPR0_SEL,选择GPR0来源。

来源可以是:

TBU_TS0(24bit)+ ECNT(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

TBU_TS1(24bit)+ TIM_INP_VAL(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

TBU_TS2(24bit)+ 预留(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

CNTS寄存器(24bit)+ 预留(8bit)组成32bit GPR0寄存器。使用EGPR0_SEL控制是否接到GPR0寄存器(EGPR0_SEL=0表示接,EGPR0_SEL=1表示断开)

**bit10~11:**GPR1_SEL,选择GPR1来源。

来源可以是:

TBU_TS0(24bit)+ ECNT(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

TBU_TS1(24bit)+ TIM_INP_VAL(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

TBU_TS2(24bit)+ 预留(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

SMU的CNT寄存器(24bit)+ 预留(8bit)组成32bit GPR1寄存器。使用EGPR1_SEL控制是否接到GPR1寄存器(EGPR1_SEL=0表示接,EGPR1_SEL=1表示断开)

**bit12:**CNTS_SEL,选择影子寄存器CNTS。可来源于:TBU_TS0或SMU的CNT寄存器

bit13:DSL,测量上升沿或下降沿选择(仅当ISL位为=0时设置有效)

**bit14:**ISL,TIEM模式下选择双沿还是上升沿或下降沿。如为0B,单沿采集(上升还是下降沿由DSL决定);如为1B,双沿采集,此时忽略DSL的设置。

**bit15:**ECNT_RESET,如为0B,ECNT工作在循环模式;如为1B,ECNT周期采样reset

**bit16:**FLT_EN,滤波使能或禁止

**bit17~bit18:**FLT_CNT_FRQ滤波计数器时钟选择,可以是CLK0/1/6/7

**bit19:**EXT_CAP_EN,外部捕获使能或禁止

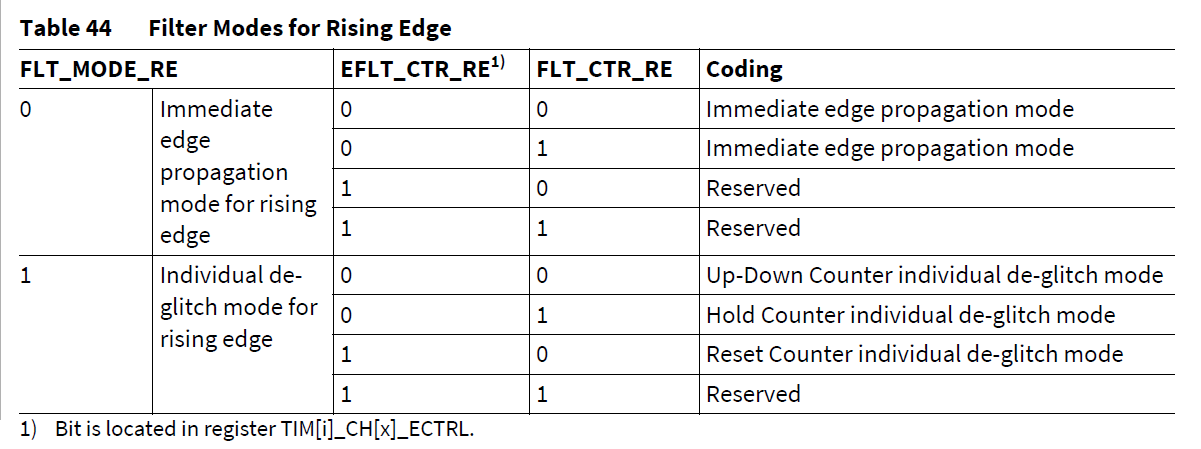

**bit20:**FLT_MODE_RE,上升沿滤波模式

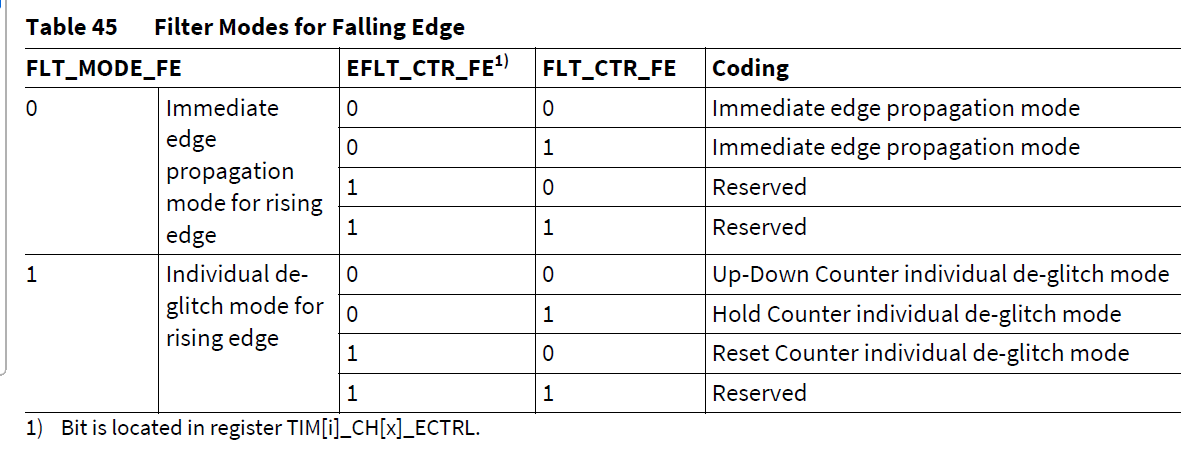

**bit21:**FLT_CTR_RE,上升沿滤波计数器模式

**bit22:**FLT_MODE_FE,下降沿滤波模式

**bit23:**FLT_CTR_FE,下降沿滤波计数器模式

**bit24~bit26:**CLK_SEL,时钟选择,可以是CMU模块的CLK0~CLK7之一

bit27:FR_ECNT_OFL,是否扩展边沿寄存器(如8bit或16bit)

bit28:EGPR0_SEL,见GPR0_SEL

'bit29:EGPR1_SEL,见GPR1_SEL

bit30~bit31:TOCTRL,超时控制。

4.2、DPLL主要寄存器

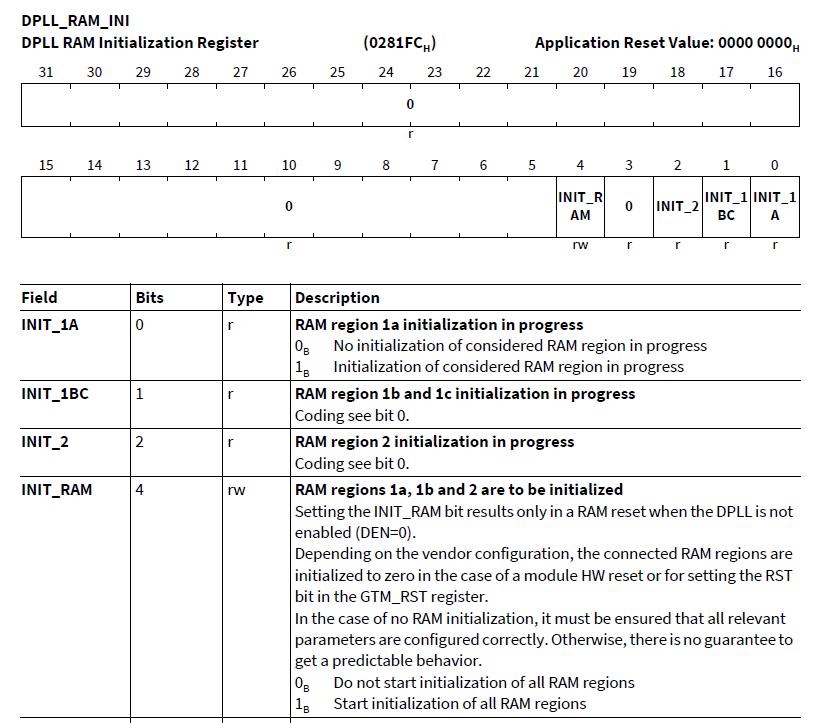

4.2.1、DPLL_RAM_INI

**bit0:**INIT_1A,只读位,指示RAM1A区域初始化是否在运行

**bit1:**INIT_1BC,只读位,指示RAM1B和RAM1C区域初始化是否在运行

**bit2:**INIT_2,只读位,指示RAM2区域初始化是否在运行

**bit3:**INIT_RAM,启动所有DPLL RAM区域的初始化

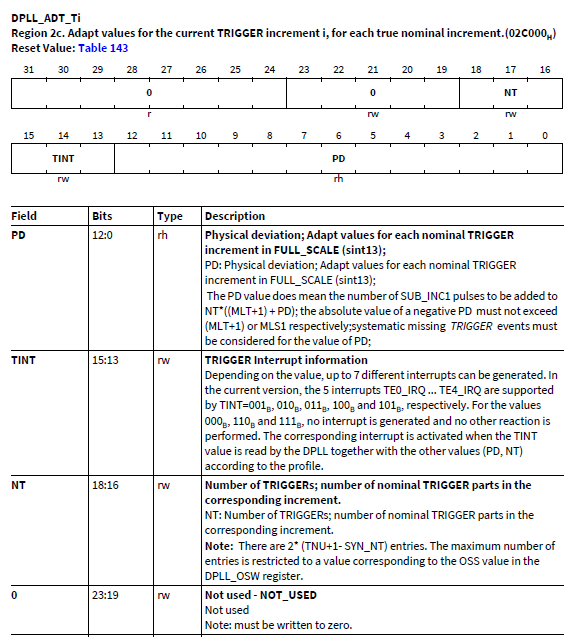

4.2.2、DPLL_ADT_Ti

bit0~bit12:只读位,

bit13~bit15:

bit16~bit18:

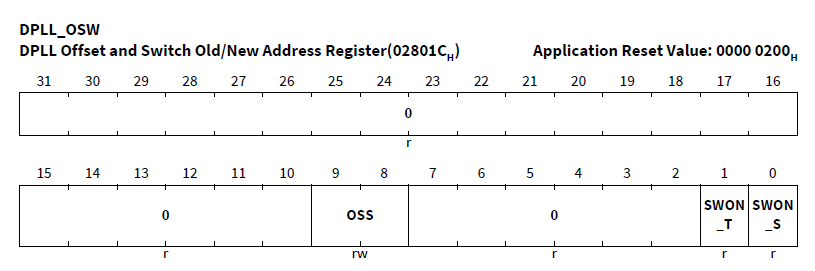

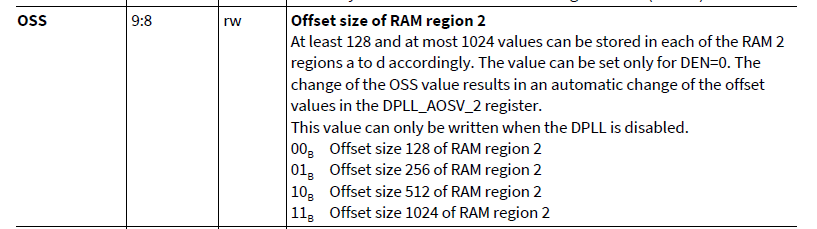

4.2.3、DPLL_OSW

bit9~bit8:OSS,RAM的偏移大小。

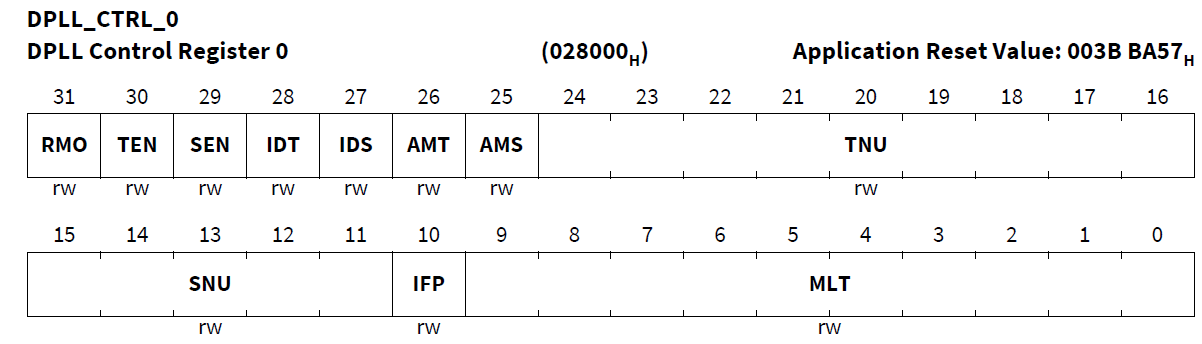

4.2.4、控制寄存器0

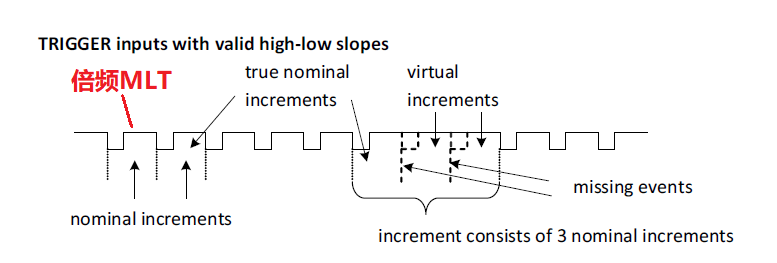

**bit0~9:**MLT,TRIGGER信号的乘数,即倍频。在两个正常TRIGGER事件(如两个曲轴转速信号的正常齿的下降沿之间)。如MLT设置为599,那么两个正常齿的下降沿之间被分了599+1=600份。

bit10:

bit11~bit15:

**bit16~bit24:**TNU,TRIGGER数量,正常齿和缺齿(要虚拟补齐为正常齿事件的数量)的TRIGGER事件总和。如60-2曲轴的TRIGGER数量是60(58正常齿事件和一个缺齿(虚拟补齐为2个正常齿事件))。如TNU设为59,那么TRIGGER数量为59+1=60。

bit25:

bit26:

bit27:

bit28:

bit29:

**bit30:**TEN,TRIGGER使能或禁止

bit31:

4.2.5、控制寄存器1

5、代码示例

主要实现曲轴信号的输入解析及ATOM的时序控制

5.1、TIM0 CH0处理

5.1.1、TIM0 CH0初始化

非关键参数见在TIM模块的博客里详见,此处不展开。

主要功能:

1)以TEIM方式测量输入。

2)打开边沿检测中断和新值中断。

3)检测双边沿(上升沿和下降沿)

4)TBU_TS0分别存入GPR0和GPR1寄存器。GPR0会通过ARU(23:0)传输到MAP和DPLL模块,GPR1会通过ARU(47:24)传输到MAP和DPLL模块。

cs

IfxGtm_Tim_Timer TIM_Timer_Tim0CH0;

IfxGtm_Tim_In TIM_IN_Tim0CH0;

/* TIM0 channel0. */

void Init_Tim0_0(void)

{

IfxGtm_enable(&MODULE_GTM); /* 使能GTM模块. */

IfxGtm_Cmu_enableClocks(&MODULE_GTM, IFXGTM_CMU_CLKEN_CLK0); /* 使能CLK0时钟. */

IfxGtm_Tim_In_Config configTIM_IN; /* 定义结构体变量 */

IfxGtm_Tim_In_initConfig(&configTIM_IN, &MODULE_GTM);

/* 装载默认值到configTIM_IN结构体. */

configTIM_IN.timIndex = IfxGtm_Tim_0; /* 设为TIM0 */

configTIM_IN.channelIndex = IfxGtm_Tim_Ch_0; /* 设为CH0*/

/* 以下不涉及,不关心,使用默认值即可 */

// configTIM_IN.irqMode = IfxGtm_IrqMode_pulseNotify;

// configTIM_IN.isrPriority = IfxSrc_Tos_cpu3;

// configTIM_IN.isrPriority = 0;

// configTIM_IN.capture.irqOnNewVal = FALSE;

// configTIM_IN.capture.irqOnCntOverflow = FALSE;

// configTIM_IN.capture.irqOnEcntOverflow = FALSE;

// configTIM_IN.capture.irqOnDatalost = FALSE;

// configTIM_IN.capture.clock = IfxGtm_Cmu_Clk_0;

// configTIM_IN.capture.mode = Ifx_Pwm_Mode_leftAligned;

// configTIM_IN.capture.gateCount = 0;

// configTIM_IN.capture.activeEdge = IfxGtm_Tim_In_ActiveEdge_falling;

/* 超时不关心 */

configTIM_IN.timeout.clock = IfxGtm_Cmu_Clk_0;

configTIM_IN.timeout.irqOnTimeout = FALSE;

configTIM_IN.timeout.timeout = 0.0;

configTIM_IN.filter.inputPin = &IfxGtm_TIM0_0_P02_0_IN; /* 选择输入port . */

/* 滤波不关心,可根据实际配置,使用默认值即可 */

// configTIM_IN.filter.input = IfxGtm_Tim_In_Input_currentChannel;

// configTIM_IN.filter.inputPinMode = IfxPort_InputMode_pullDown;

/* Select input port pin mode. */

// configTIM_IN.filter.risingEdgeMode =

IfxGtm_Tim_In_ConfigFilterMode_individualDeglitchTimeUpDown;

// configTIM_IN.filter.fallingEdgeMode =

IfxGtm_Tim_In_ConfigFilterMode_individualDeglitchTimeUpDown;

// configTIM_IN.filter.risingEdgeFilterTime = 0;

// configTIM_IN.filter.fallingEdgeFilterTime = 0;

// configTIM_IN.filter.clock = IfxGtm_Cmu_Tim_Filter_Clk_0;

// configTIM_IN.filter.irqOnGlitch = FALSE;

IfxGtm_Tim_In_init(&TIM_IN_Tim0CH0, &configTIM_IN); /* 初始化以上配置. */

IfxGtm_Tim_Timer_Config configTIM_Timer; /* 定义结构体变量 */

IfxGtm_Tim_Timer_initChannelConfig(&configTIM_Timer, &MODULE_GTM);

/* 装载默认值到configTIM_Timer结构体. */

configTIM_Timer.timIndex = IfxGtm_Tim_0; /* 设置为TIM0 */

configTIM_Timer.channel = IfxGtm_Tim_Ch_0; /* 设置为CH0 */

configTIM_Timer.channelControl.enable = TRUE; /* 使能通道 */

configTIM_Timer.channelControl.mode = IfxGtm_Tim_Mode_inputEvent;

/* 设为TIEM测量模式 */

configTIM_Timer.channelControl.enableOneShotMode = FALSE; /* 关闭依次测量模式 */

configTIM_Timer.channelControl.enableAruRouting = TRUE;

/* 使能ARU路由功能后才能将TIM0_CH0(49bit)路由到MAP模块和DPLL模块*/

configTIM_Timer.channelControl.channelInputControl = FALSE;

/* FALSE表示本通道(即TIM0_CH0)作为输入;TURE表示上一个通道(即TIM0_CH7)作为输入*/

configTIM_Timer.channelControl.gpr0Sel = IfxGtm_Tim_GprSel_tbuTs0;

/* TBU_TS0(24bit时基)存入到GPR0(24bit)里 */

configTIM_Timer.channelControl.gpr1Sel = IfxGtm_Tim_GprSel_tbuTs0;

/* TBU_TS0(24bit时基)存入到GPR1(24bit)里 */

configTIM_Timer.channelControl.cntsSel = IfxGtm_Tim_CntsSel_cntReg;

/* CNTS来自CNT寄存器 */

configTIM_Timer.channelControl.signalLevelControl = FALSE;

/* DSL 0:falling edge;1:rising edge. 表示的是以上升沿还是下降沿测量 */

configTIM_Timer.channelControl.ignoreSignalLevel = TRUE;

/* ISL:0:由DSL决定;1:双沿.表示以单沿测量(上升还是下降由DSL决定)还是双沿测量 */

configTIM_Timer.channelControl.enableCounterReset = FALSE; /* 测量计数器循环归零 */

configTIM_Timer.channelControl.enableFilter = TRUE; /* 使能滤波 */

configTIM_Timer.channelControl.filterCounterFrequency =

IfxGtm_Tim_FilterCounterFreqSel_cmuClk0; /* 设置滤波时钟 */

configTIM_Timer.channelControl.enableExternalCaptureMode = FALSE;

/* 关闭外部捕获模式*/

configTIM_Timer.channelControl.filterModeRisingEdge =

IfxGtm_Tim_FilterMode_individualDeglitchTime; /* 设置上升沿滤波模式 */

configTIM_Timer.channelControl.filterCounterModeRisingEdge =

IfxGtm_Tim_FilterCounter_hold; /* 设置上升沿滤波模式 */

configTIM_Timer.channelControl.filterModeFallingEdge =

IfxGtm_Tim_FilterMode_individualDeglitchTime; /* 设置下降沿滤波模式 */

configTIM_Timer.channelControl.filterCounterModeFallingEdge =

IfxGtm_Tim_FilterCounter_hold; /* 设置下降沿滤波模式 */

configTIM_Timer.channelControl.clkSel = IfxGtm_Cmu_Clk_0; /* 选择通道时钟为clk0 */

configTIM_Timer.channelControl.extendEdgeCounterOverflow = FALSE;

/* 边沿检测计数器(ECNT)的位数,FALSE:8bit,TURE:16bit */

configTIM_Timer.channelControl.egpr0Sel = FALSE; /* 看上图Figure44容易理解,表示连接 */

configTIM_Timer.channelControl.egpr1Sel = FALSE; /* 看上图Figure44容易理解,表示连接 */

configTIM_Timer.channelControl.timeoutControl = IfxGtm_Tim_Timeout_disabled;

/* 超时关闭 */

configTIM_Timer.raisingEdgeFilterTime = 0; /* 上升沿滤波时间 */

configTIM_Timer.fallingEdgeFilterTime = 0; /* 下降沿滤波时间 */

configTIM_Timer.shadowCounter = 0; /* 影子计数器初始值 */

configTIM_Timer.irqEnable = 1; /* 使能中断 */

configTIM_Timer.irqMode = IfxGtm_IrqMode_pulseNotify;

/* 中断模式为脉冲模式,即检测到上升沿或下降沿都发生中断 */

configTIM_Timer.irqType = IfxGtm_Tim_IrqType_newVal;

/* 中断类型:SMU信号测量单元发生新值就中断 */

/* 不涉及 */

configTIM_Timer.inputSourceSelect.mode = 0;

configTIM_Timer.inputSourceSelect.value = 0;

configTIM_Timer.enableAuxInputSourceSelect = FALSE;

IfxGtm_Tim_Timer_initChannel(&TIM_Timer_Tim0CH0, &configTIM_Timer);

/* 将上面的值写入TIM0 CH0 . */

/* 在CPU0里以优先级180运行中断 */

IfxSrc_init(&MODULE_SRC.GTM_TIM[0][0], IfxSrc_Tos_cpu0, 180);

IfxSrc_enable(&MODULE_SRC.GTM_TIM[0][0]);

}TIM0_CH0初始化后将根据实际信号有以下动作:

1)产生TIM0_CH0(49)的信号,此信号bit49保存的是上升沿(0)还是下降沿(1);高或低24bit保存的是TBU_TS0的计数值;

2)当实际硬线信号有上升沿或下降沿都产生中断

3)当SMU信号处理单元有新值发生时发生中断。

基于以上,就可以做如下功能:

在上升沿或下降沿中断里判断TIM0_CH0(49)的bit9来进一步确定是上升沿还是下降沿。具体如何处理见3.1.2章节

5.1.2、TIM0 CH0中断处理

主要实现找到缺齿、并与DPLL同步。同步后关闭TIM0 CH0的中断,之后就将TIM0_CH0(49bit)通过ARU传递到MAP和DPLL处理。

cs

/* enumeration DPLL synchronous state */

typedef enum

{

DPLL_CRS_noSync = 0,

DPLL_CRS_Sync = 1,

DPLL_CRS_WaitSync = 2,

DPLL_CRS_LossSync = 3,

} DPLL_SyncState;

DPLL_SyncState DPLL_CRS_SyncState;

IFX_INTERRUPT(TIM0_CH0_CrkSync, 0, 180);/*在CPU0以中断优先级180处理TIM0_CH0_CrkSync功能*/

/* synchronize crank input from TIM0 channel 0 to DPLL. */

void TIM0_CH0_CrkSync(void)

{

static uint32 TIM0_CH0_GPR0_Value; /* 定义TIM0 channel0 GPR0寄存器静态变量. */

static uint32 TIM0_CH0_OldTs = 0; /* 定义TIM0_CH0_OldTs静态变量 . */

static uint32 TIM0_CH0_NewTs = 0; /* 定义TIM0_CH0_NewTs 静态变量 . */

static uint32 TIM0_CH0_OldDiff = 0; /* 定义TIM0_CH0_OldDiff静态变量 . */

static uint32 TIM0_CH0_NewDiff = 0; /* 定义TIM0_CH0_NewDiff静态变量 . */

IfxGtm_Tim_Ch_clearNewValueEvent(&MODULE_GTM.TIM[0].CH0);

/* 清除中断通知状态位,为下一次再次进入中断清除. */

TIM0_CH0_GPR0_Value = MODULE_GTM.TIM[0].CH0.GPR0.U;

/* 获得TIM0 channel0 GRP0寄存器值想,可参考4.1.1章节,此寄存器包含24bit的GPR0和8bit的ECNT. */

/* tooth starts with falling edge. */

if ((TIM0_CH0_GPR0_Value & 0x01000000) == 0) /* 检测到下降沿,即检测bit24(ECNT的bit0) */

{

TIM0_CH0_OldTs = TIM0_CH0_NewTs; /* 当前值更新到上一次变量里 */

TIM0_CH0_NewTs = TIM0_CH0_GPR0_Value & 0x00FFFFFF;

/* 取出GPR0的低24bit存入TIM0_CH0_NewTs */

TIM0_CH0_OldDiff = TIM0_CH0_NewDiff; /* 当前差值更新到上一次差值变量里 */

/*calculate new difference between new time stamp and old time stamp */

if((TIM0_CH0_NewTs > TIM0_CH0_OldTs) && TIM0_CH0_OldTs)

/* 状态1:GPR0的值在正常增加 */

{

TIM0_CH0_NewDiff = TIM0_CH0_NewTs - TIM0_CH0_OldTs; /* 计算当前的差值 */

}

else if(TIM0_CH0_NewTs < TIM0_CH0_OldTs)

/* 状态:GPR0向上计数溢出. */

{

/* 计算当前的差值 */

TIM0_CH0_NewDiff = TIM0_CH0_NewTs + (0x00FFFFFF - TIM0_CH0_OldTs);

}

/* 缺齿时间是正常齿2.5~3.5倍之间 */

if(((10*TIM0_CH0_OldDiff)>(25*TIM0_CH0_NewDiff)) && ((10*TIM0_CH0_OldDiff)<(35*TIM0_CH0_NewDiff)))

{

/* 如果没有同步. */

if(DPLL_CRS_SyncState == DPLL_CRS_noSync)

{

GTM_DPLL_APT_2C.B.APT_2C = (57 + 3);

/* TRIGGER信号同步到RAM)2C的指针(缺齿后的第1个正常齿) */

GTM_DPLL_CTRL_1.B.SGE1 = TRUE;

/* enable SUB_INC1 generator. */

DPLL_CRS_SyncState = DPLL_CRS_WaitSync;

/* waiting for synchronization */

}

else if(DPLL_CRS_SyncState == DPLL_CRS_Sync)

/* 如果同步. */

{

GTM_TBU_CHEN.B.ENDIS_CH1 = 2;

/* enable TBU channel 1 */

GTM_TIM0_CH0_IRQ_EN.B.NEWVAL_IRQ_EN = FALSE;

/* 禁止TIM0 channel 0 NEWVAL interrupt. */

}

}

}

}5.2、MAP初始化

见AURIX-TC3xx-GTM详解五-MAP(TIM0 Input Mapping Module)博客,同之。

5.3、DPLL处理

5.3.1、DPLL初始化

cs

/* DPLL. */

void Init_Dpll(void)

{

uint16 i;

uint8 relToothOffset = 0;

uint8 Cycle = 0;

static volatile unsigned int *DPLL_RAM2 = (unsigned int *) 0xF012C000;

/* 定义DPLL RAM2起始地址 */

static volatile unsigned int *DPLL_ADT_Tx = (unsigned int *) 0xF012C400;

/* 定义DPLL RAM2c起始地址,与RAM2的起始地址0xF012C000之间留点余量即可 */

/* 确保所有RAM初始化已经完成,即INIT_RAM位为0. */

while (GTM_DPLL_RAM_INI.B.INIT_RAM)

{

/* 等待RAM初始化完成. */

}

/* 初始化RAM2所有部分的值为0,RAM2大小为0x4000 . */

for(i=0;i<GTM_DPLL_RR2_SIZE;i++)

{

DPLL_RAM2[i] = 0;

}

/* 复制60-2期望的波形到DPLL_ADT_Tx(0xF012C400地址开始RAM2区域) */

/* 波形为57正常齿+1个缺齿+57个正常齿+1个缺齿,即2圈曲轴转速 */

for (Cycle = 0; Cycle < 2; Cycle++)

{

for(i = relToothOffset; i <(57+relToothOffset);i++)

{

DPLL_ADT_Tx[i] =0x10000; /* normal tooth. */

}

DPLL_ADT_Tx[57+relToothOffset] =0x30000; /* gap tooth. */

relToothOffset = 58;

}

/* configure DPLL parameter. */

GTM_DPLL_OSW.B.OSS = 0; /* 配置RAM2储存值数量为128,以上存储值数量是116个,足够. */

GTM_DPLL_MPVAL1.U = 0; /* not used in this case. */

GTM_DPLL_TOV.U = 2.5*1024;

/* 缺齿时间超过正常齿的2.5倍就会触发丢失TRIGGER信号中断 */

GTM_DPLL_PVT.B.PVT = 0.5*1024;

/* Plausibility value of next active TRIGGER slope. equal to 0.5 times normal tooth*/

GTM_DPLL_TLR.U = 4;

/* max time between 2 active slopes. equal to 4 times normal tooth*/

GTM_DPLL_THMI.U = 0;

/* Minimal time between active and inactive TRIGGER slope. */

GTM_DPLL_THMA.U = 0xFFFF;

/* Maximal time between active and inactive TRIGGER slope. */

GTM_DPLL_IRQ_MODE.B.IRQ_MODE = IfxGtm_IrqMode_pulseNotify;

/* pulse-notify mode. */

/* Get of lock interrupt for SUB_INC1 request. */

IfxSrc_init(&MODULE_SRC.GTM_DPLL[13],IfxSrc_Tos_cpu0,IFX_INTPRIO_GTM_DPLL_GL1);

IfxSrc_enable(&MODULE_SRC.GTM_DPLL[13]);

GTM_DPLL_IRQ_EN.B.GL1I_IRQ_EN = TRUE;

/* Loss of lock interrupt for SUB_INC1 request. */

IfxSrc_init(&MODULE_SRC.GTM_DPLL[14],IfxSrc_Tos_cpu0,IFX_INTPRIO_GTM_DPLL_LL1);

IfxSrc_enable(&MODULE_SRC.GTM_DPLL[14]);

GTM_DPLL_IRQ_EN.B.LL1I_IRQ_EN = TRUE;

/* set DPLL Control Register 0. */

Ifx_GTM_DPLL_CTRL_0 DPLL_CTRL0;

DPLL_CTRL0.U = 0x00000000; /* Initial value is 0. */

DPLL_CTRL0.B.MLT = (MultiFreq-1)&0x000003FF; /* Multiplier for TRIGGER is 600 times, */

DPLL_CTRL0.B.TNU = (Tooth60_2-1)&0x000000FF; /* TRIGGER number is 60 normal tooth. */

DPLL_CTRL0.B.TEN = TRUE; /* TRIGGER signal is enabled. */

GTM_DPLL_CTRL_0.U = DPLL_CTRL0.U; /* write to register. */

/* set DPLL Control Register 1. */

Ifx_GTM_DPLL_CTRL_1 DPLL_CTRL1;

DPLL_CTRL1.U = 0x00000000; /* Initial value is 0. */

DPLL_CTRL1.B.PIT = TRUE; /* The plausibility value is time related.将PVT值乘以最后一次增量DT_T_ACT的持续时间,然后除以1024. */

DPLL_CTRL1.B.SYN_NT = 2; /* gap tooth number. */

DPLL_CTRL1.B.TSL = 2; /* falling edge as trigger signal*/

GTM_DPLL_CTRL_1.U = DPLL_CTRL1.U; /* write to register. */

/* enable DPLL module. */

GTM_DPLL_CTRL_1.B.DEN = TRUE;

}