可查看GZH:小蘇的FPGA

目录

[1.1 、GT核实现万兆网功能](#1.1 、GT核实现万兆网功能)

[1.1.2 、GT核的使用](#1.1.2 、GT核的使用)

[1.2、 10G Ethernet Subsystem核实现万兆网](#1.2、 10G Ethernet Subsystem核实现万兆网)

[2.1 、10G Ethernet Subsystem核应用](#2.1 、10G Ethernet Subsystem核应用)

[2.2 、GT核应用](#2.2 、GT核应用)

[三 、 代码](#三 、 代码)

由于市面上缺少10G PHY芯片以及功耗等原因,在FPGA板卡中使用万兆以太网通信方案时,主要基于SerDes采用光模块或背板等途径实现。

一、FPGA实现10G以太网

本文主要介绍UltraScale/+系列FPGA的实现方式,7系列方式相同,只是7系列借助的GT或者MAC核与UltraScale/+系列稍有差异。

通过自行编码不借助官方IP实现PHY+MAC功能的方式,大概是从事芯片、IP设计等工作,不在本次讨论之内。本文主要介绍通过借助Xilinx IP核实现万兆以太网:GT收发核、10G Ethernet Subsystem核、10G Ethernet PCS/PMA核(此核7系列支持)。

由于手头上只有UltraScale+的FPGA,封装为QSFP,所以接下来只介绍GT核与10G Ethernet Subsystem核实现万兆网的方式。

1.1 、GT核实现万兆网功能

基于SerDes实现10G以太网通信采用64B/66B编码方式,串行线速率为10.3125Gbps。

1.1.1、万兆网PCS层编码

10GBASE-R:适用于光纤等连接;10GBASE-KR:适用于背板连接;

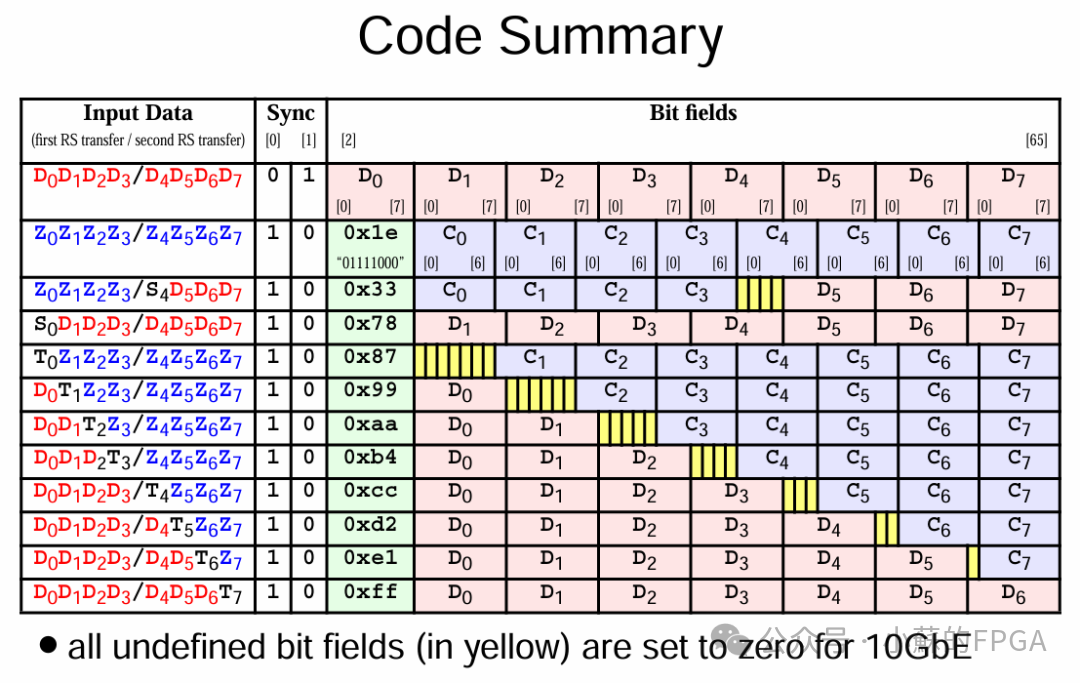

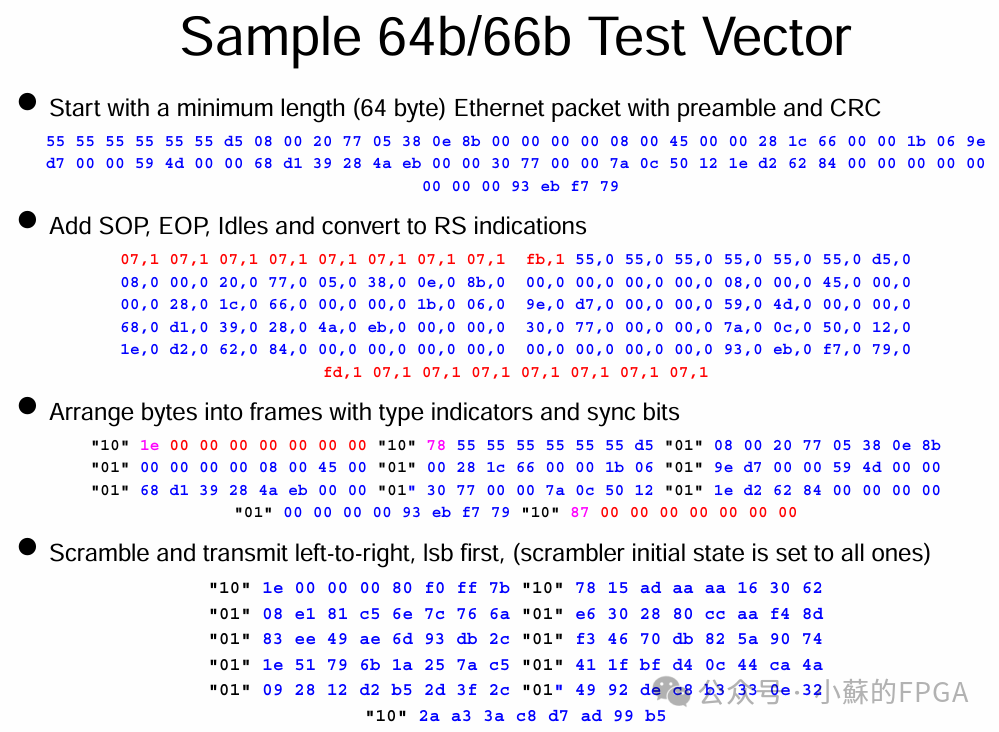

8B10B编码开销比较大,万兆网通信采用64B66B编码。64B66B编码在发送前需要对数据加扰,在接收数据时也要先对数据解扰。64bit数据经过加扰尽量保证0/1均衡和时钟恢复,在加扰后的64bit数据前加入2bit的同步位(Sync)组成66bit数据,同步位表示该64bit数据是数据帧还是控制帧。

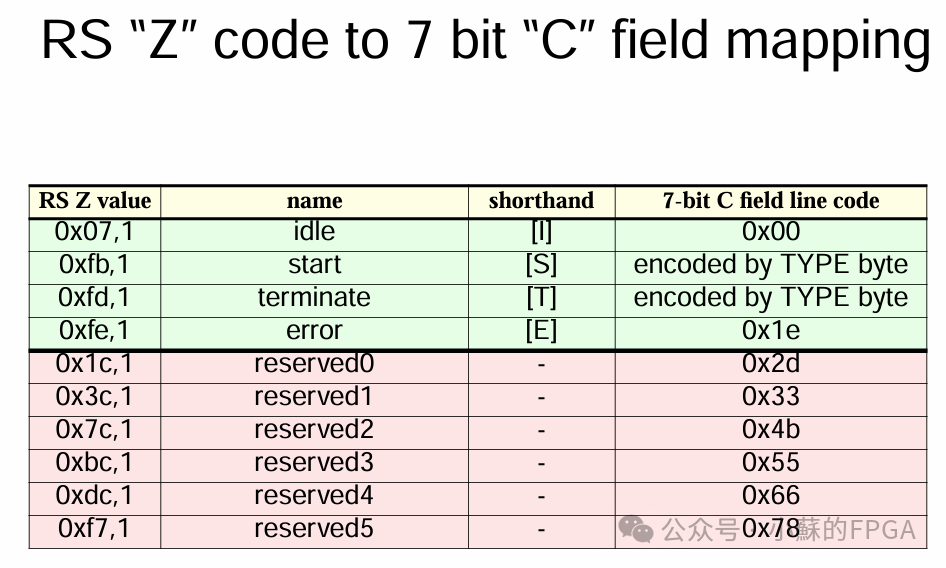

10G以太网PCS层的同步位和数据、状态信息如下:

相关字段如下:

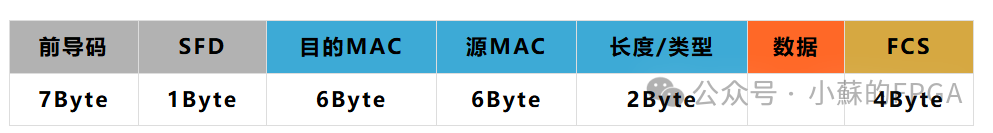

以太网帧结构及字段信息参考:FPGA实现千兆网UDP协议(含ARP、ICMP)。下图中的以太网帧结构中的各字节段对应于上图中的Data字段。

比如一帧报文的发送如下:空闲IDLE(0x07)+ START(0xFB)+ 前导码+ SFD + MAC + ...... + FCS + TERMINATE(0xFD)

上述结构根据图3的符合情况,再继续封装后,进行加扰处理。

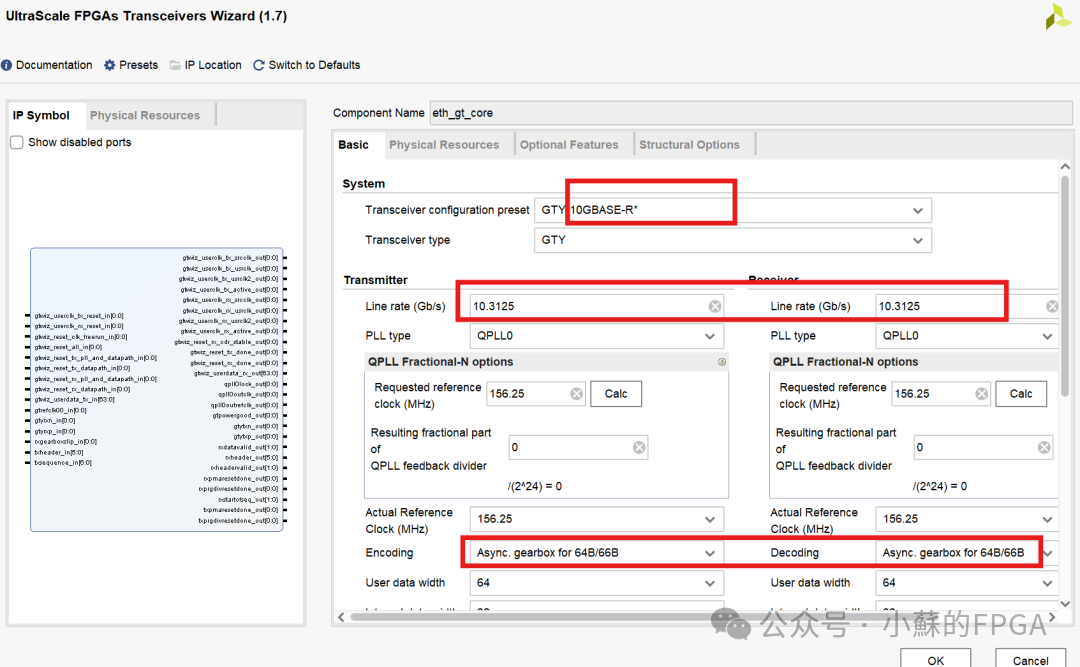

1.1.2 、GT核的使用

根据本人的开发板原理图, GT核的配置如下:

对外QSFP封装,选用10GBASE-R;

线速率:10.3125Gbps;

编码:64B66B,异步变速箱(不采用Sync,否则每33个周期插入一个空闲周期)

GTY由FPGA型号决定;

用户数据64bit;

1.1.3、万兆网开发

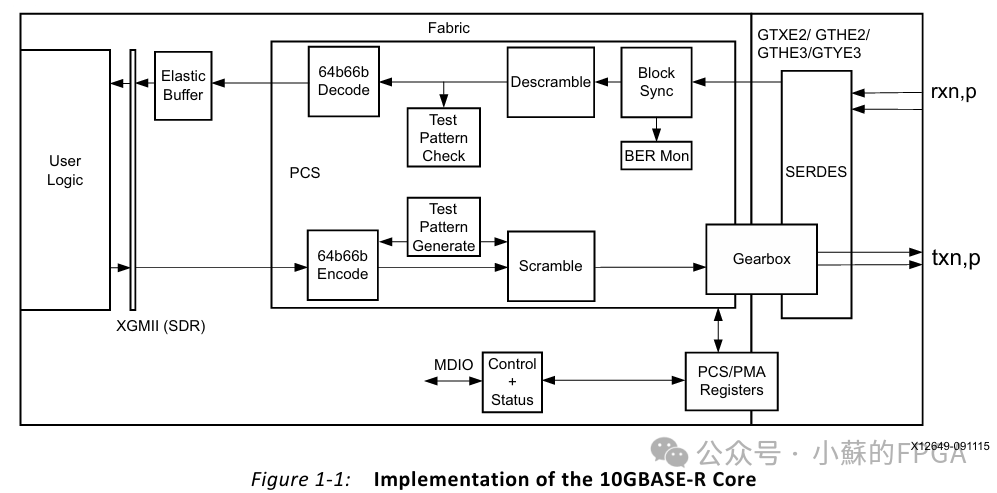

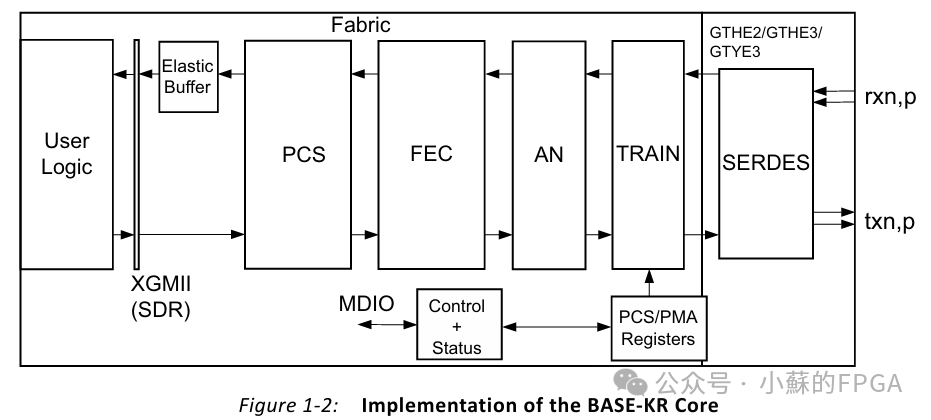

借助例化上述GT核后,可按照图1开发编码实现PCS相关功能:对于发送帧功能,用户端的帧数据,封装起始、结束、空闲码后,经加扰后,结合同步字段,经变速箱Gearbox,并串转换等,最终经电路传送出去;对于接收,是上述过程的逆操作。

开发过程主要涉及:帧数据按照上节内容封装与解封、同步字段的增添与解析、加解扰。其中帧数据的封装与解析按照以太网协议进行即可。

1.2、 10G Ethernet Subsystem核实现万兆网

此方式是实现万兆网通信最快捷的方法,只是需要license。开发按照以太网协议对网络帧进行解析与封装即可,只需关心如下结构:

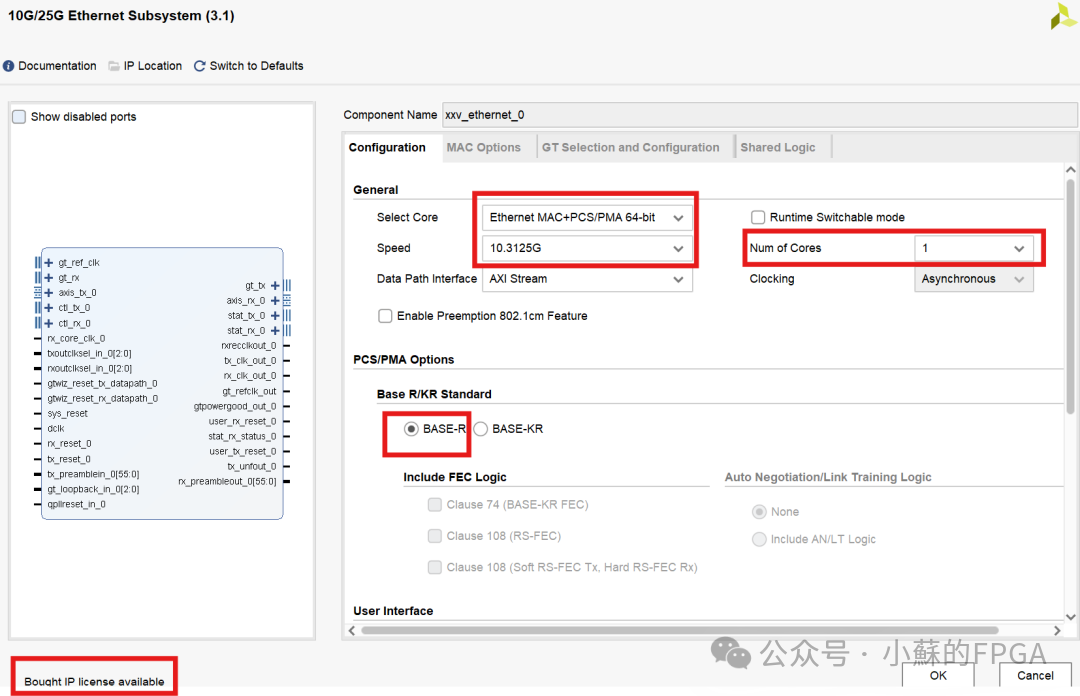

10G Ethernet Subsystem核的配置如下:

核数目:1;本次实验1对收发,也可配置多路万兆网。(比7系列简便,多通道收发要例化多个核)

其他部分,根据原理图对应配置即可。

二、万兆网功能开发及测试

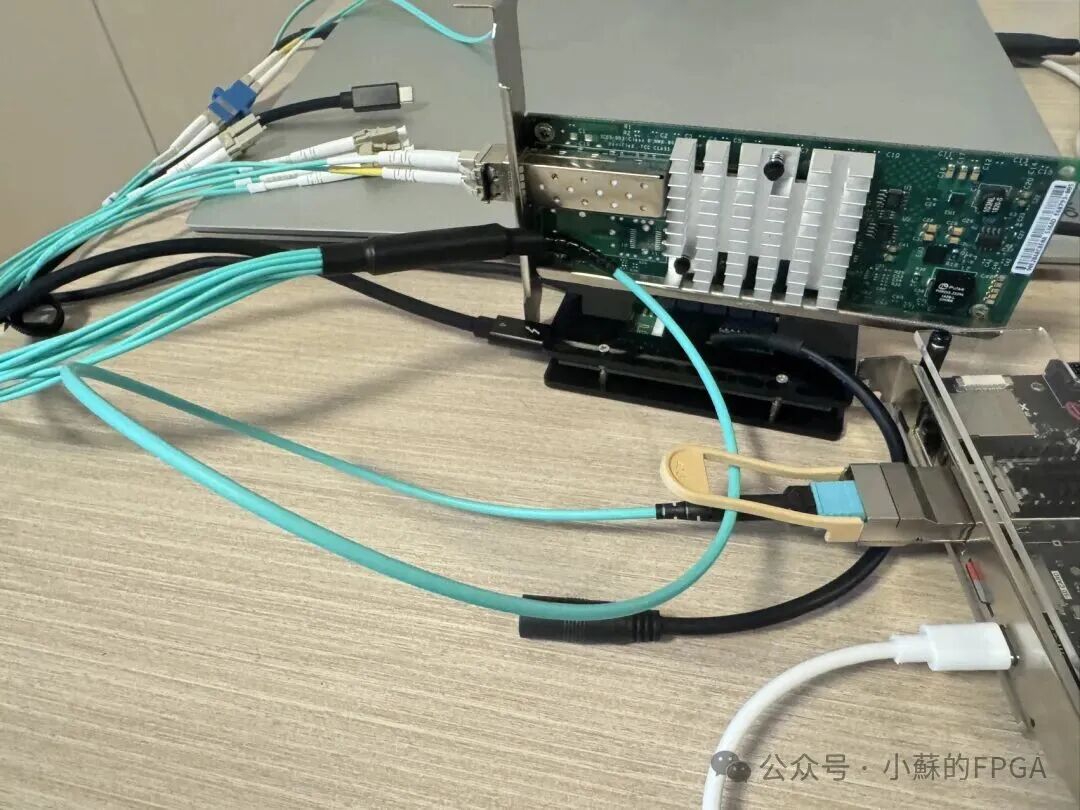

开发板只有QSFP封装的,测试采用MPO-LC光纤经 SFP+ 光模块连接万兆网卡与上位机通信测试。

2.1 、10G Ethernet Subsystem核应用

2.1.1、工程搭建

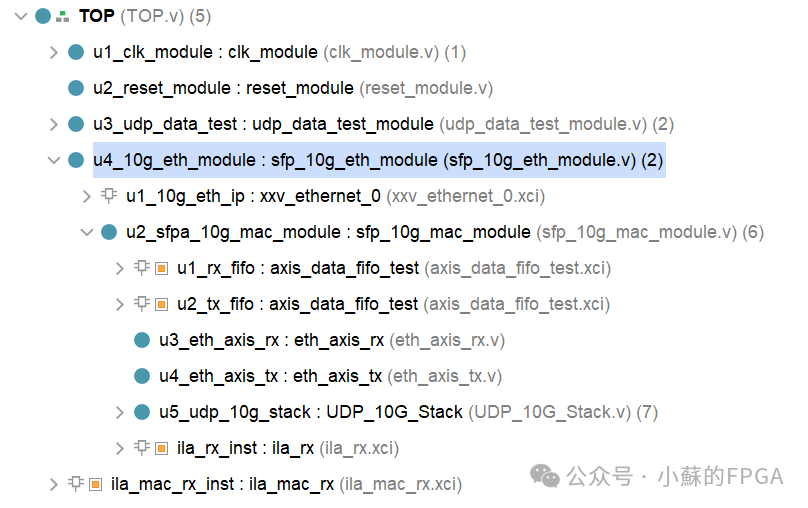

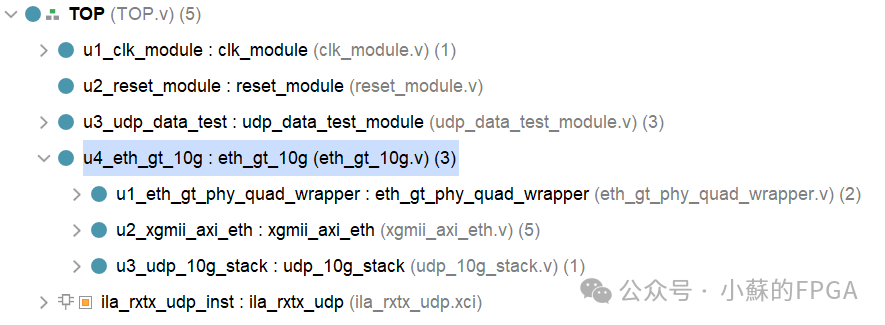

开发UDP协议栈,含UDP、ARP、ICMP(ping)收发功能。工程结构如下:

2.1.2、工程测试

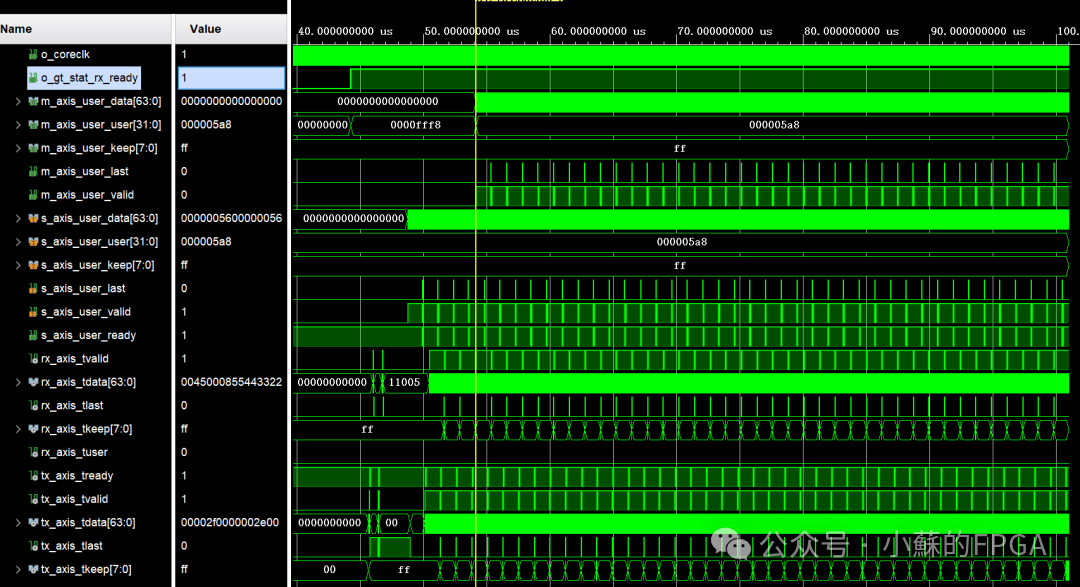

自回环仿真测试:先进行ARP寻址,后进行收发UDP报文。

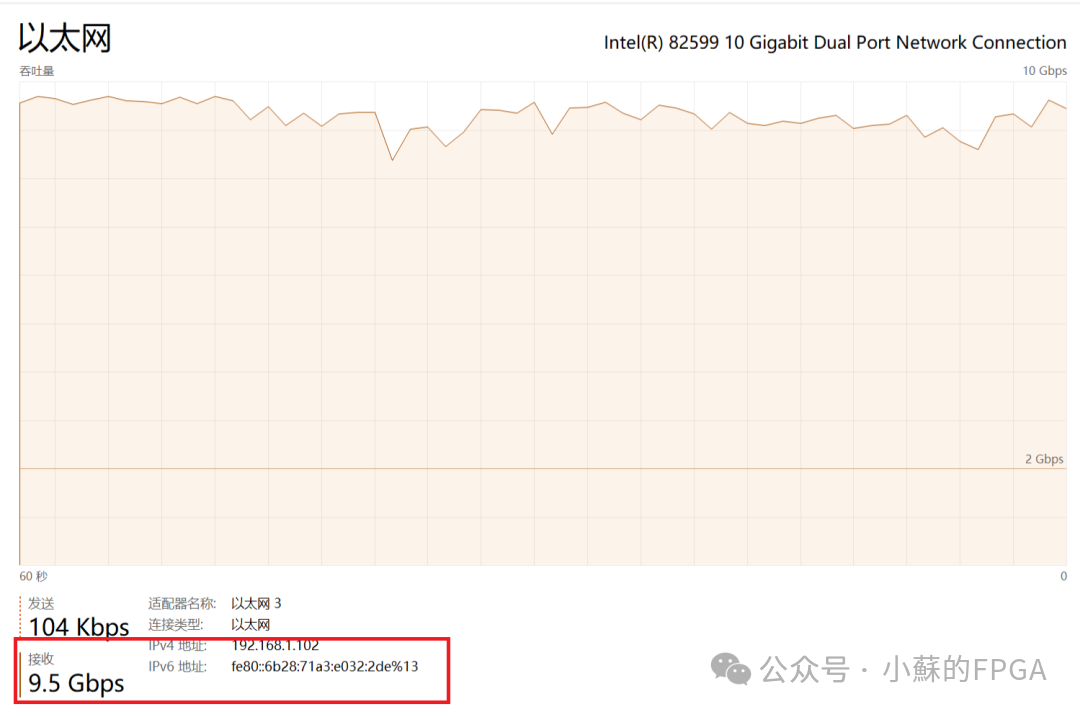

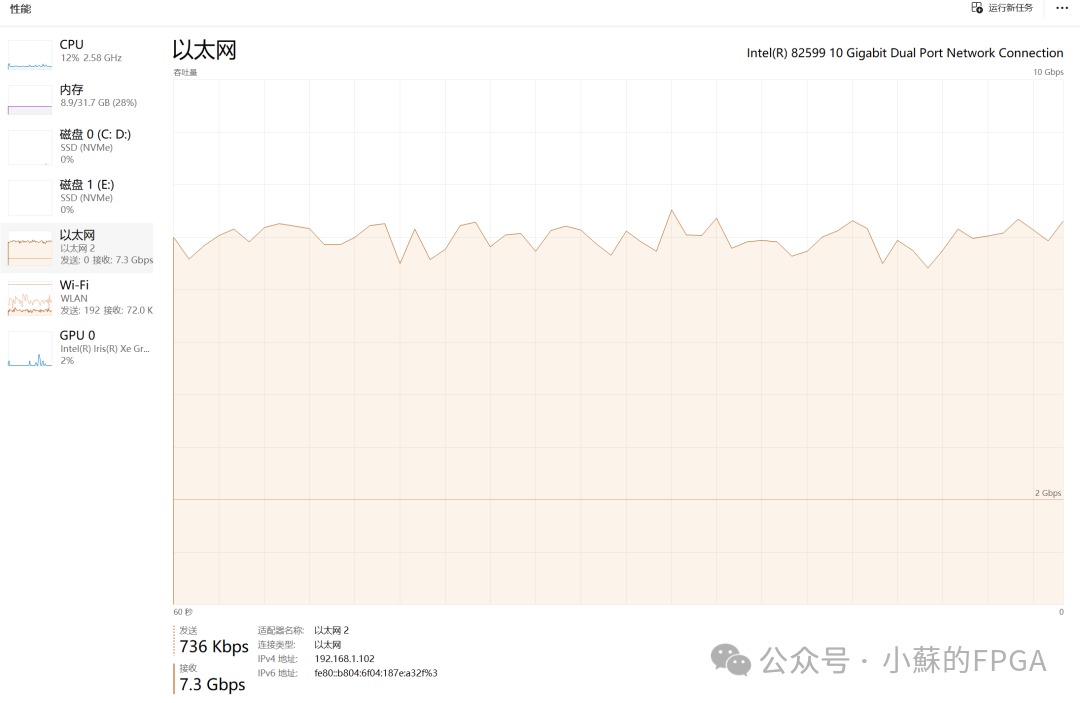

速度测试:VIO使能控制向上位机发送报文进行速度测试,速率达到9.5Gbps。

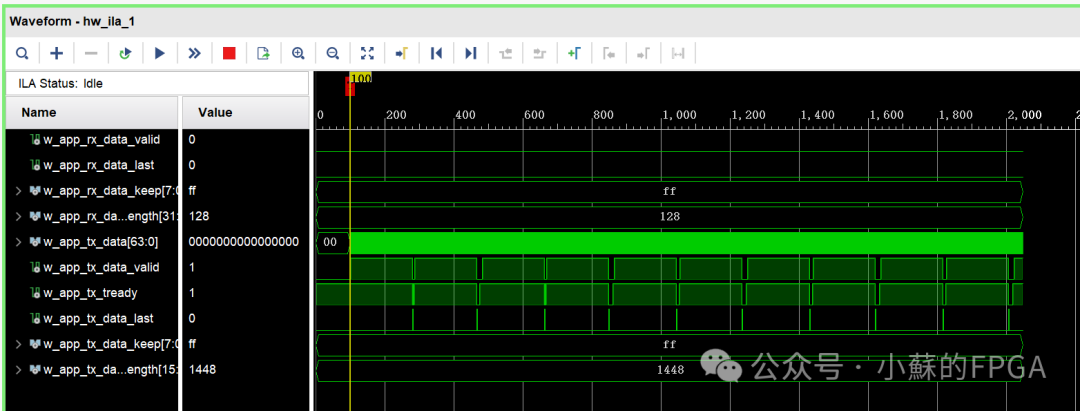

用户数据发送:

接收速率:

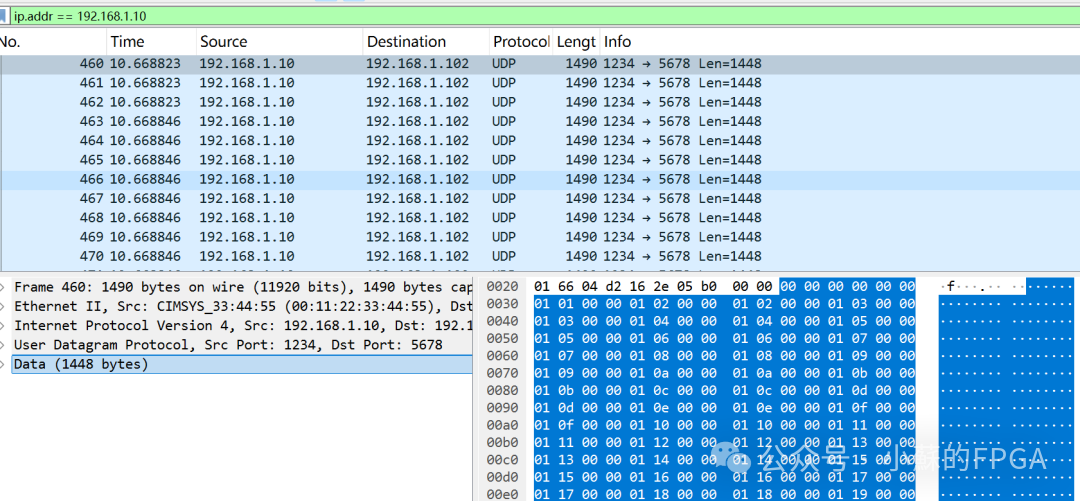

wireshark抓取的报文:

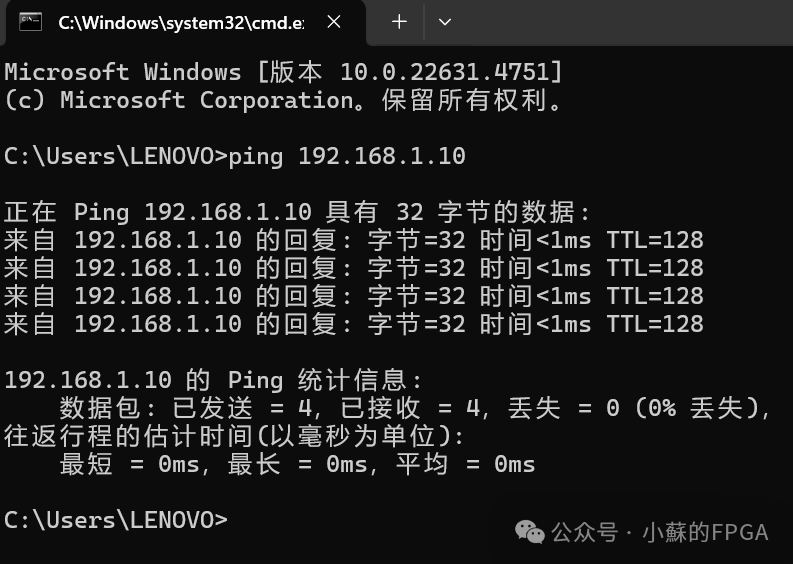

Ping功能测试:

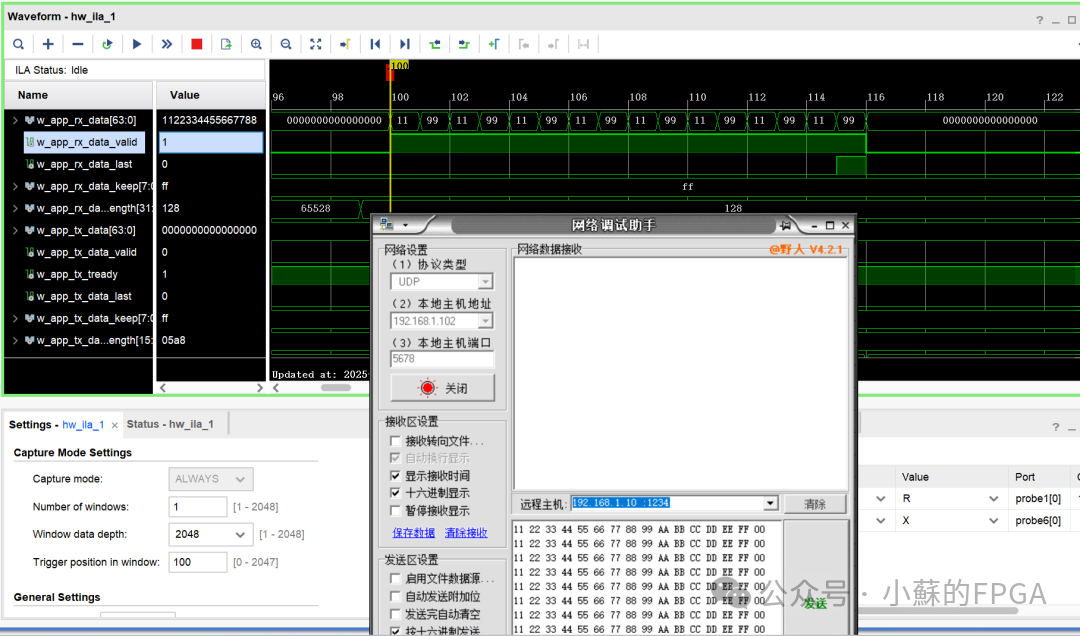

接收UDP报文:能正常解析出UDP数据部分和长度信息等。

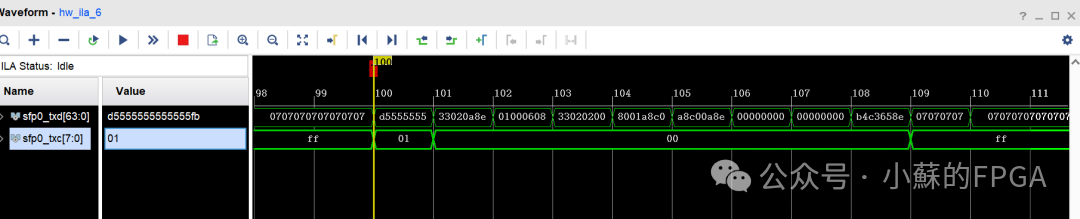

2.2 、GT核应用

工程结构如下:

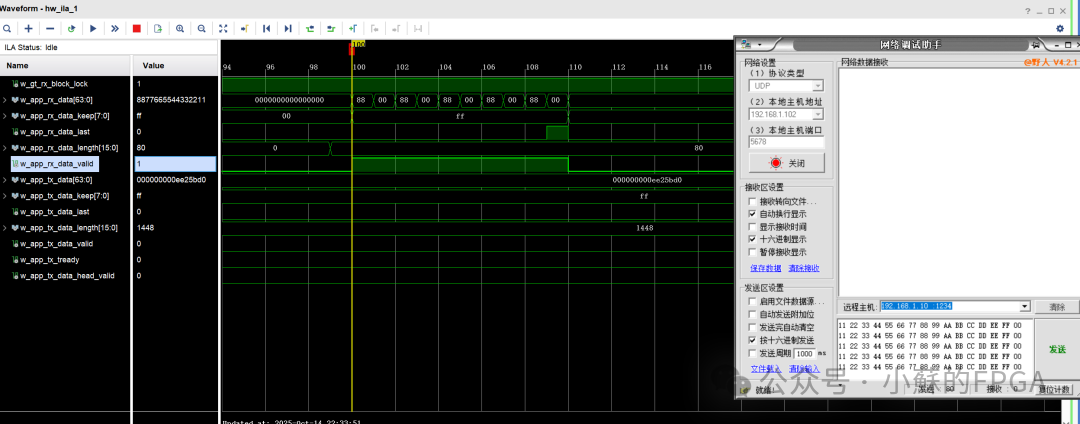

UDP报文接收:能正常解析出UDP数据部分和长度信息等。

UDP报文发送速率测试:VIO使能控制向上位机发送报文进行速度测试

三 、 代码

有需要相关代码的请私信。可查看GZH:小蘇的FPGA

FPGA 40G/50G Ethernet Subsystem核的使用

JESD204B的使用系列------3、DAC的应用(AD9164 9.6GSPS)

JESD204B的使用系列------2、协议及ADC的应用(AD9689)