EMIO使用

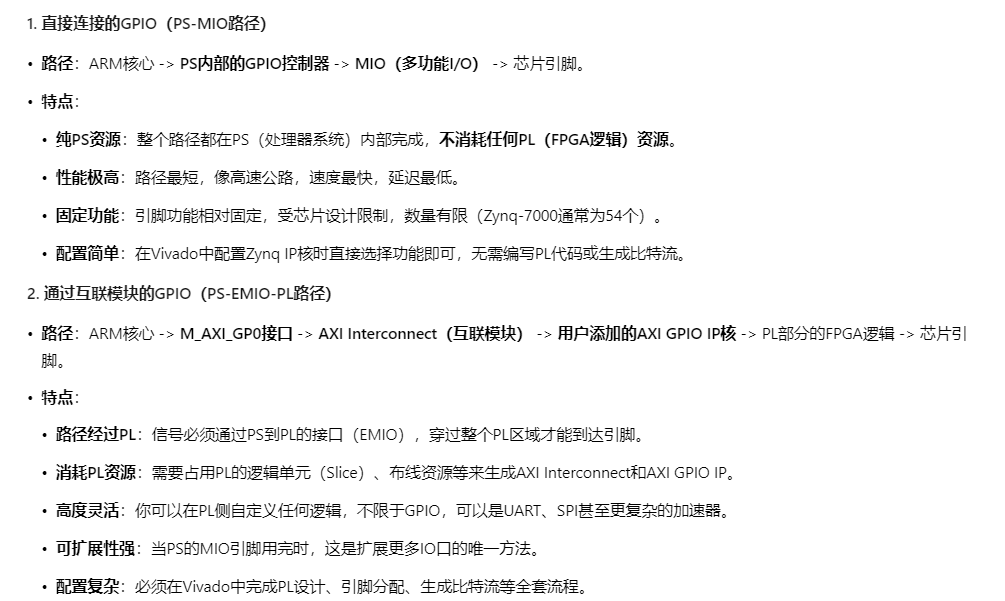

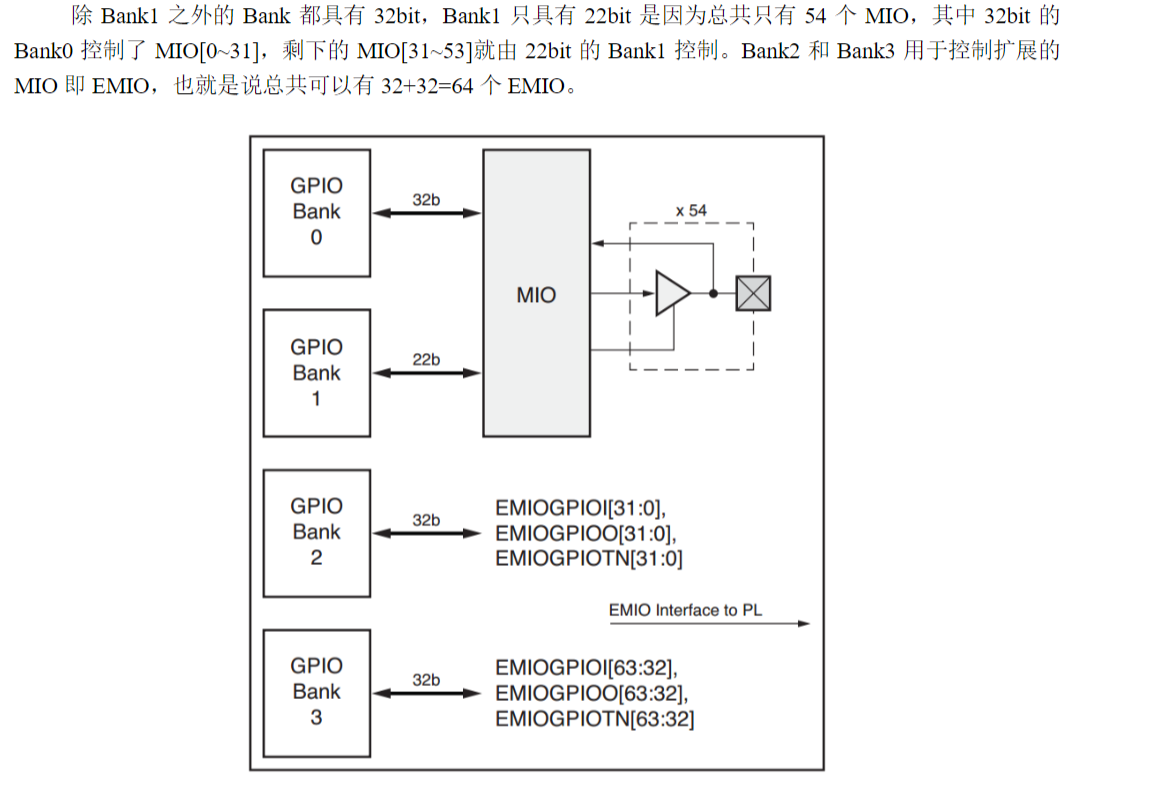

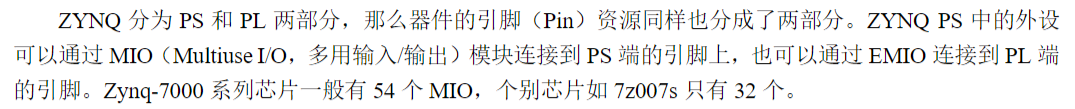

GPIO 可以通过 MIO 连接到 PS 端的引脚,也可以通过 EMIO 连接到 PL再到引脚。 mio是通过arm处理芯片和器件相互连接,emio是通过ps控制PL在到引脚。emio的时候,ps通过M_AXI_GPO的口然后进行互联和GPIO再输出,这些是EMIO 的路劲,再到管脚。

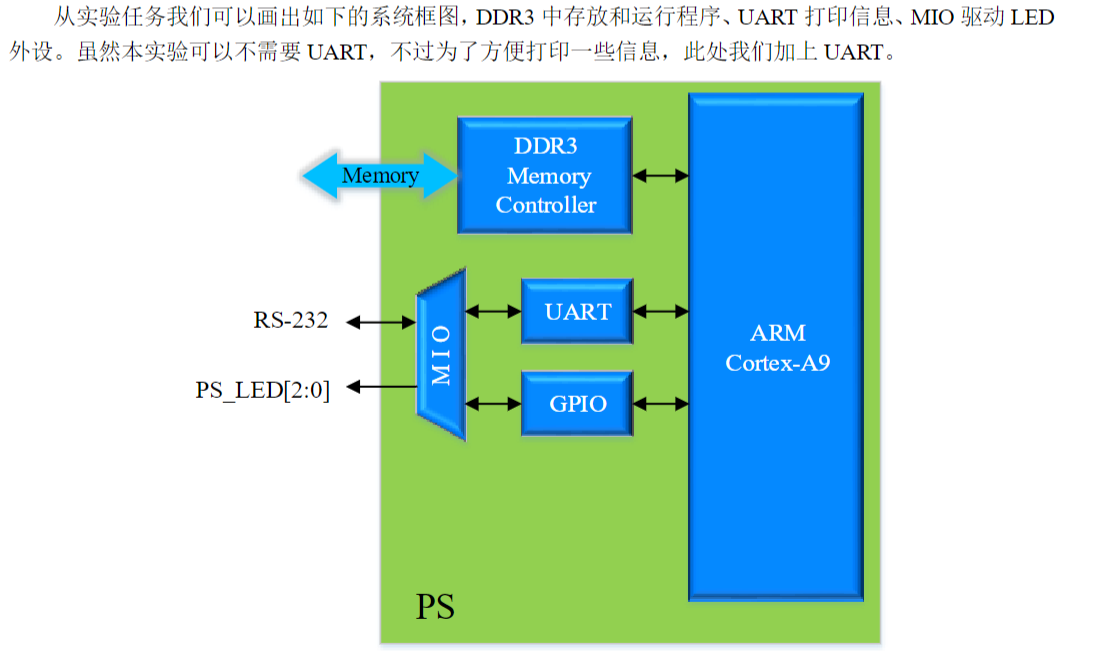

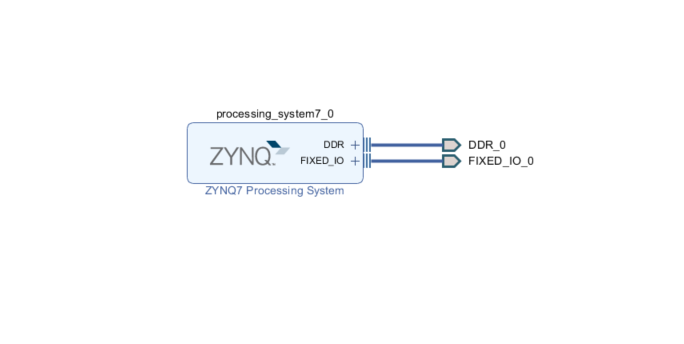

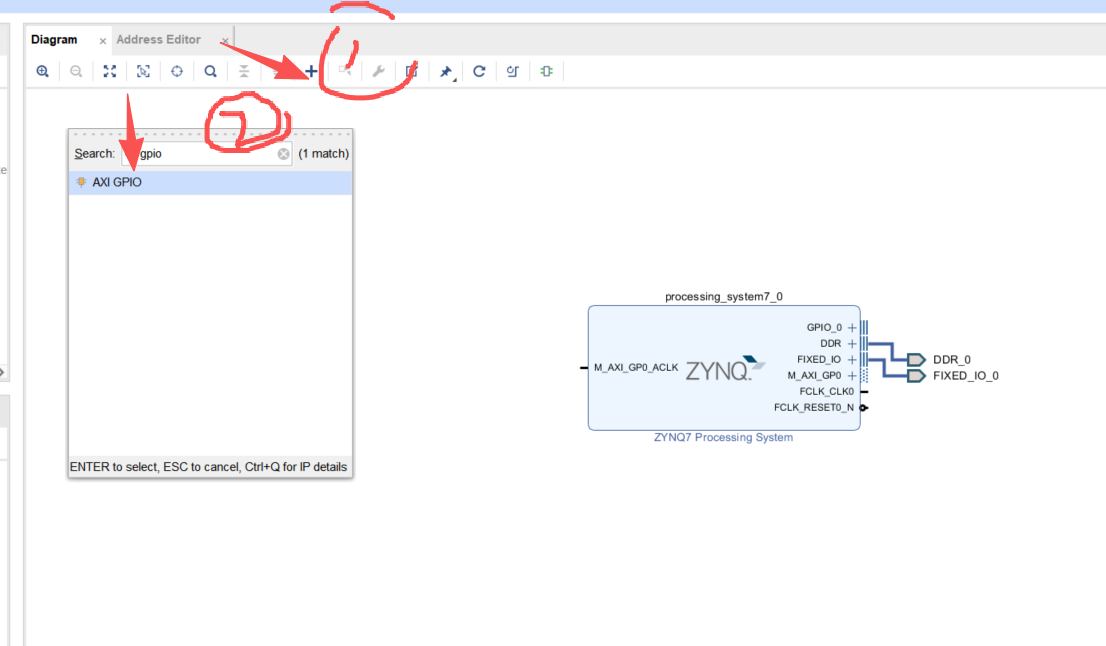

1.创建bd与PL进行互联

在原有的基础上进行扩展,前面说了MIO 是通过ps的GPIO口直接与pin脚相连控制外设器件的,而EMIO是通过ps的GPIO到FPGA的pl侧进行处理,然后在到外部管脚。现在拓展EMIO外设

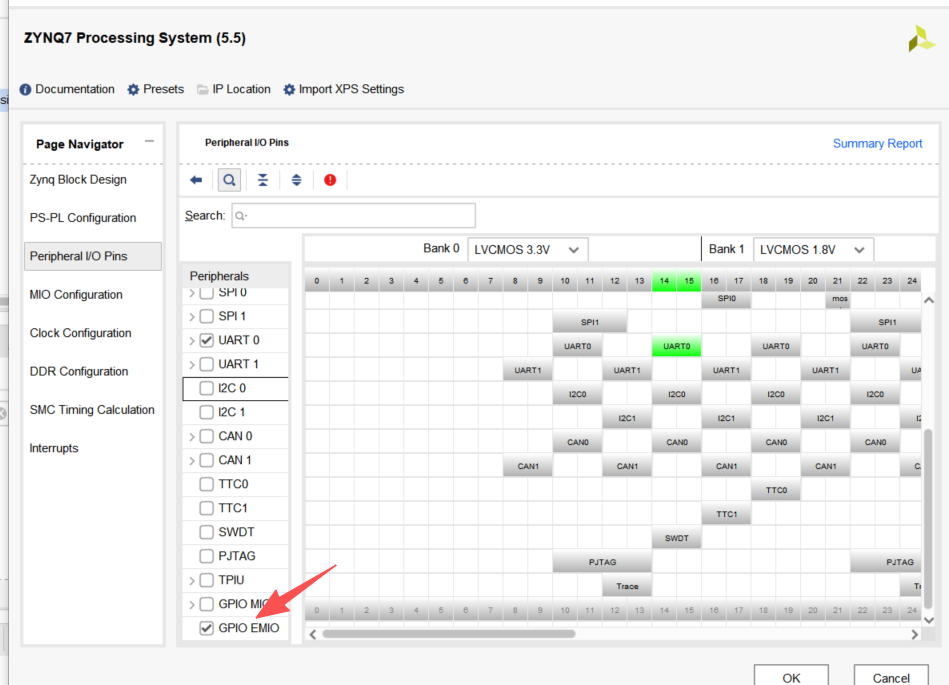

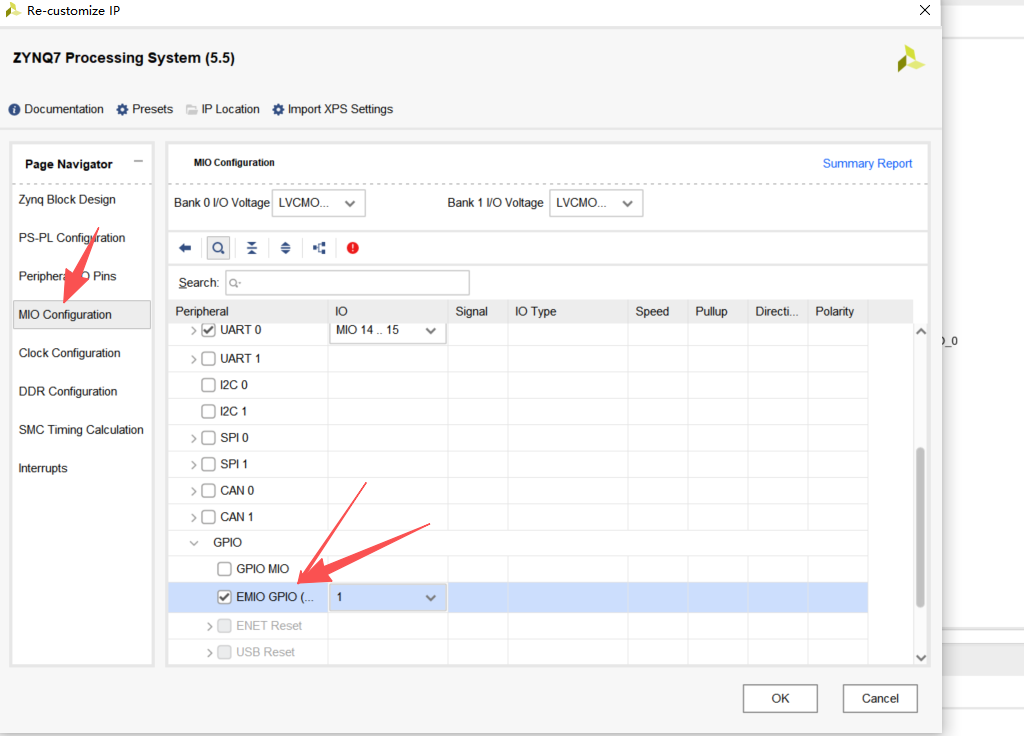

2.在bd中打开GPIO

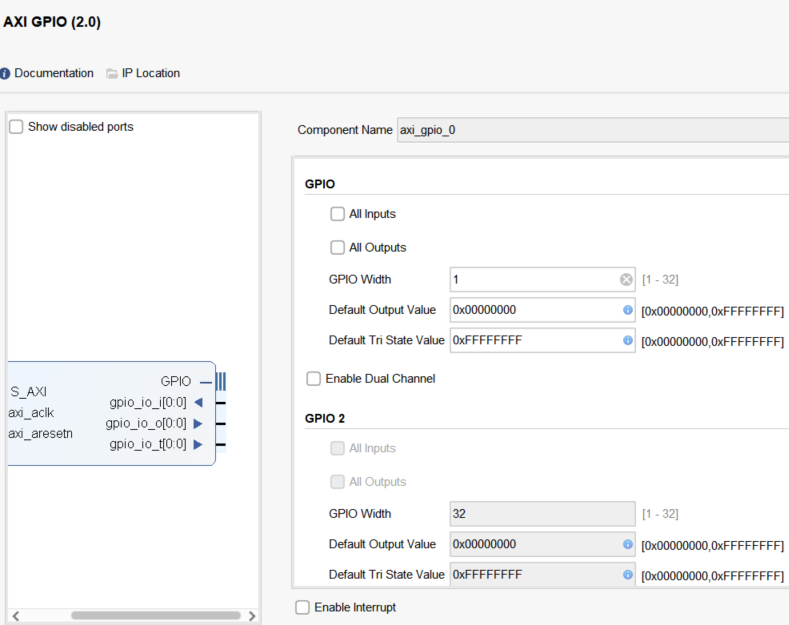

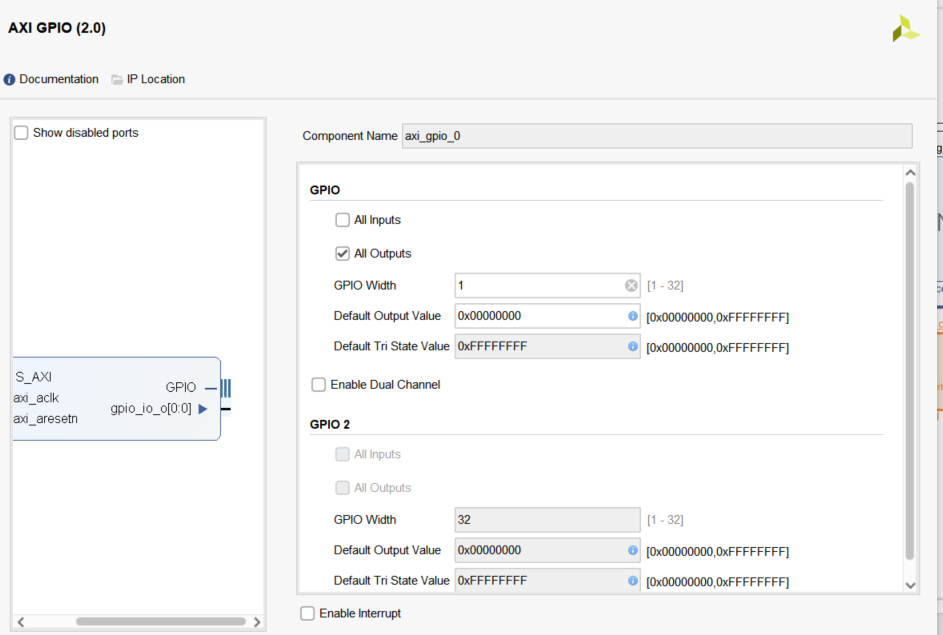

设置一个GPIO管脚

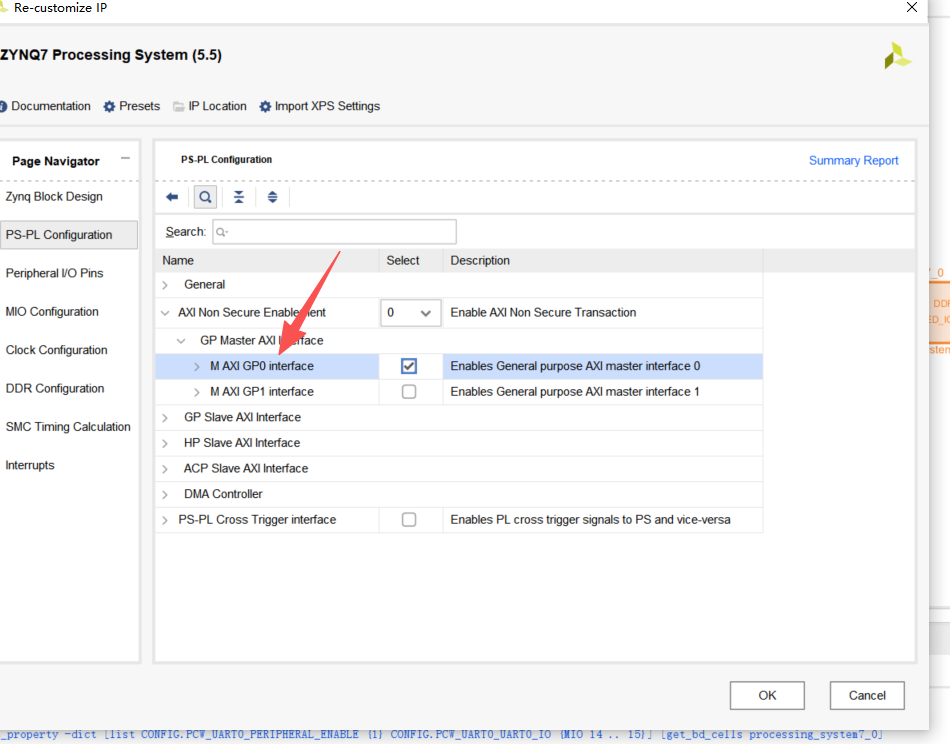

3.配置PS给PL侧进行传输信息通道GP

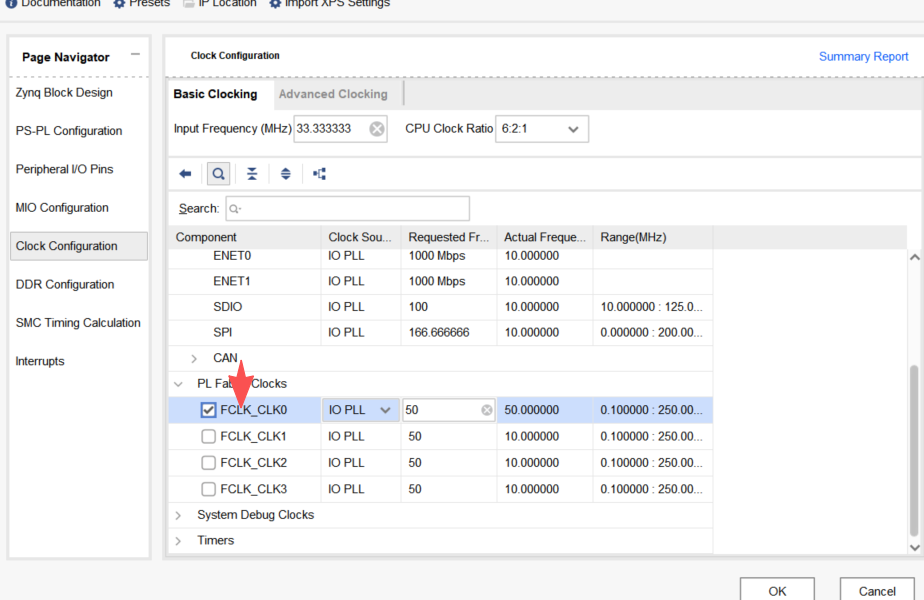

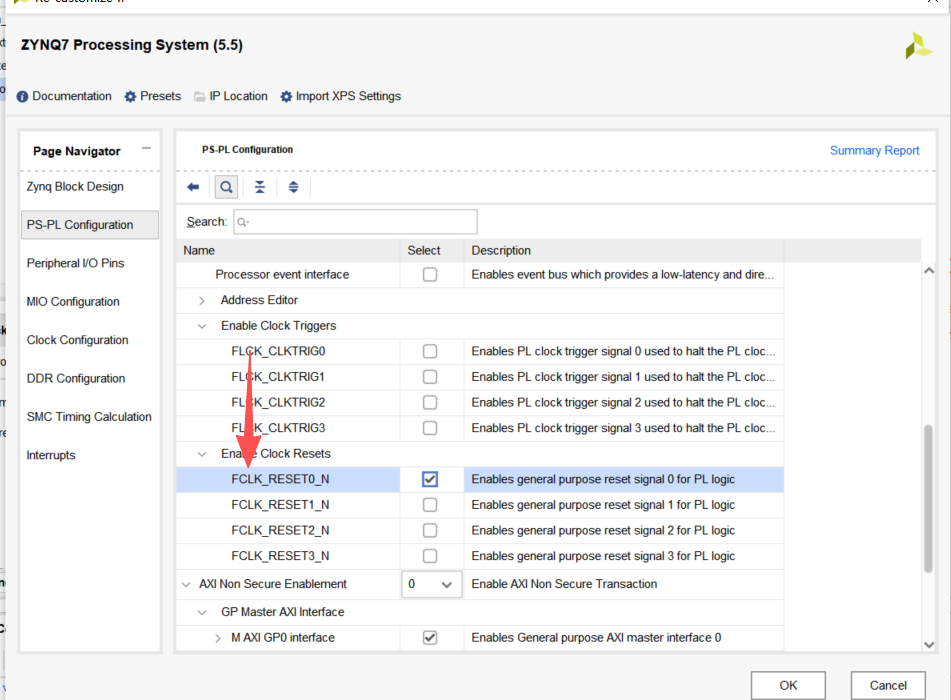

4.在配置给PL侧的时钟和复位

给PL的时钟

给PL的复位

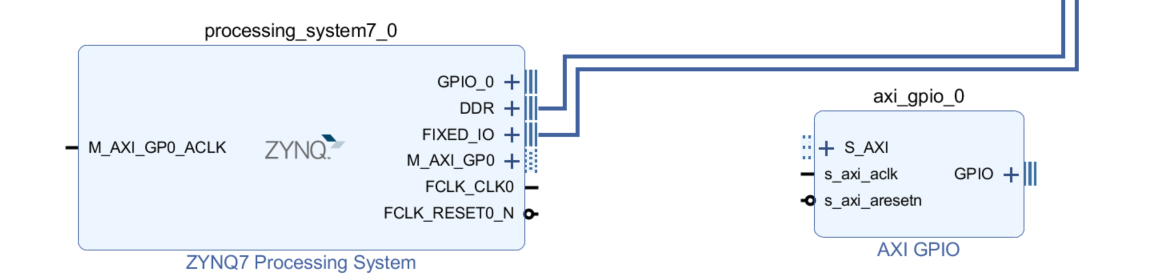

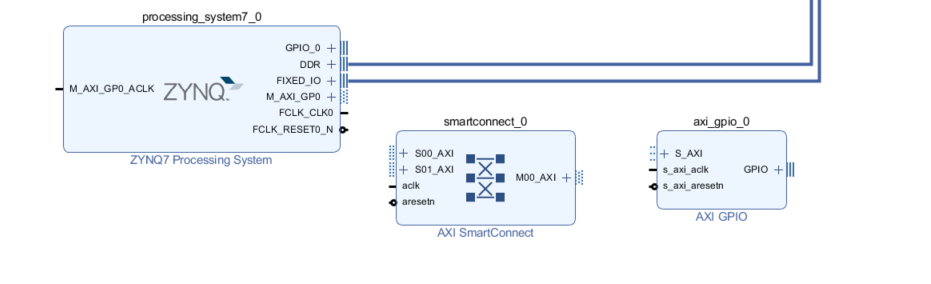

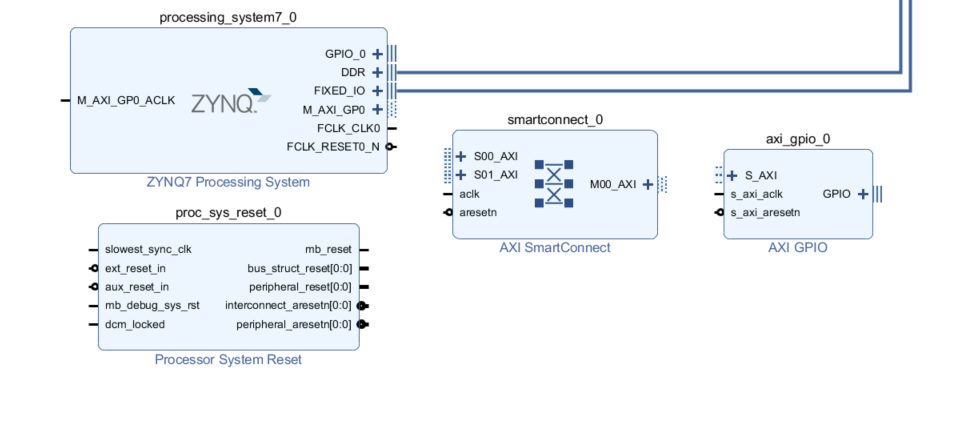

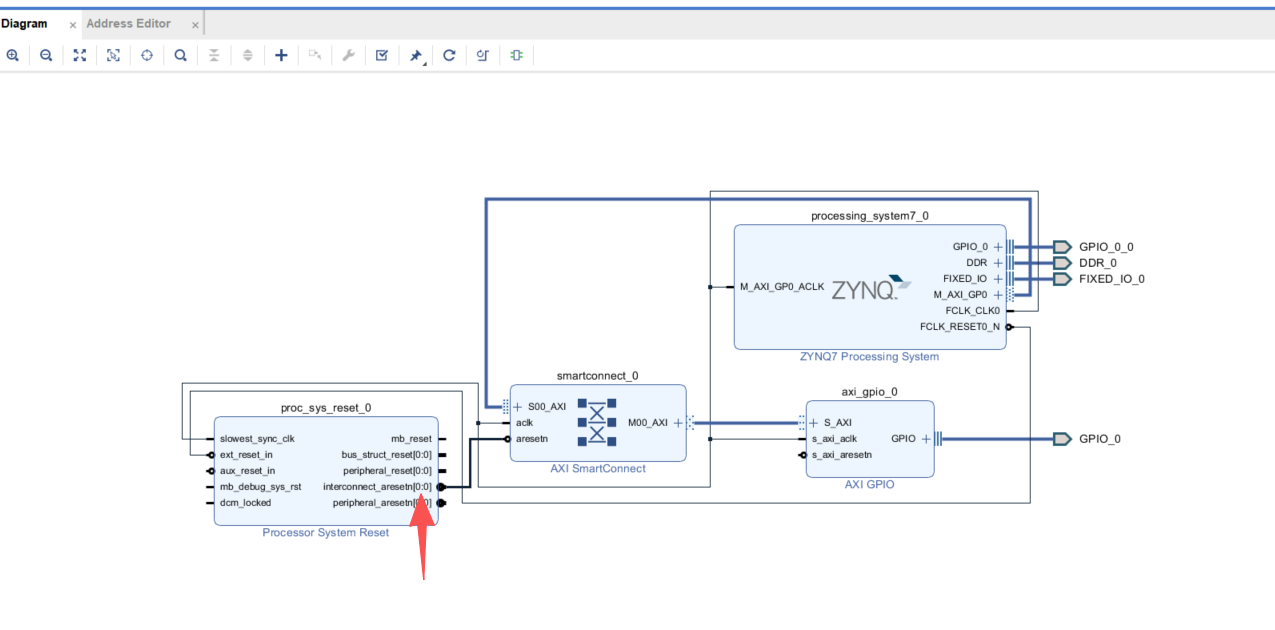

总的图如下图

5.PS的ARM设计完后,需要GPIO外设模块

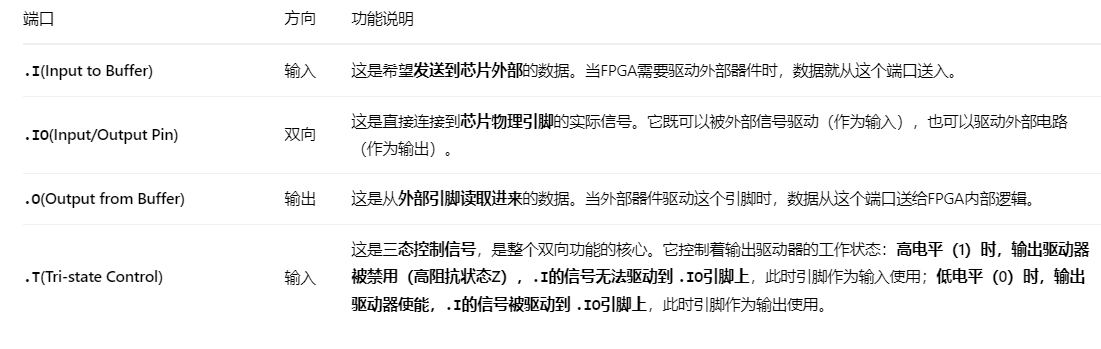

上述是给FPGA和外设的三态门

本工程用输出去控制

接下来需要给PL进行控制外设,但是上面的还不够完整还需要配置ps与gpio的axi互联模块

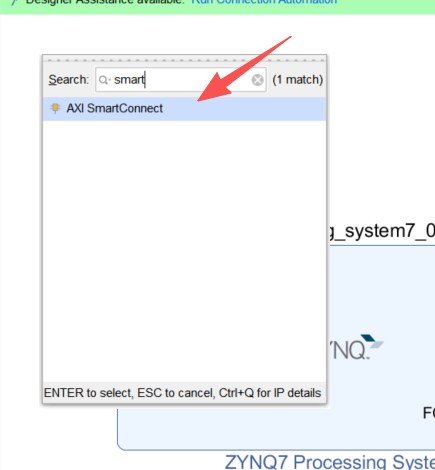

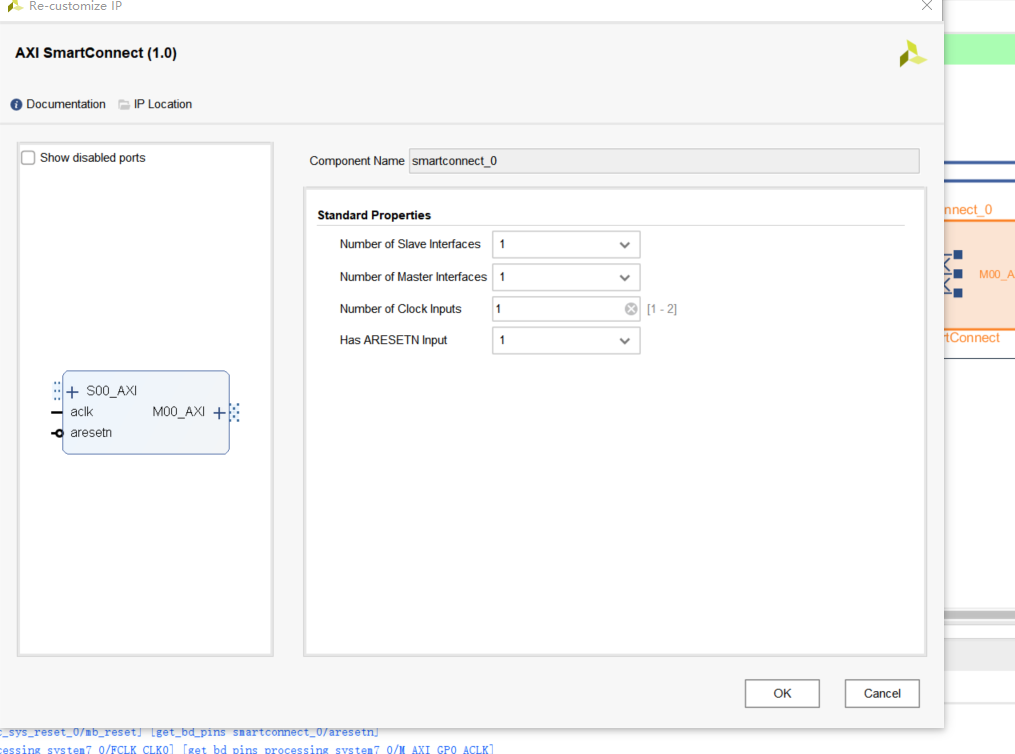

6.ps与gpio的axi互联模块

找到smartconnect模块。

互联模块给一个输入端口,,可以多个输出端口

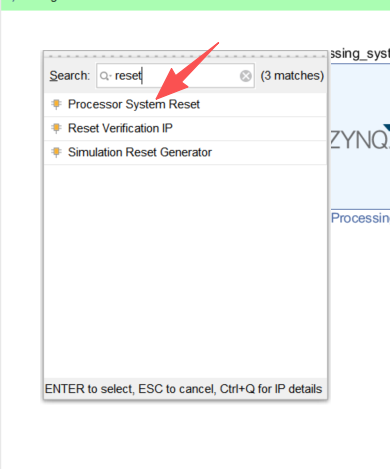

7.进行同步复位模块,每个工程基本的都有没有也可以,最好有,进行同步复位

完整框架如下

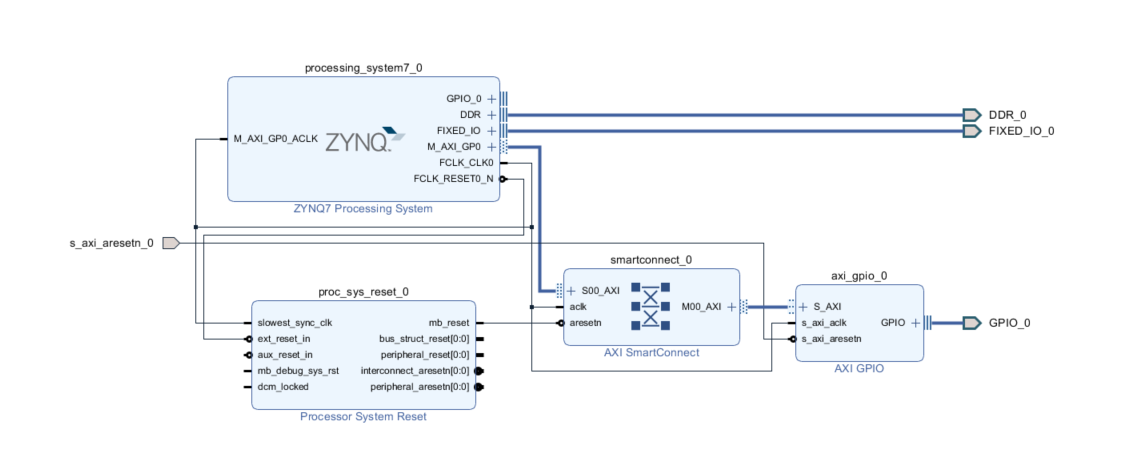

8.连接网络

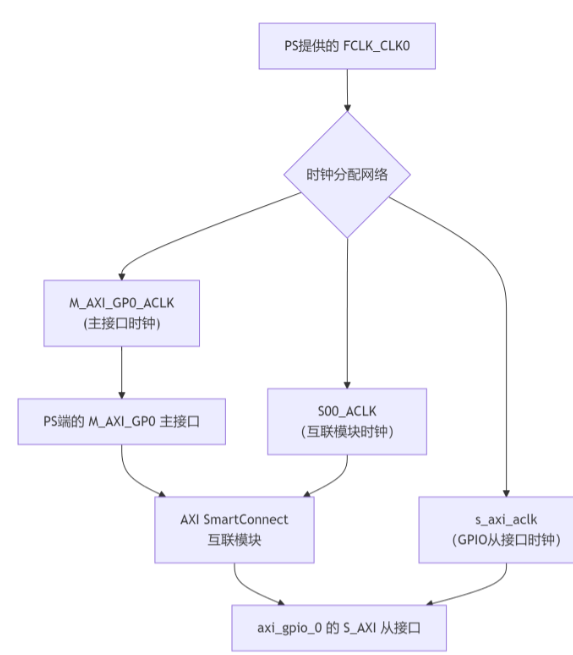

将ps的时钟链接互联模块,以及M_AXIGP0_ACLK,给去全局工作时钟。PS的复位给同步复位模块,然后同步复位给互联模块的复位

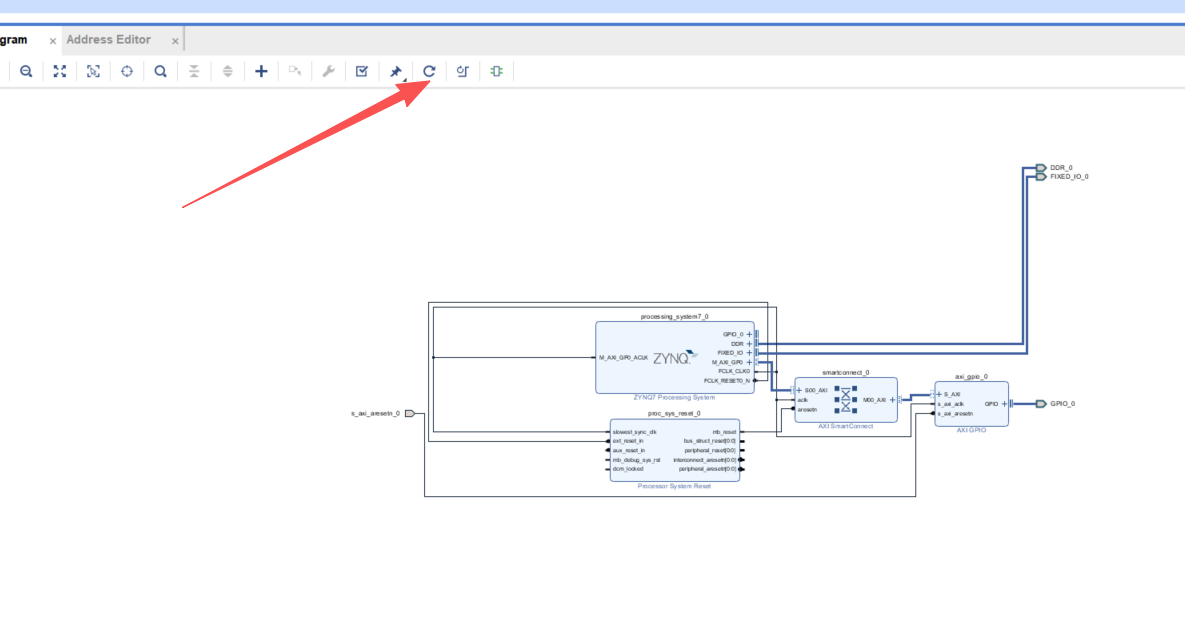

点击上述进行排版

上述接错了后面会报错正确连接如下互联模块复位链接错了

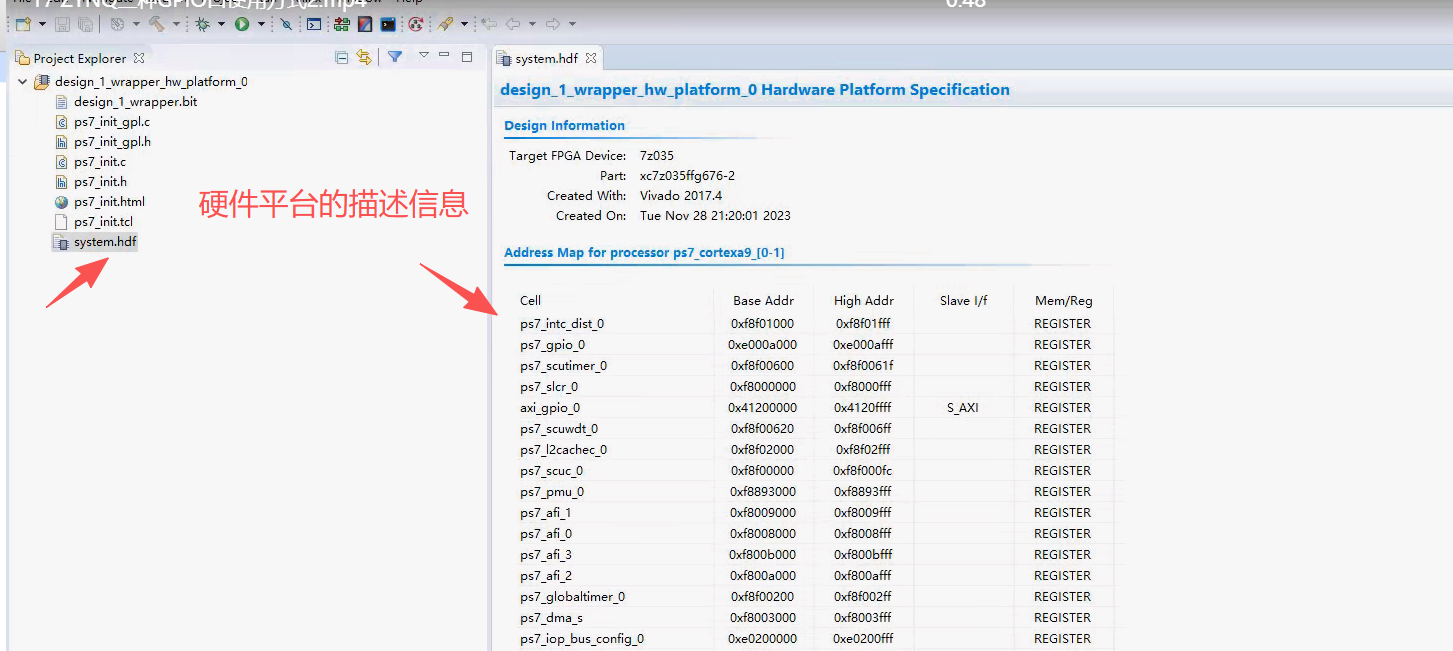

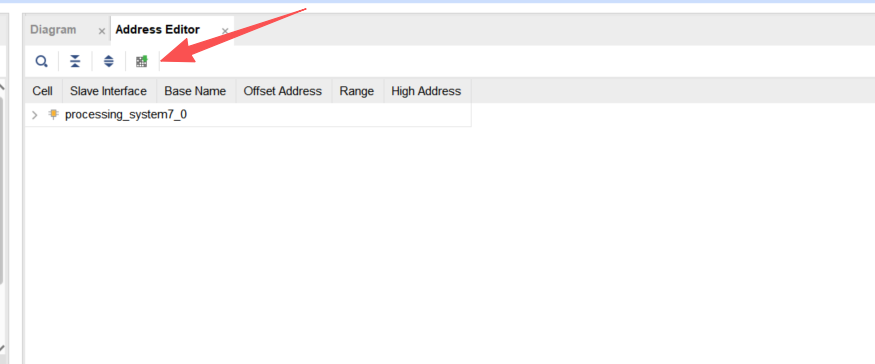

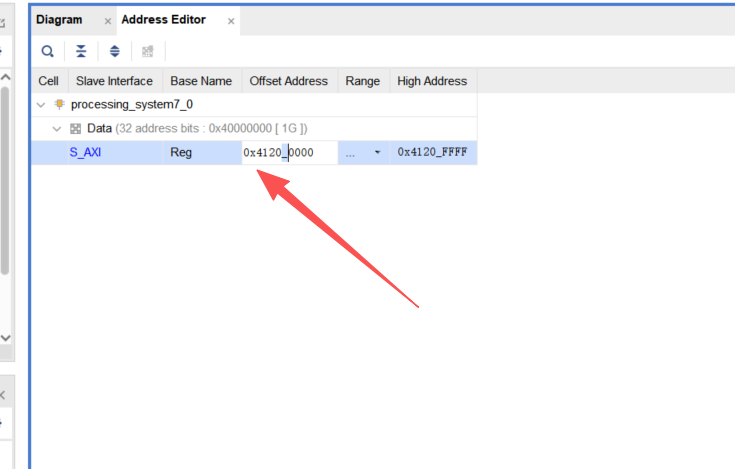

9.分配AXI总线的地址

自动分配地址值

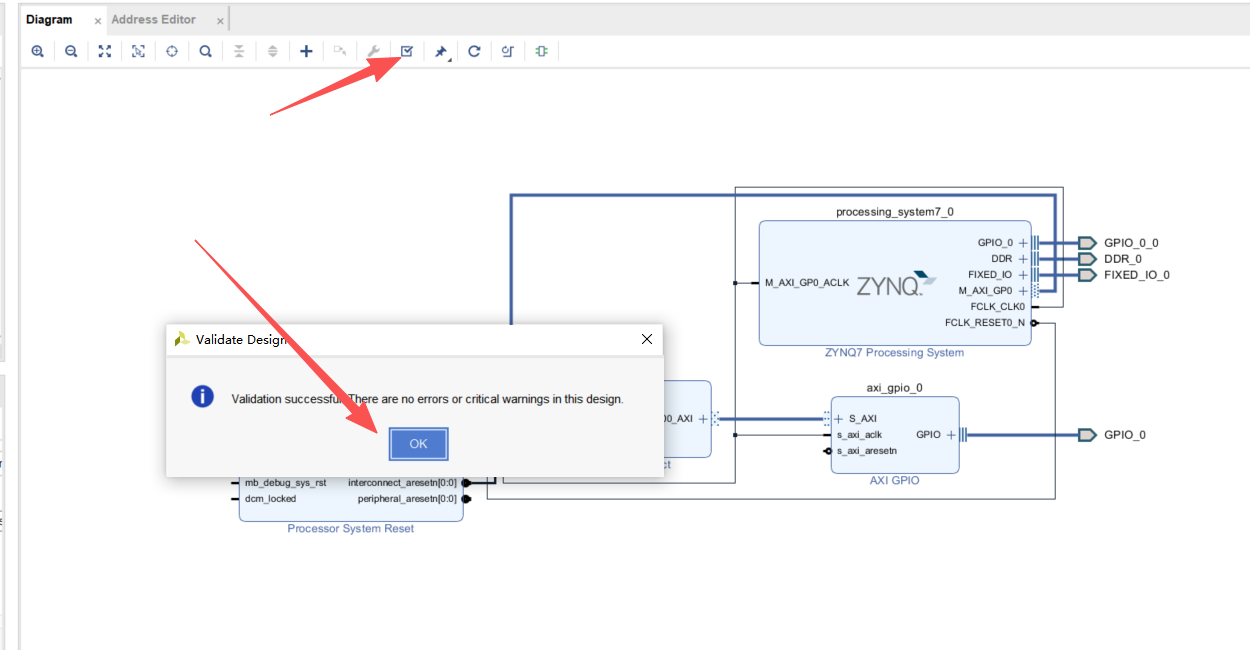

10报错检查

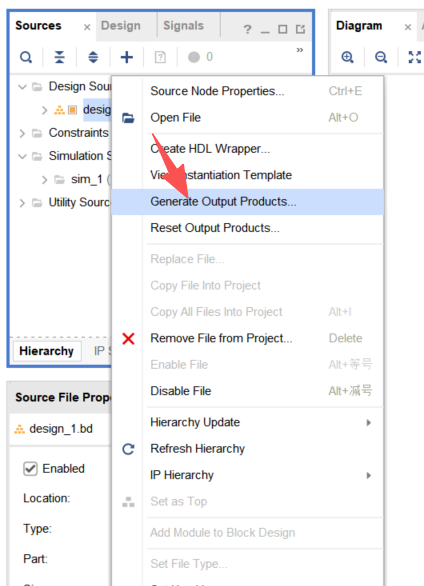

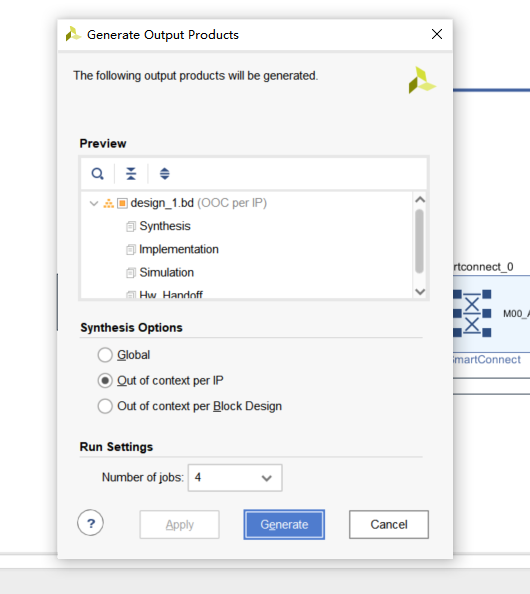

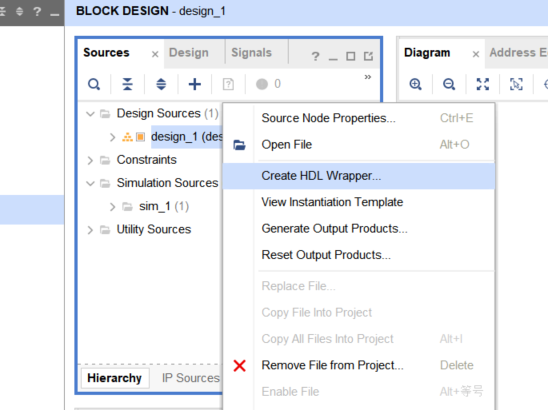

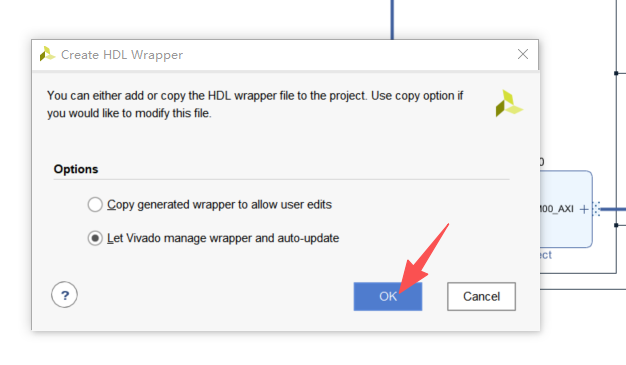

11,将bd输出并打包生成顶层

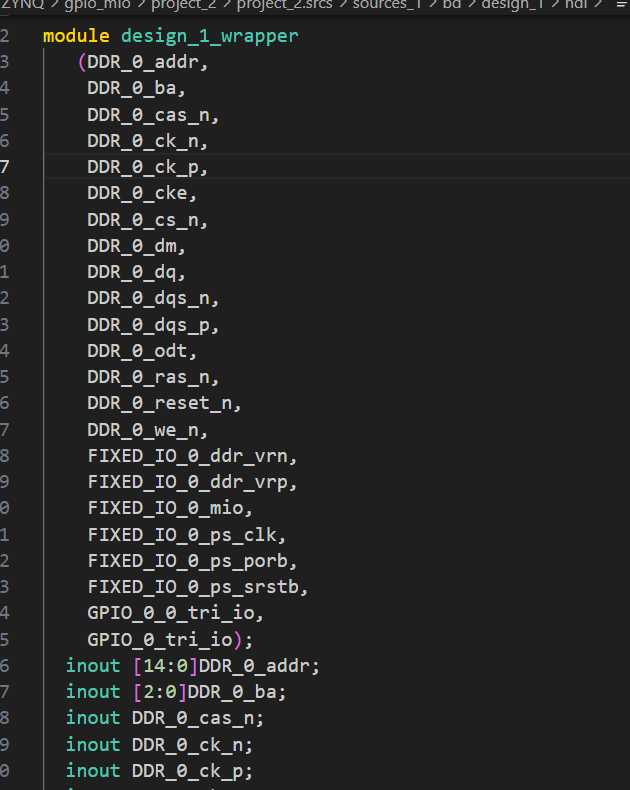

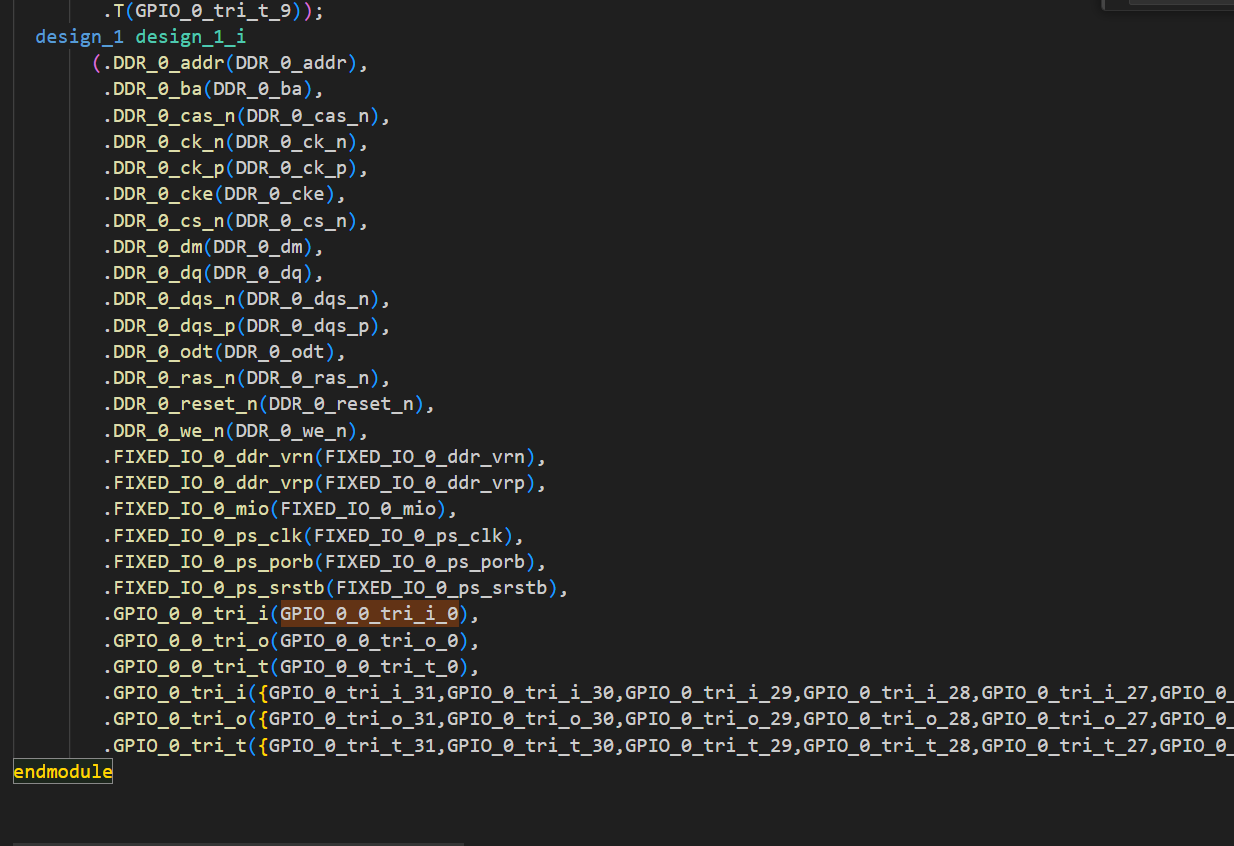

打包可以看到顶层

12打包代码

除了DDR以及DIXED的口其他都是PL侧的资源

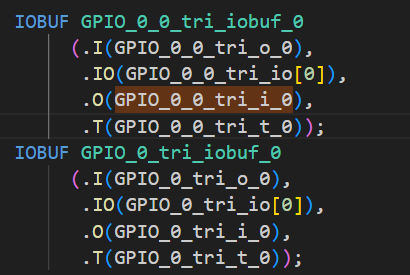

会看到iobuffer

IOBUF是什么