对于FPGA的验证方法根据设计阶段的不同,分为设计理论功能验证(称为前仿真或功能仿真)与实际实现的功能验证。

FPGA设计的仿真是使用专门的仿真工具,给设计好的模块输入一些激励信号,通过观察模块输出端口的值来判断输入的激励信号是否能产生正确的输出。

这里我们通过test bench来实现验证

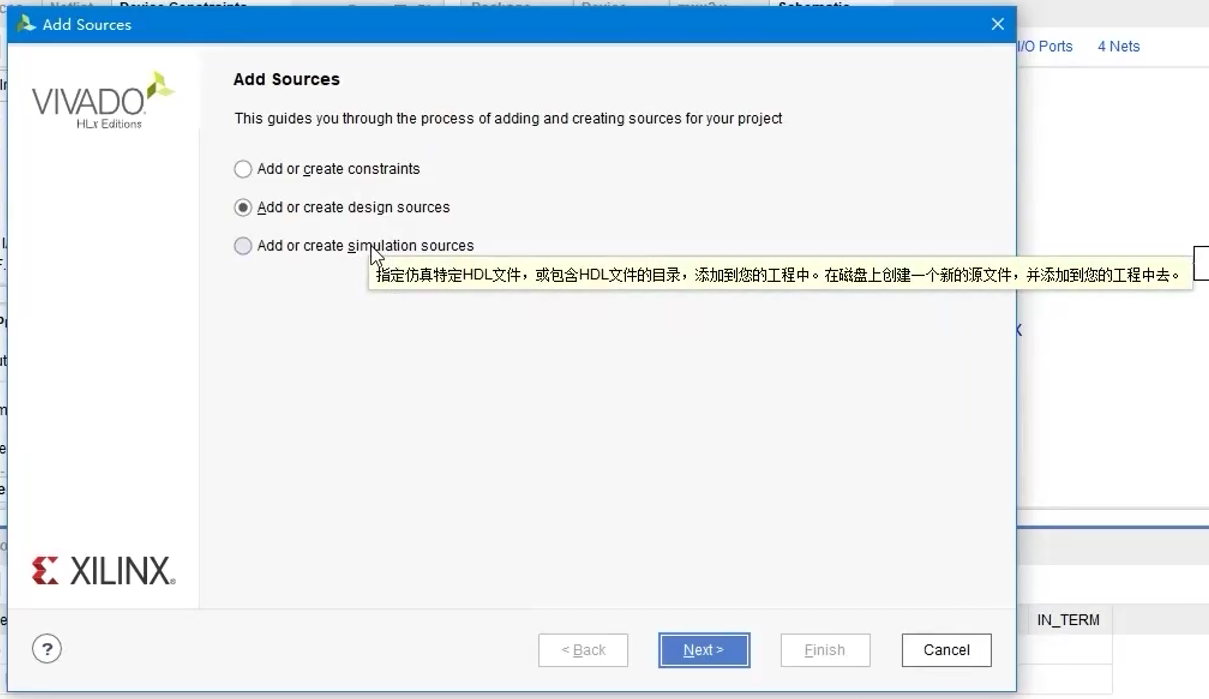

一、创建新文件

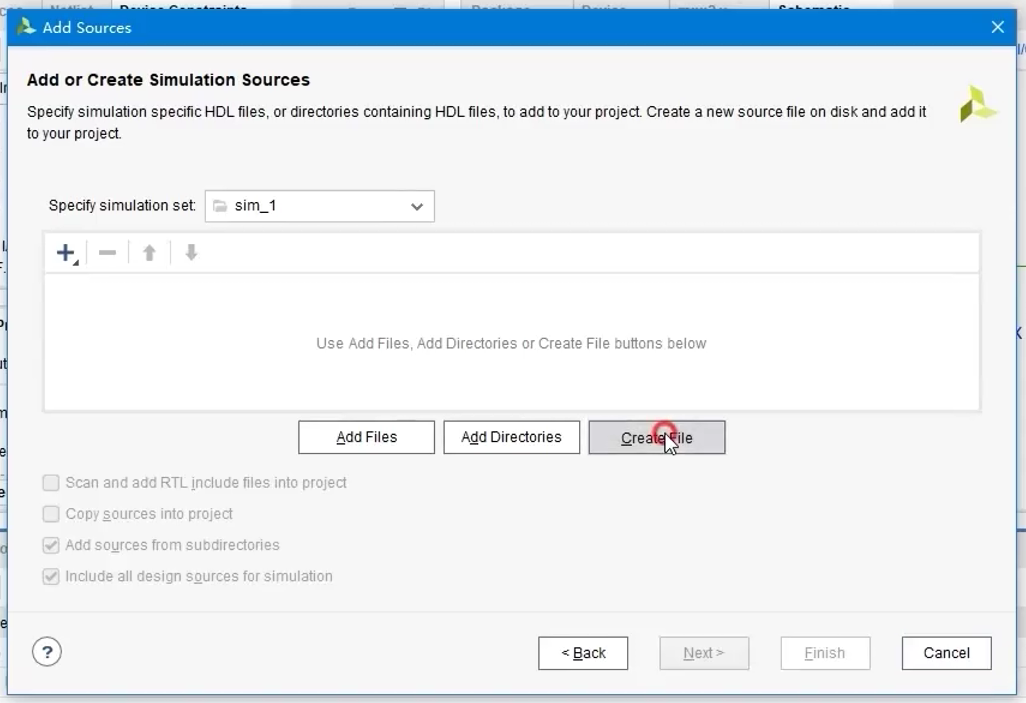

通过Alt+A打开Add Sources界面,这里选择第三个选项

通过这个选项创建的文件,Vivado软件不会将其用作设计文件去尝试综合成逻辑电路,只用在对设计文件进行仿真的时候。

进入到添加文件或新建文件的页面与上一节创建设计源文件的界面一样,仍然选择Create File创建新文件

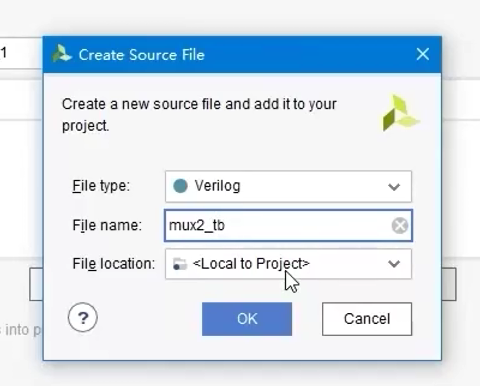

tb是test bench的缩写,用以说明该文件是仿真测试用的文件,注意使用的是下划线_

点击OK→Finish

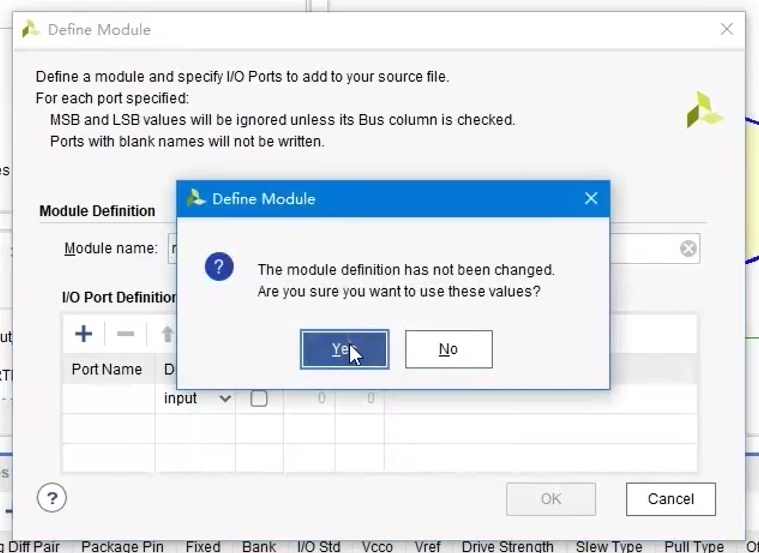

点击OK→Yes

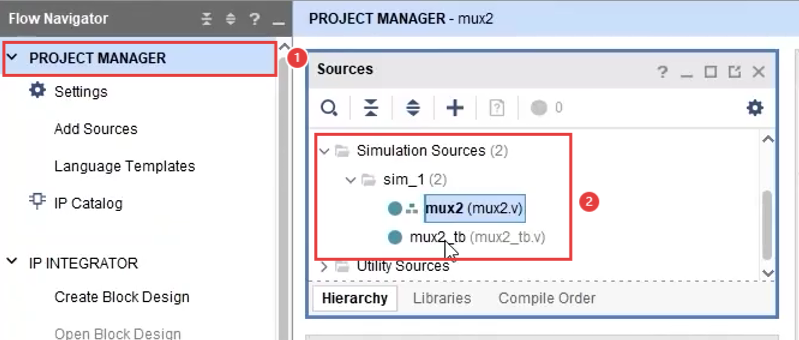

在Simulation Sources中可以看到新生成的两个文件

设计文件既可以生成逻辑电路,也可以用来仿真

二、程序编写

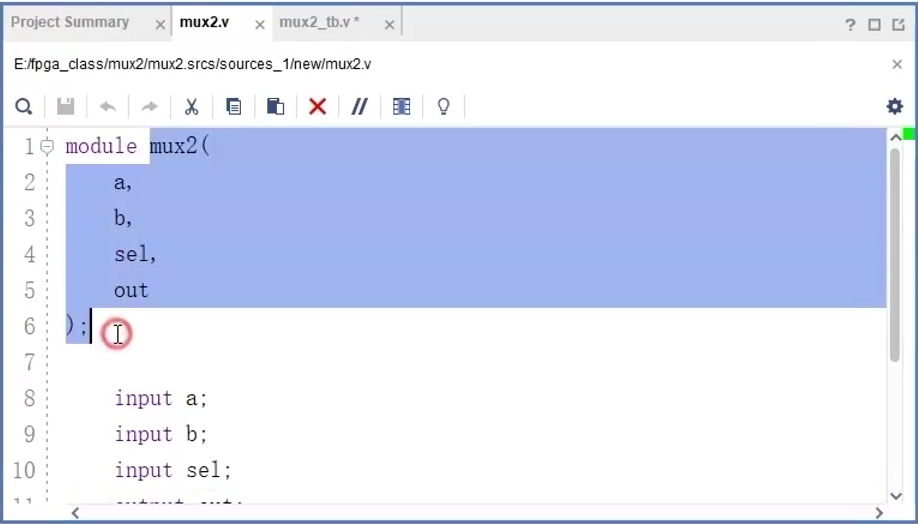

1.创建模块

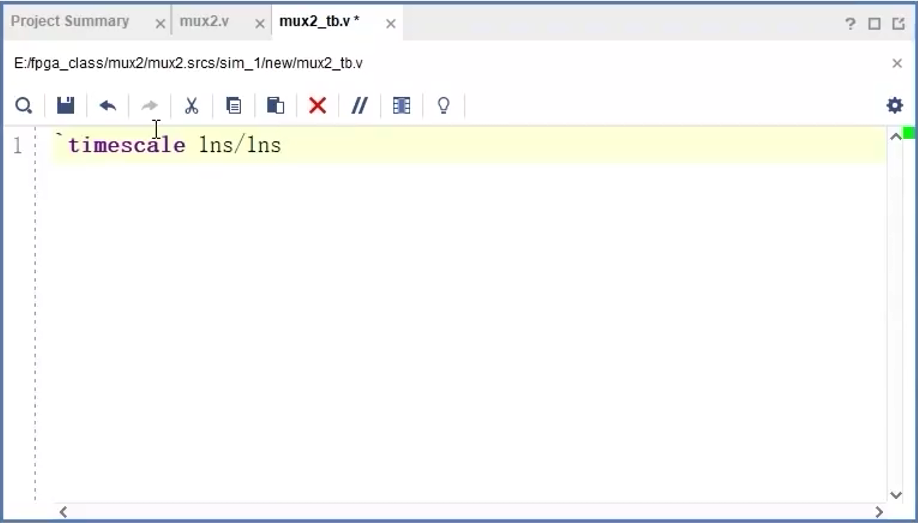

打开mux2_tb文件,将软件自动生成的所有内容删除

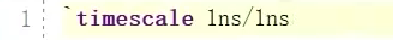

对于所有用来仿真的test bench文件,第一行代码永远是一样的

timescale是语法标准的保留词,有专门的作用,用来指定代码仿真时用到的延时语句的单位和精度

注意:代码开头的`是键盘左上角的`

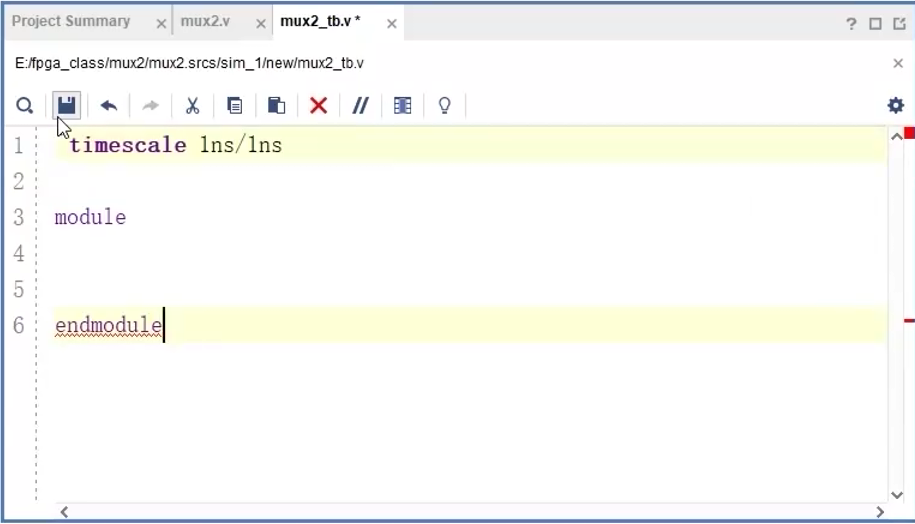

仿真软件也使用module和endmodule表示内容的开始和结束

2.模块声明

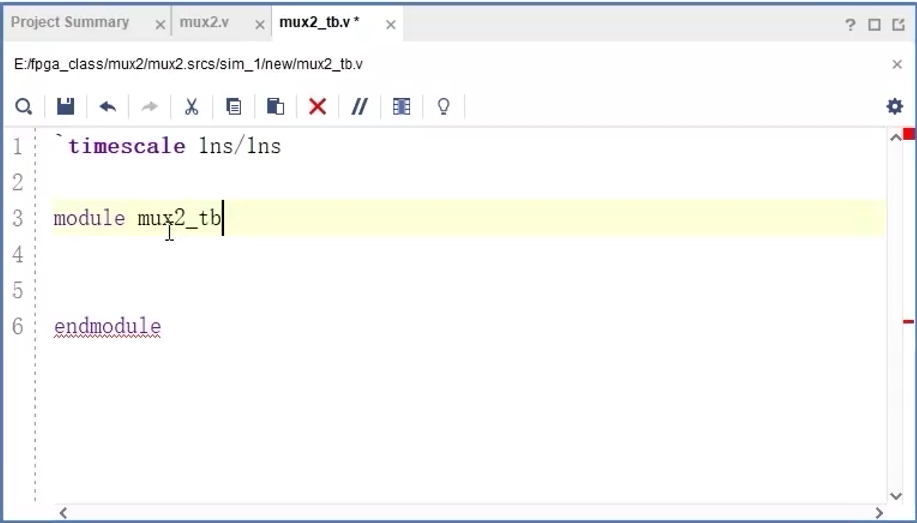

在module后写该仿真模块的名称,与文件名称保持一致

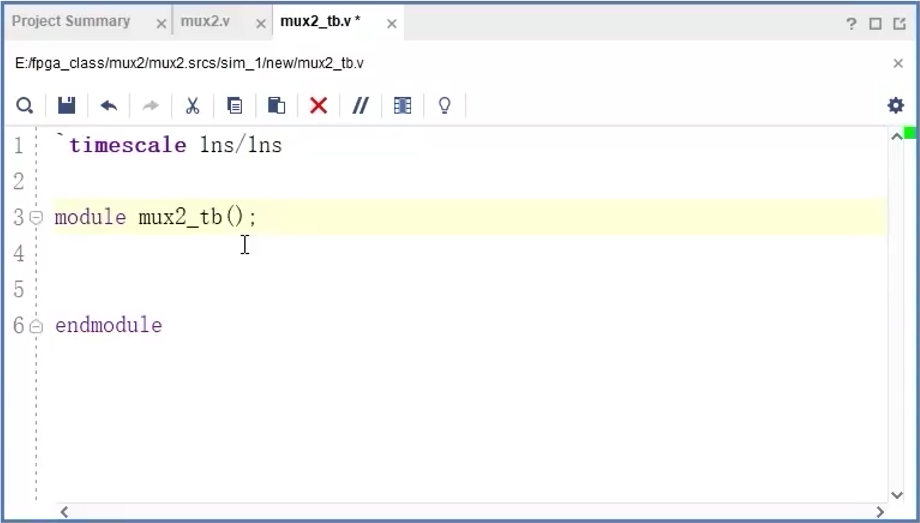

对于简单的测试文件来说不需要有端口信号,端口列表()中空着即可,()可以省略不写

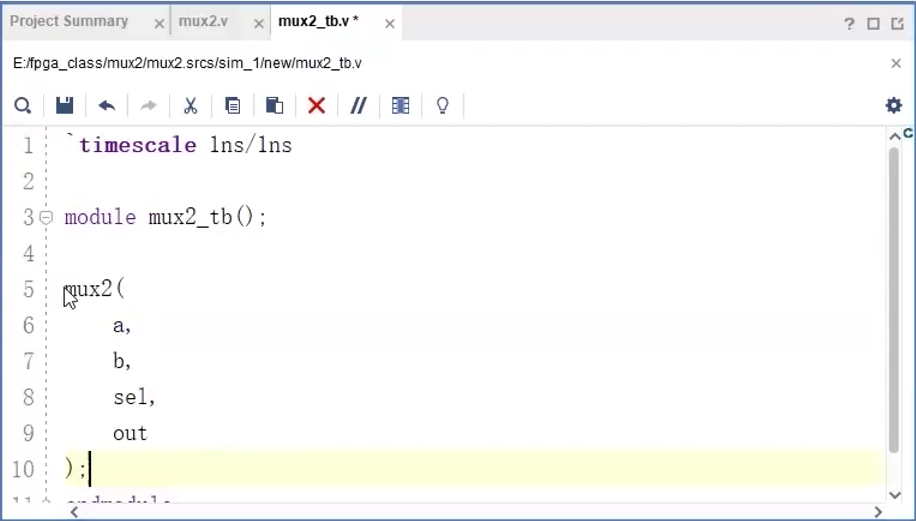

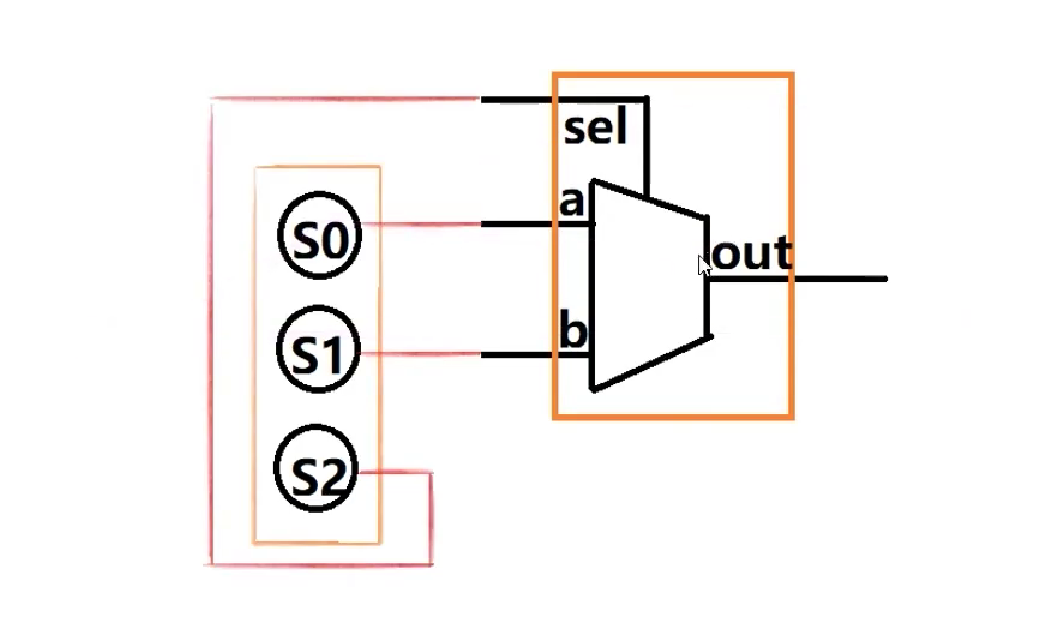

3.例化

首先要把设计好的被测试模块放到测试平台上,该过程称为例化

打开mux2文件,复制模块名称和端口列表

粘贴到mux2_tb文件中

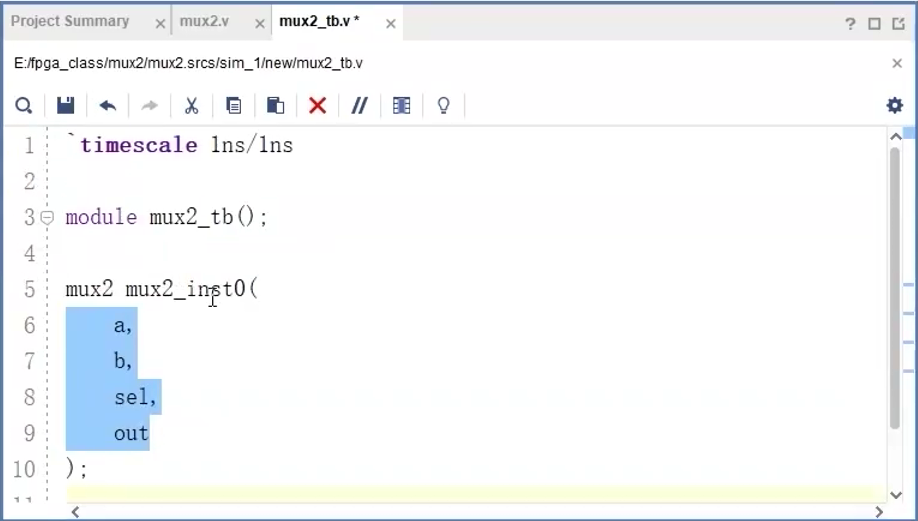

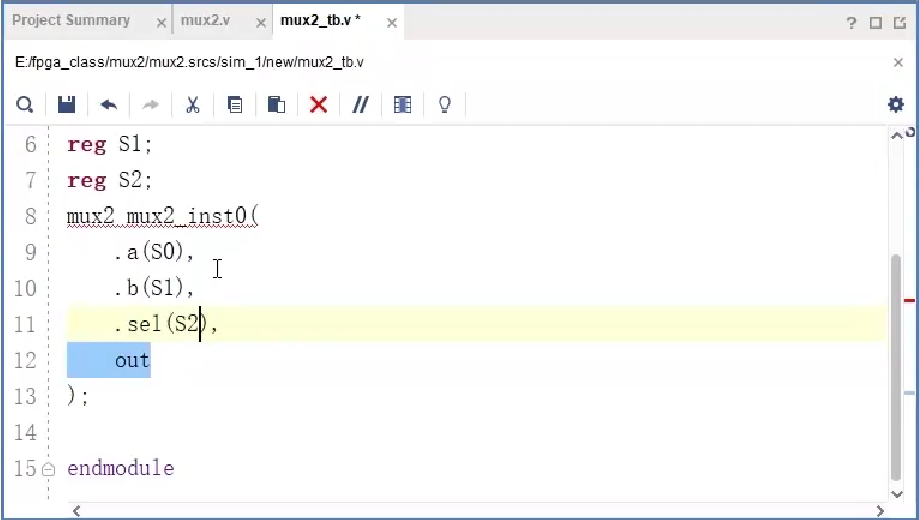

4.重新命名

在模块的名字后打一个空格,写一个新名字作为模块的标签

inst是例化的意思

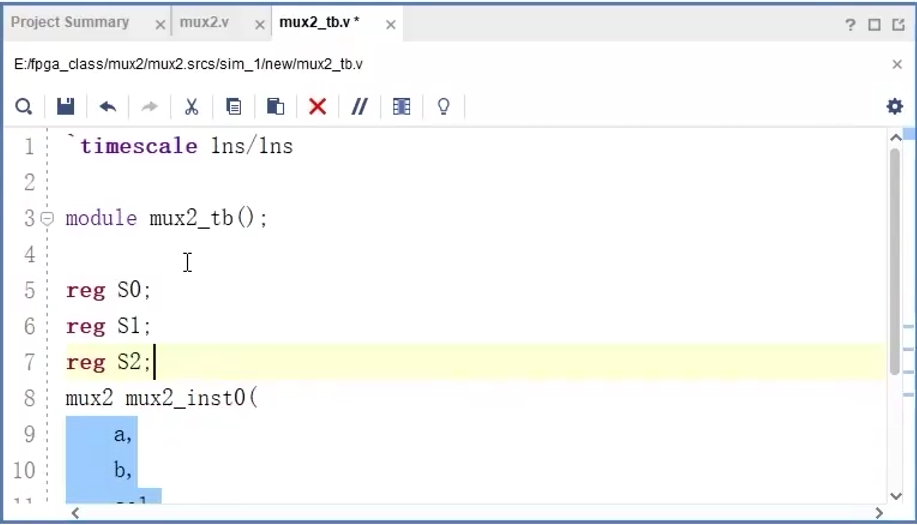

5.连接端口

在test bench中模拟信号发生器只需要写几个可以随意修改的信号名即可

这里的被测试模块mux2有三个端口,所以在测试平台即test bench中定义三个信号

对于需要随时修改值的信号需要使用关键词reg来定义

这就表示信号发生器有三个信号输出端口,现在要做的是将信号发生器的三个输出端口和被测试模块的三个输入端口进行连接

只需要在被测试模块需要连接的端口前面加上英文字符.代表准备例化,在后面跟一个括号(),相当于准备好了接线,将接线的端口写入括号中即可。

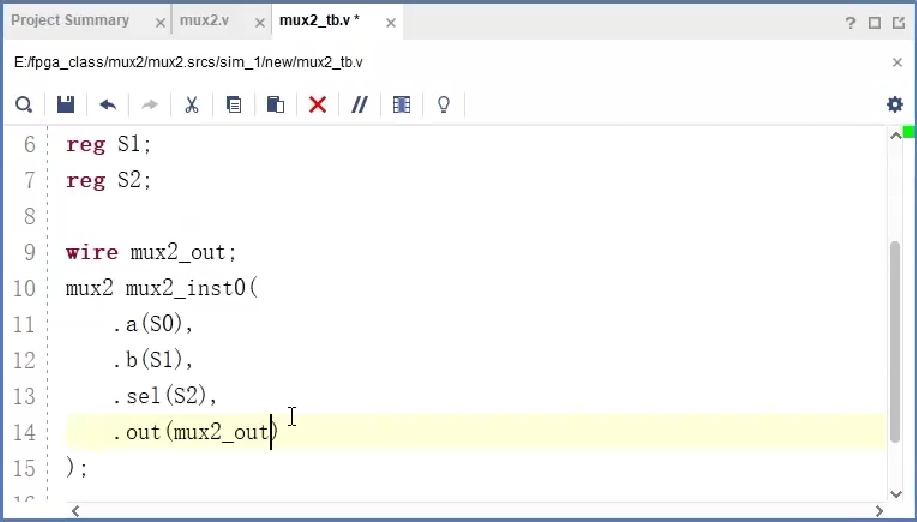

对于输出端口只需要在测试平台中放置一根导线,仿真软件就可以在仿真过程中自动检测导线上的电平状态,这种类型的导线用关键词wire进行声明,然后就可以将其与被测试端口进行连接。

至此,已经将被测试端口和激励源以及观测信号连接完成了。

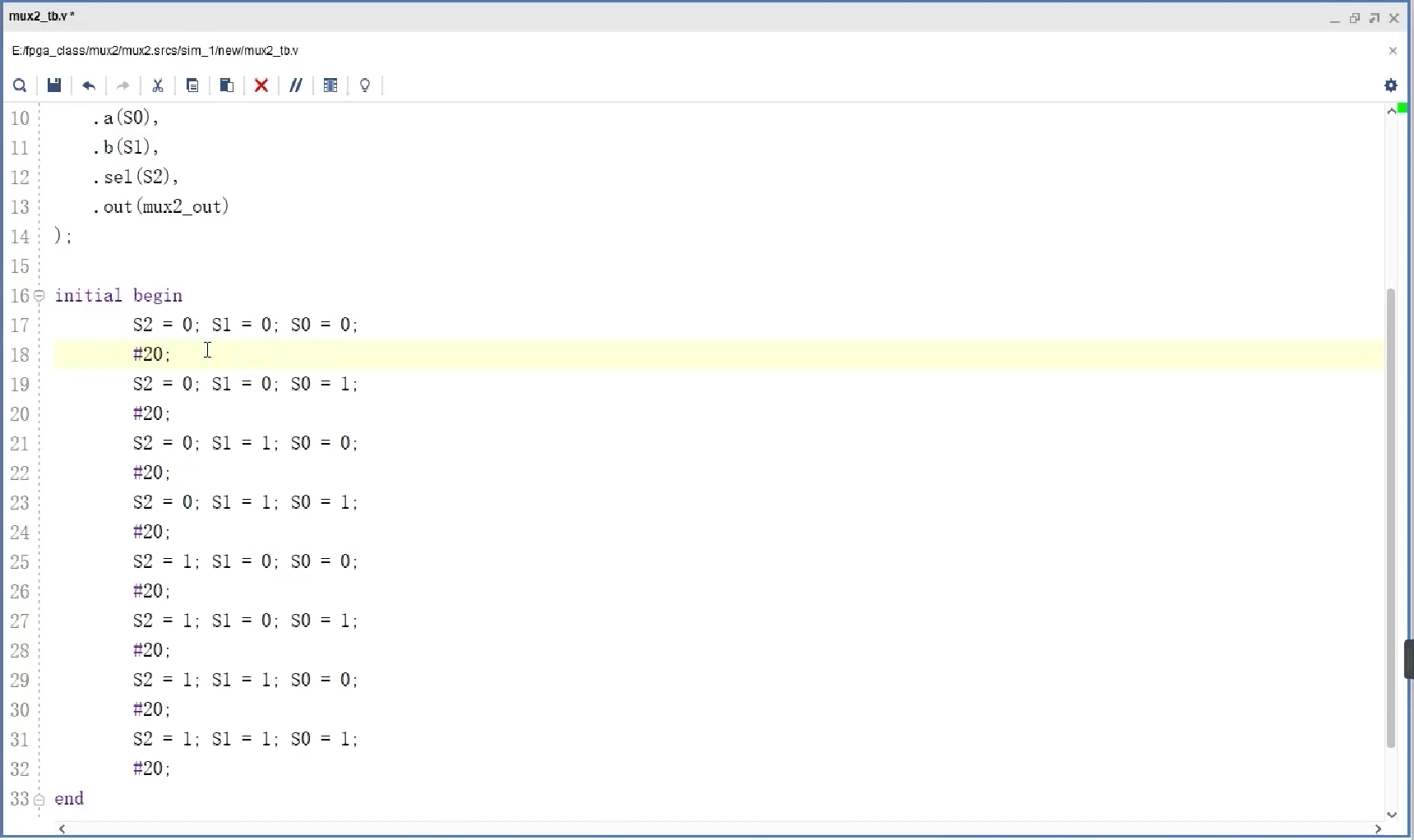

6.产生激励信号

该过程相当于给信号发生器编程,控制三个输出端口按照什么规律 在什么时候 输出什么电平信号

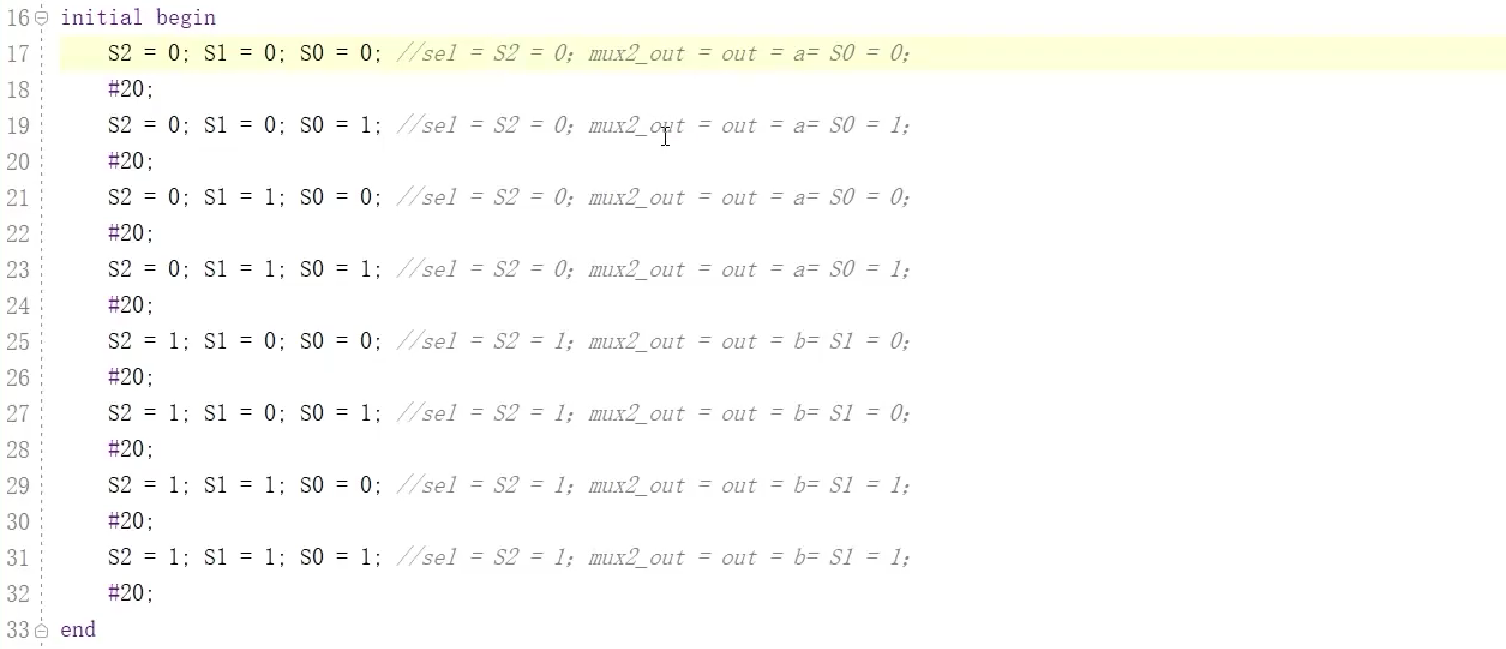

initial是快声明词,这个词后面一般会跟着一对单词:begin end 共同组成一个initial块

这个块描述的内容是从仿真的零时刻开始顺序往后逐句执行的

这里直接用等号进行赋值即可,不需要再写assign,每个语句用分号;隔开

#20代表在仿真的时间线上向后推移20ns,这里的单位ns与test bench文件开头的timescale定义的内容有关

斜线前的内容与延时的单位 有关,1ns/1ns时,#20表示延时20个1ns,10ns/1ns时,#20表示延时20个10ns

斜线后的内容与延时的精度 有关,代表每次延时的最小单位,若写成1ns/1ps,则后面就可以写成#20.1 #20.001等形式,也就是说若写为1ps,小数点后可以写三位

注意:这种语句仅用于仿真平台即test bench中,不支持被综合成逻辑电路,或者说FPGA中没有能实现内部信号传输延时的硬件资源结构

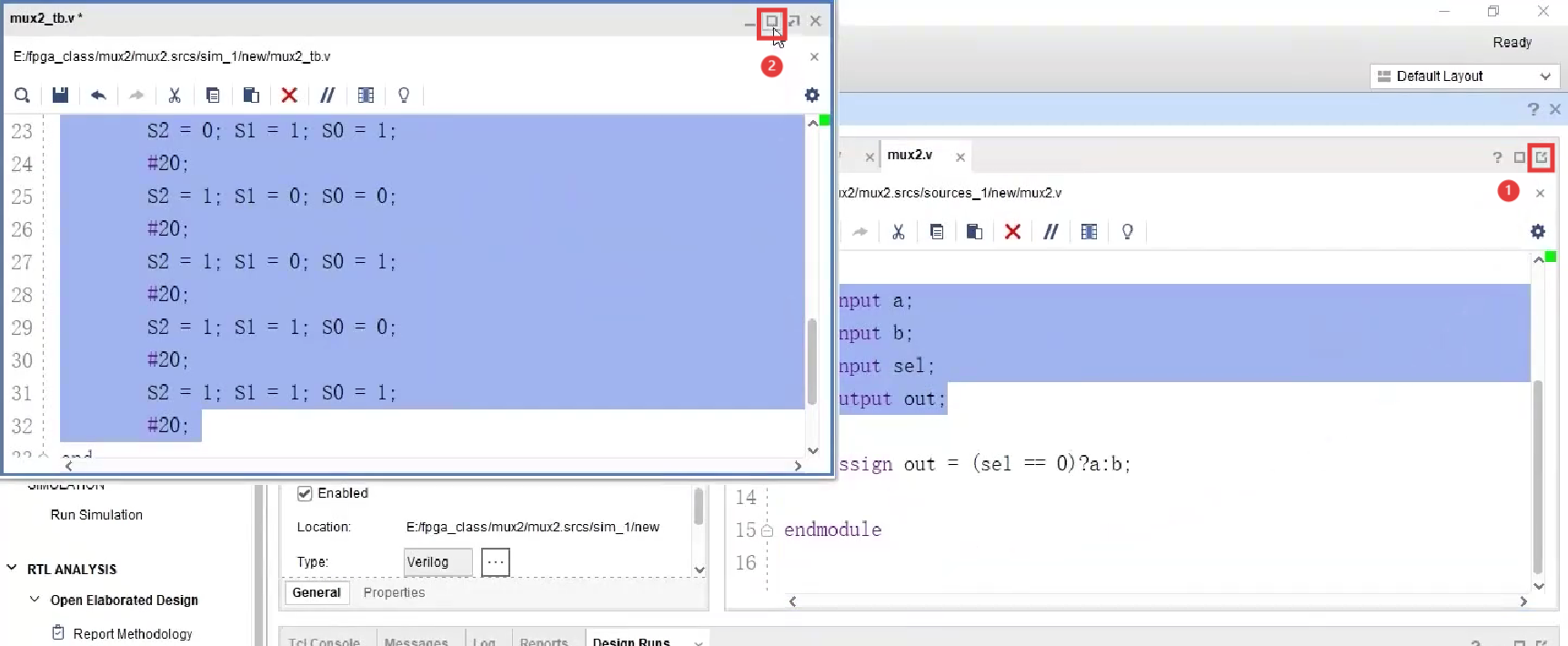

提示:按图所示步骤可以将变成的区域放大

三、仿真验证

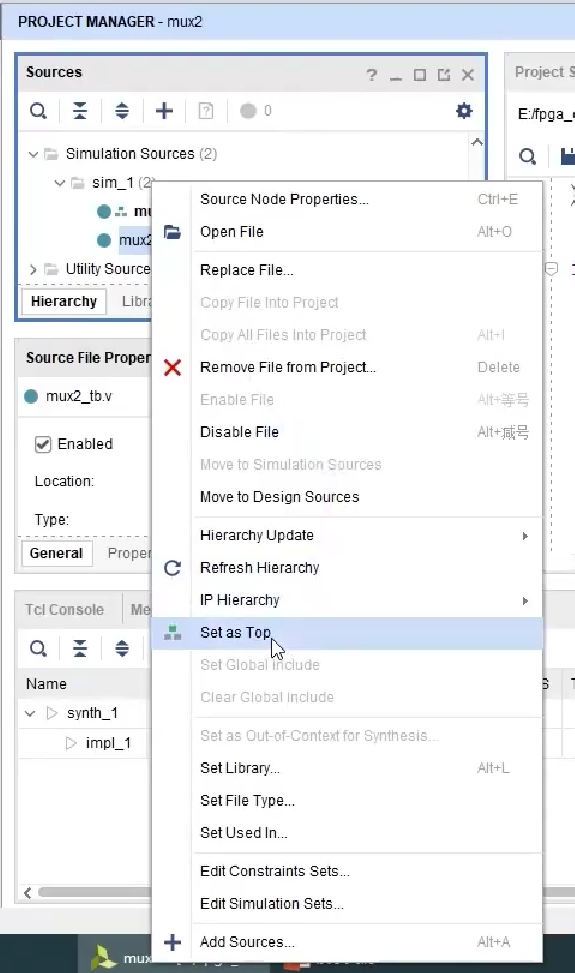

使用Vivado自带的软件进行仿真,需要将仿真文件mux2_tb设置成顶层文件才能进行仿真

选中仿真文件mux2_tb右键点击Set as Top

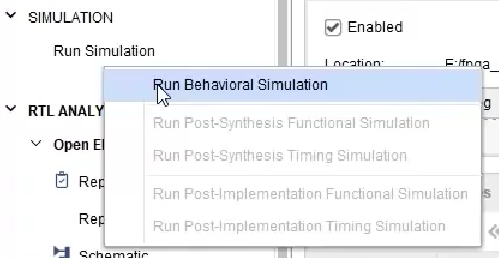

点击Run Simutation,在弹出的仿真类型中选择第一个

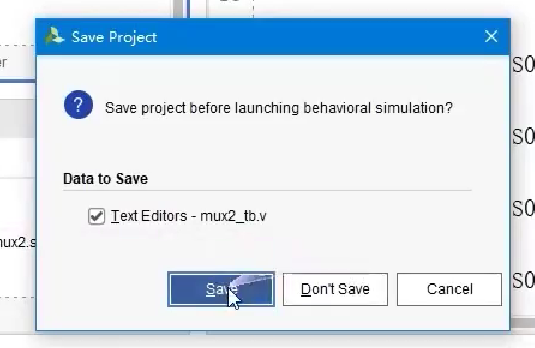

点击Save

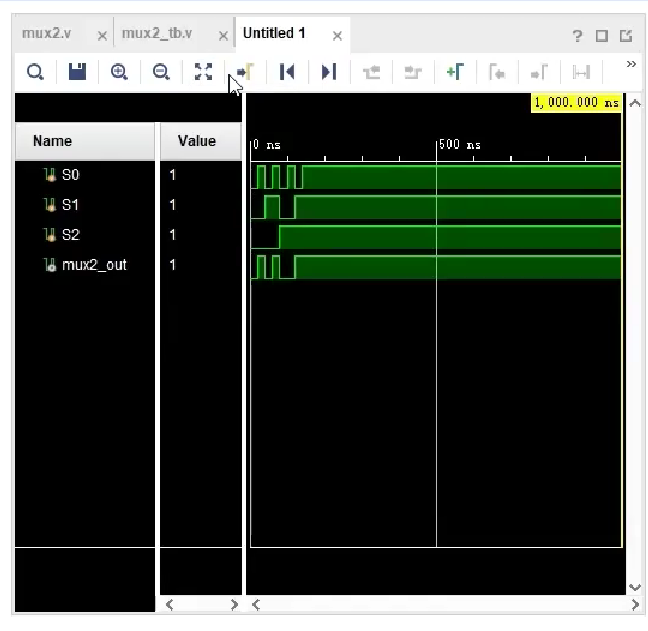

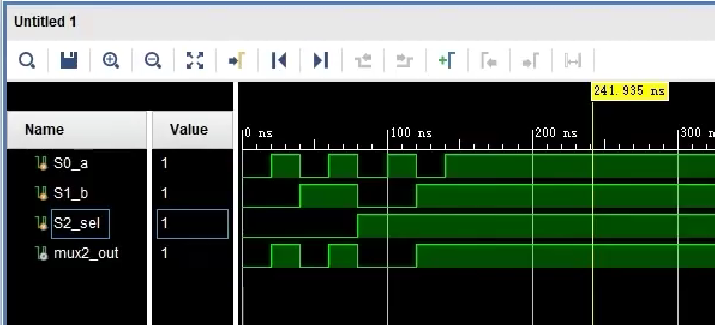

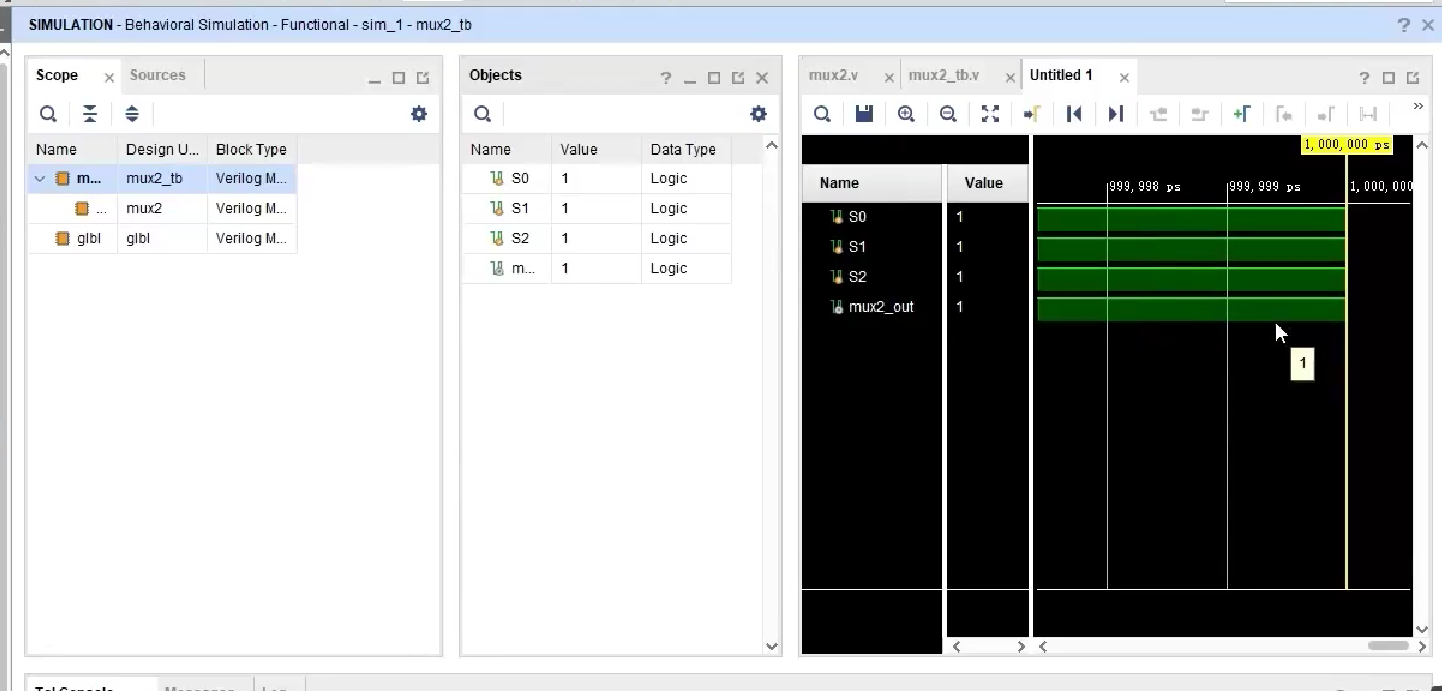

此时仿真工具会进入仿真波形的界面

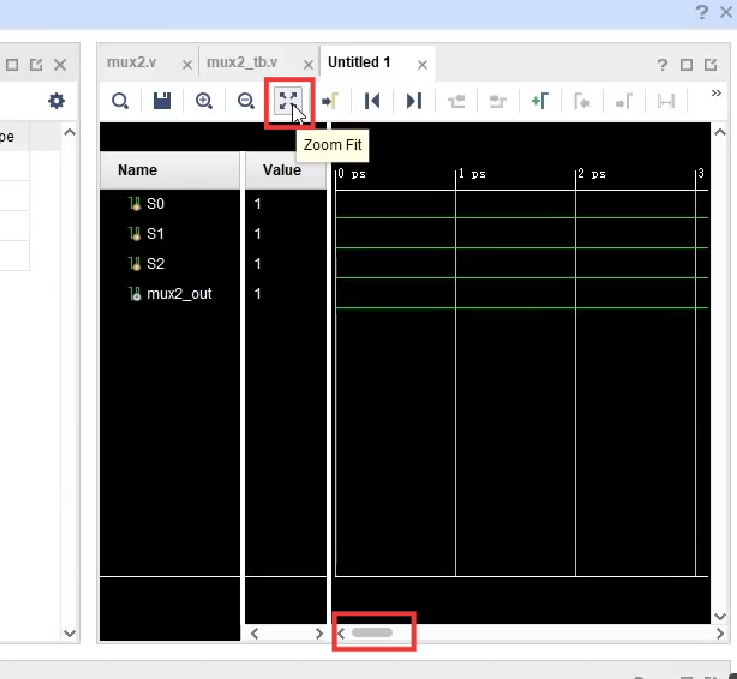

软件仿真完成后自动把波形放大到了最大的状态,所以只能看到上图所示的局部波形,将下面的滚动条拖到最左边,然后点击Zoom Fit

此时就可以看到完整的波形了,然后可以根据设计预期值进行简单的核对