发音:/ˈaikərəs/: n. [希神]伊卡洛斯(代达罗斯的儿子)安装

iverilog安装时,默认会把GTKWave一起安装,用于查看生成的波形图。安装地址:https://bleyer.org/icarus/

全平台可装,本文Win平台,随后在CMD中直接查阅iverilog, vvp, gtkwave是否安装成功

bash

C:\Users\wpyoung>where iverilog

C:\Users\wpyoung\AppData\Roaming\iverilog\bin\iverilog.exe

C:\Users\wpyoung>where vvp

C:\Users\wpyoung\AppData\Roaming\iverilog\bin\vvp.exe

C:\Users\wpyoung>where gtkwave

C:\Users\wpyoung\AppData\Roaming\iverilog\gtkwave\bin\gtkwave.exeiverilog:用于编译verilog和vhdl文件,进行语法检查,生成可执行文件

vvp:根据可执行文件,生成仿真波形文件

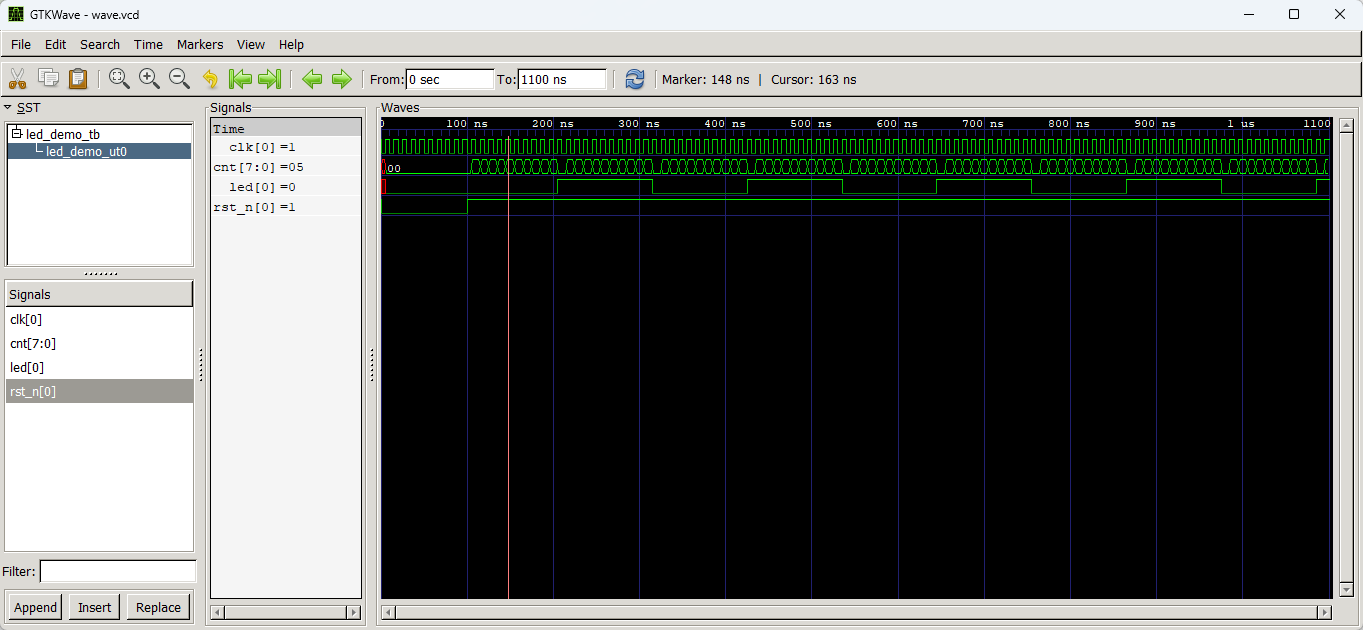

gtkwave:用于打开仿真波形文件,图形化显示波形

Icarus参数

- -o,指定生成文件的名称。如不指定,默认生成为a.out。如:iverilog -o test test.v

- -y,包含指定文件夹,iverilog -y E:/pro/demo demo_tb.v

- -I,(大写i)头文件包含(`include),用法与-y同

用法查询,输入iverilog即可

shelll

C:\Users\wpyoung>iverilog

iverilog: no source files.

Usage: iverilog [-EiSuvV] [-B base] [-c cmdfile|-f cmdfile]

[-g1995|-g2001|-g2005|-g2005-sv|-g2009|-g2012] [-g<feature>]

[-D macro[=defn]] [-I includedir] [-L moduledir]

[-M [mode=]depfile] [-m module]

[-N file] [-o filename] [-p flag=value]

[-s topmodule] [-t target] [-T min|typ|max]

[-W class] [-y dir] [-Y suf] [-l file] source_file(s)

See the man page for details.Verilog文件格式和函数

- VCD文件是记录各种信号取值变化情况的信息记录文件。EDA工具通过读取VCD格式的文件,显示图形化的仿真波形,所以,可以把VCD文件简单地视为波形记录文件。

$dumpfile ("wave.vcd"); //仿真信息将记录到wave.vcd$dumpvar(level, module_name); level用于指定层次数,module则指定要记录的模块。对于指定的模块,包括其下各个层次的信号,都需要记录到VCD文件中去。$dumpvar表示记录所有的信号文件。

仿真

iverilog -o wave led_demo_tb.v得到wave

shell

PS E:\weip_vgg_Noc\pro_hdl_icarus> iverilog -o wave led_demo_tb.v led_demo.vvvp -n wave -lxt2得到vcd文件

shell

PS E:\weip_vgg_Noc\pro_hdl_icarus> vvp -n wave -lxt2

LXT2 info: dumpfile wave.vcd opened for output.

led_demo_tb.v:29: $stop called at 11000 (100ps)- gtkwave打开仿真文件

gtkwave wave.vcd

脚本

Windows系统保存为.bat文件,Linux系统保存为.sh文件。Windows直接双击运行,Linux在终端执行

shell

echo "开始编译"

iverilog -o wave led_demo.v led_demo_tb.v

echo "编译完成"

vvp -n wave -lxt2

echo "生成波形文件"

cp wave.vcd wave.lxt

echo "打开波形文件"

gtkwave wave.lxt