一、数字阵列雷达概念

数字阵列雷达(DAR)是一种以"天线阵元级数字化"为核心特征的全数字化相控阵雷达系统。其本质是通过在雷达天线阵列的每个阵元(或每路子通道)后直接集成模数转换器(ADC)、数模转换器(DAC)及数字信号处理模块,实现对射频信号的发射与接收过程的全数字化控制。

与传统模拟相控阵雷达(Analog Phased Array Radar, APAR)相比,数字阵列雷达的核心差异在于波束形成的数字化层级:模拟相控阵仅在射频/中频阶段通过移相器、衰减器等模拟器件实现波束控制,而数字阵列雷达则将波束形成过程转移至数字域,通过数字加权算法(幅度、相位调控)直接生成高精度波束,从而实现对雷达性能的根本性提升。

二、数字阵列雷达的系统组成

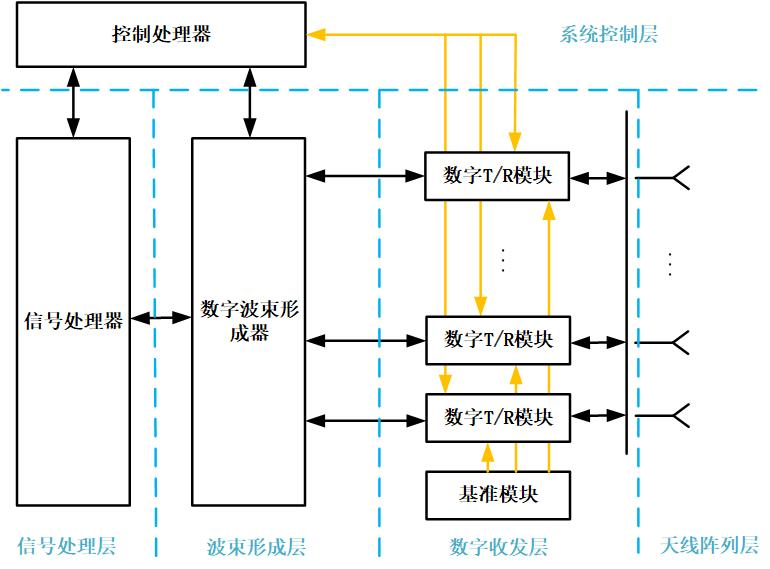

如图1所示,数字阵列雷达的系统架构可分为天线阵列层、数字收发层、波束形成层、信号处理层及系统控制层五个核心层级,各层级高度集成且协同工作,共同实现雷达的探测、跟踪与数据处理功能。

图1 数字阵列雷达简易结构框图

1.天线阵列层

作为雷达与空间电磁信号交互的接口,天线阵列层由大量独立的辐射阵元组成(如微带贴片阵元、波导阵元等),阵元排列方式可根据应用需求设计为直线阵、平面阵或共形阵。与传统雷达不同,数字阵列雷达的阵元通常具有"收发一体"功能,且每个阵元(或每路子阵)对应独立的数字收发通道,确保信号的独立数字化处理。

2.数字收发层

数字收发层是数字阵列雷达的"核心硬件载体",负责实现射频信号与数字信号的双向转换,每路通道均包含以下关键模块:

发射链路:由数字信号处理器(DSP)/现场可编程门阵列(FPGA)生成的数字基带信号,经数模转换器(DAC)转换为模拟中频信号,再通过上变频器(Up-converter)搬移至射频频段,最后经功率放大器(PA)放大后馈送至天线阵元辐射;

接收链路:天线阵元接收的射频信号经低噪声放大器(LNA)放大后,由下变频器(Down-converter)搬移至中频,再通过模数转换器(ADC)转换为数字信号,送入后续数字处理模块;

校准模块:集成内置校准通道,通过注入标准校准信号,实时补偿通道间的幅度、相位不一致性,确保阵列性能稳定性。

3.波束形成层

波束形成层是数字阵列雷达的"核心算法载体",通过数字信号处理技术实现波束的生成与调控,分为发射波束形成与接收波束形成两部分:

发射波束形成:通过DDS或FPGA对各通道的数字基带信号施加精确的幅度与相位加权,生成指向特定方向的相干信号,经DAC转换后辐射至空间,实现高增益定向发射;

接收波束形成:对各通道的数字信号进行加权合成,形成指向目标的接收主波束,同时在干扰方向形成零点,抑制电磁干扰,提升目标检测能力。

4.信号处理层

信号处理层负责对波束形成后的数字信号进行高阶处理,核心功能包括:

目标检测:通过脉冲压缩、恒虚警率(CFAR)检测等算法,从噪声中提取目标信号;

参数估计:计算目标的距离、速度、方位角、俯仰角等运动参数;

多目标跟踪:采用卡尔曼滤波、粒子滤波等算法,实现对多个目标的稳定跟踪;

抗干扰处理:通过自适应波束形成(ABF)、空时自适应处理(STAP)等算法,抑制有源干扰与杂波干扰。

5.系统控制层

系统控制层作为雷达的"中枢神经",通过主控计算机实现对全系统的协同控制,包括:

波束调度:根据任务需求动态规划波束指向、扫描模式与驻留时间;

参数配置:实时调整发射功率、信号带宽、脉冲重复频率(PRF)等雷达参数;

状态监测:监控各模块的工作状态,实现故障诊断与冗余备份;

数据交互:与外部指挥控制系统(C4ISR)进行数据传输与指令交互。