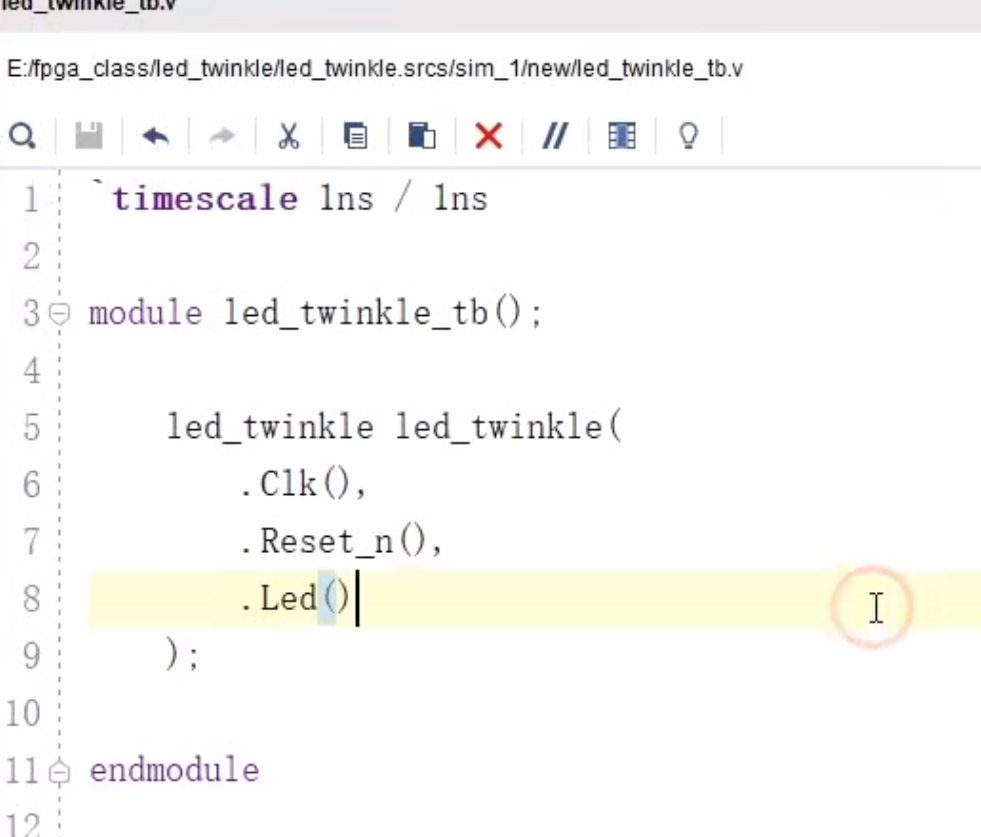

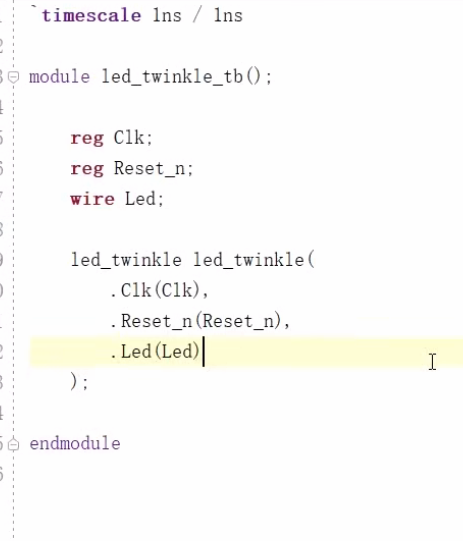

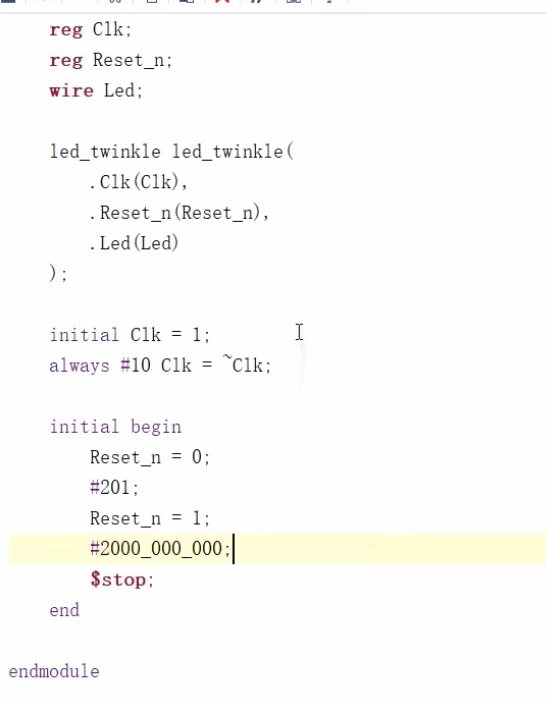

一、新建tb文件

进行例化

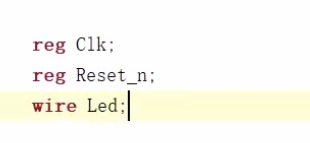

定义输入信号和输出信号

将输入信号与被测试模块连接到一起

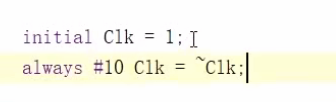

定义时钟信号

含义是定义clk为高电平,延时10纳秒后取反

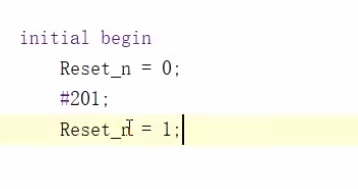

定义复位信号

先通过复位将D触发器设置为零,在仿真时间线上往后推移201ns,多等一纳秒是为了避免与时钟信号产生冲突从而无法理解波形

再将reset_n信号拉高

设计led每500ms翻转一次,所以至少一秒钟以上才能看到现象

仿真两秒观察实验现象

保存

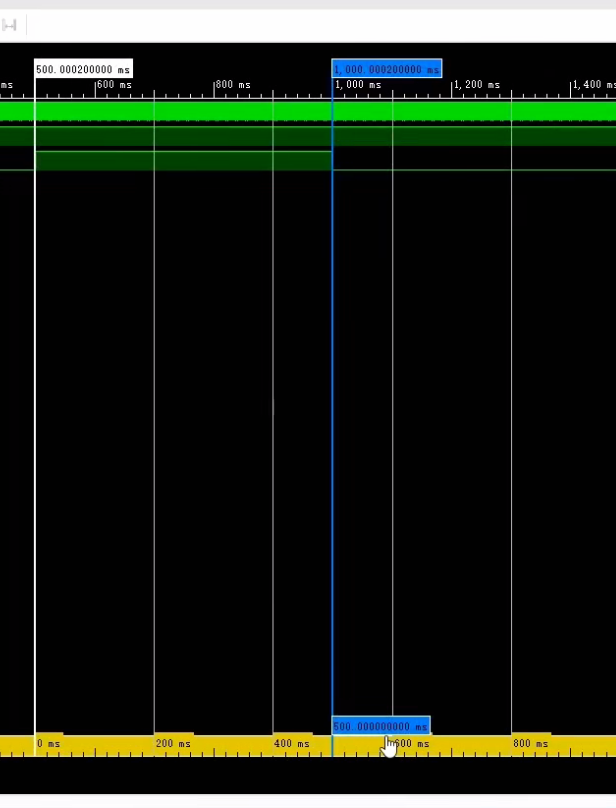

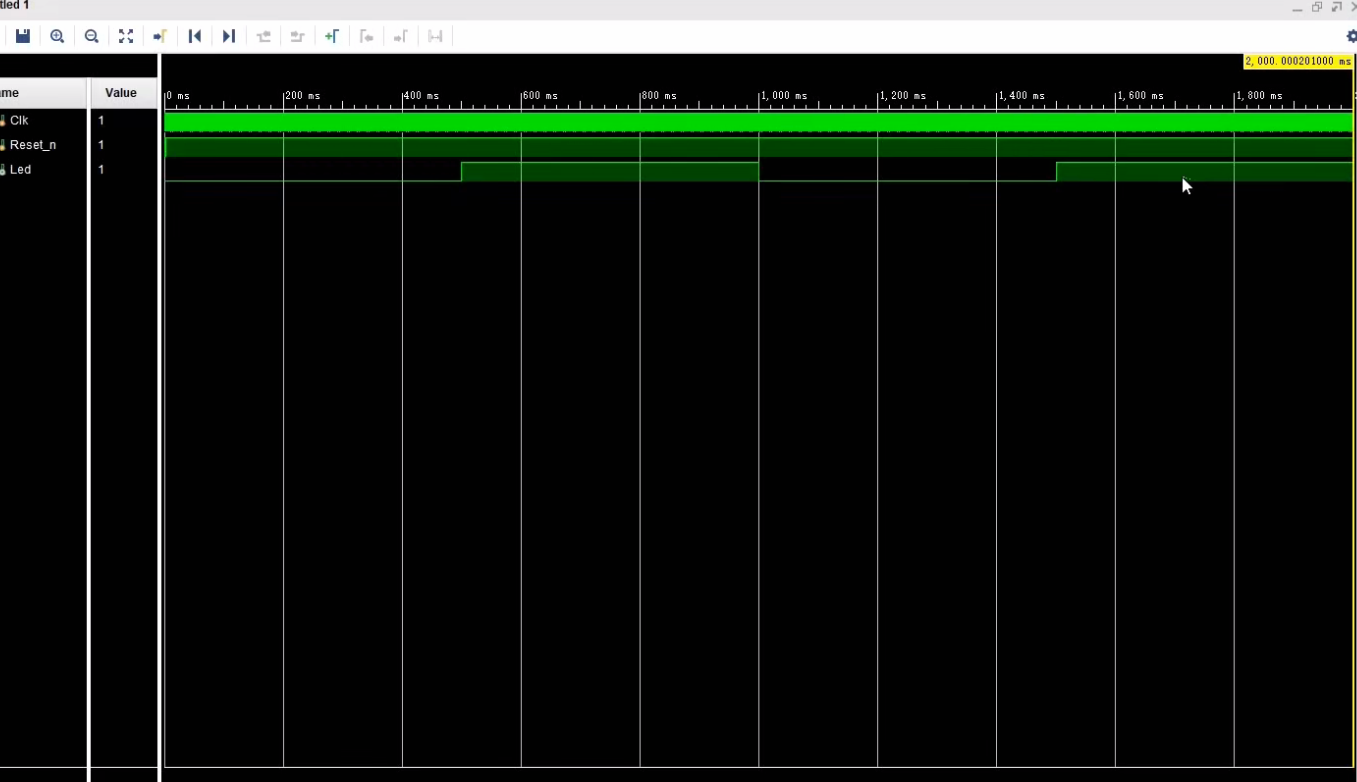

二、仿真波形

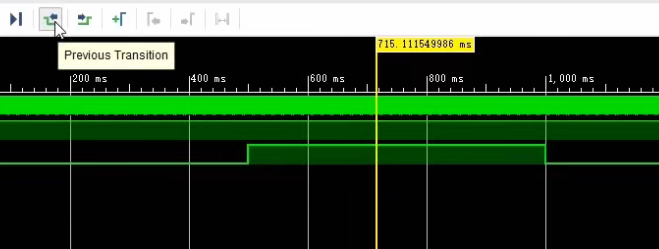

可以看到高低电平翻转

可以看到高低电平翻转

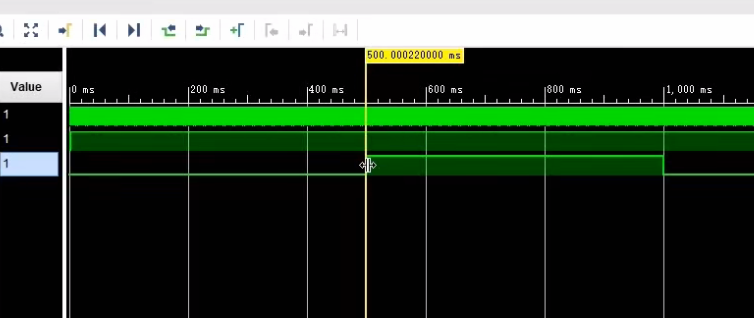

看时序电路还要看仿真时间是否正确

拖动黄色光标,点击这个按钮,光标就自动吸附到了第一个上升沿

点击这个图标, ,会添加标记,可以右键删除标记

,会添加标记,可以右键删除标记

点击这个按钮, ,光标会到左边的位置,因此

,光标会到左边的位置,因此 ,两边同时添加光标

,两边同时添加光标

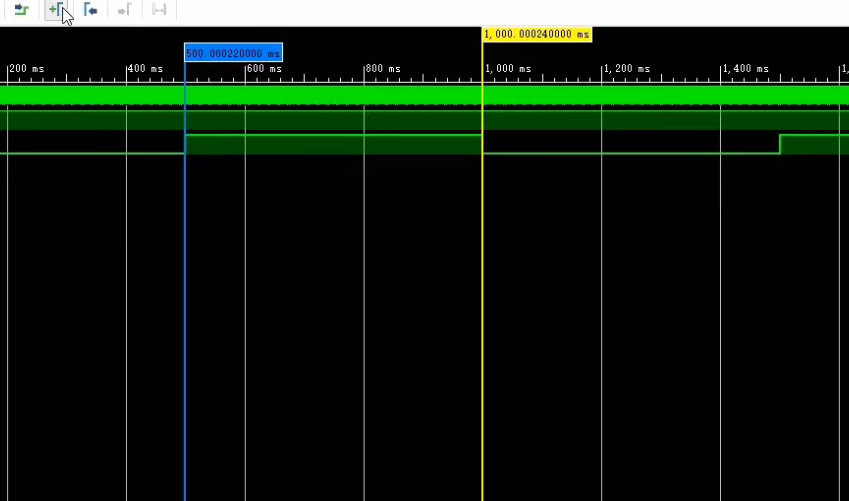

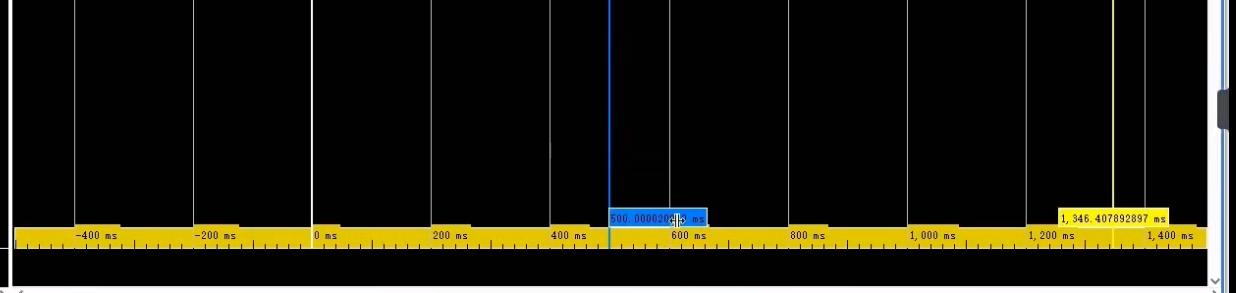

选择第一个蓝线,可以看到下面出现了蓝色的时间点,这就是两个蓝线之间的时间间隔

这个时间还多了20ns,是clk的时间,这个计数器从最大值25000000变为零也要消耗一个时钟周期的时间

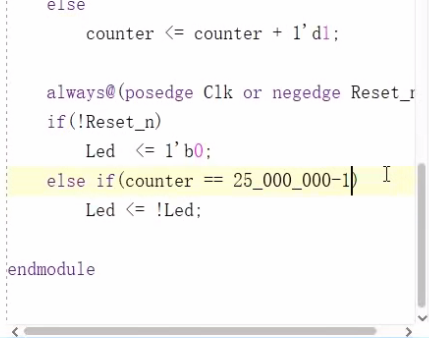

因此,只需在最大值处减一就可以调整过来了

可以看到修改后的值就是500ns