本文参考《锁相环技术原理及FPGA实现》杜勇这本书

- 1.锁相环综述

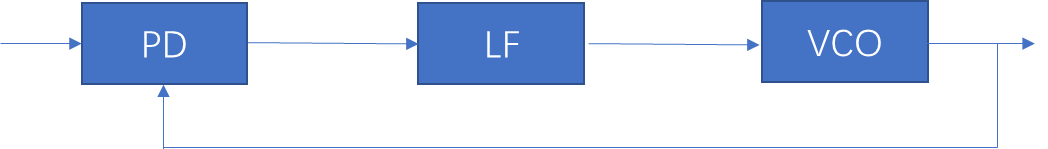

锁相环一般分为三部分,鉴相器、环路滤波器和电压振荡器。其中环路滤波器是决定锁相环的性能的重要器件,设计比较复杂,所以先搞明白鉴相器和电压振荡器,再说环路滤波器,整体来看。

- 1.2一阶环简化

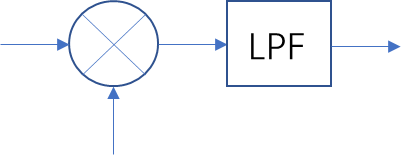

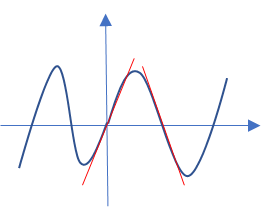

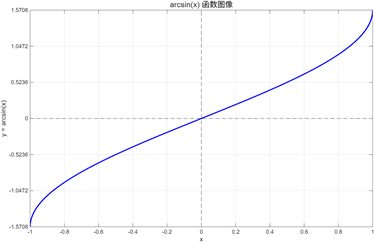

由鉴相器和电压振荡器可以组成一阶环路。鉴相器由混频器和低通滤波器组成,主要使用的是鉴相器成线性这一段函数,给到锁相环一个增益Kd。

电压振荡器是一个积分器的作用,在我们数字系统中更常知道的是NCO,数字振荡器,一个简单的数字振荡器的实现是查表法,把所有的值放在一个table里面,相应高级一些的是Cordic算法。

NCO输出的值是按照比例分散在[-pi,pi]或者说[0,2*pi]这个周期中,比如说一个NCO的位数是8位,我的频率控制字是M位,那形成的频率是f=2^M*fclk/2^8,在整个区间进行映射。

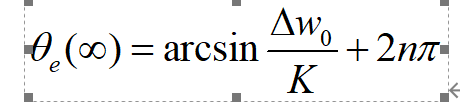

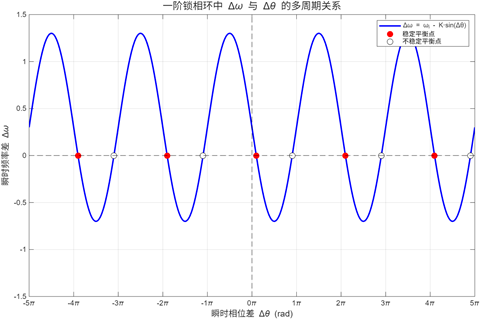

以鉴相器和NCO组成的一阶锁相环,我们可以推导出稳态相位误差:

1.3环路滤波器

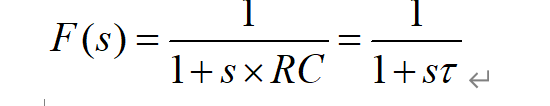

最简单的环路滤波器-RC滤波器

RC低通滤波器的频率特性

RC低通滤波器会产生超前的相位,降低相位裕度,不利于环路的稳定,所以考虑无源比例积分滤波器和有源比例积分滤波器。

无源比例积分滤波器的稳态相位误差不太好

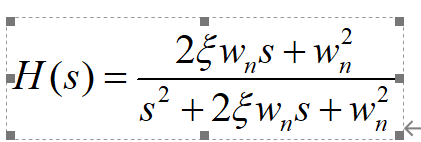

之后考虑有源比例积分滤波器,

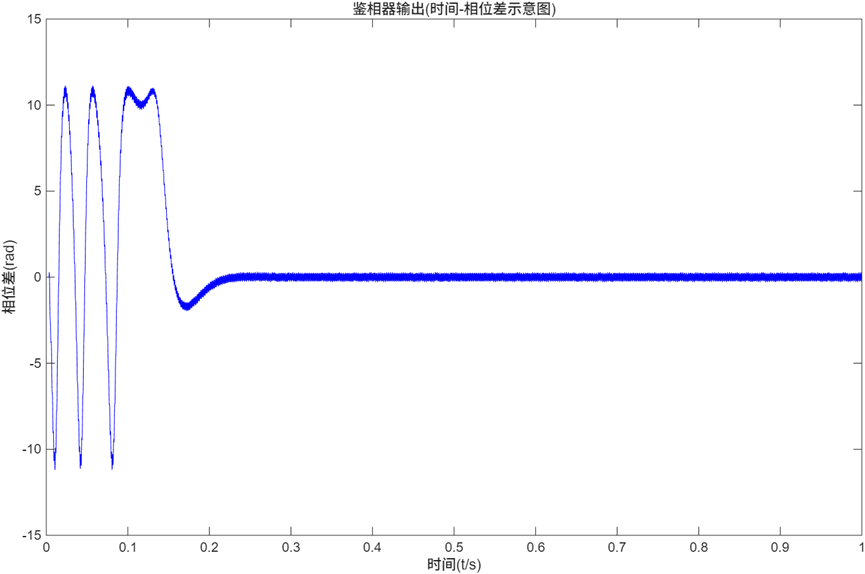

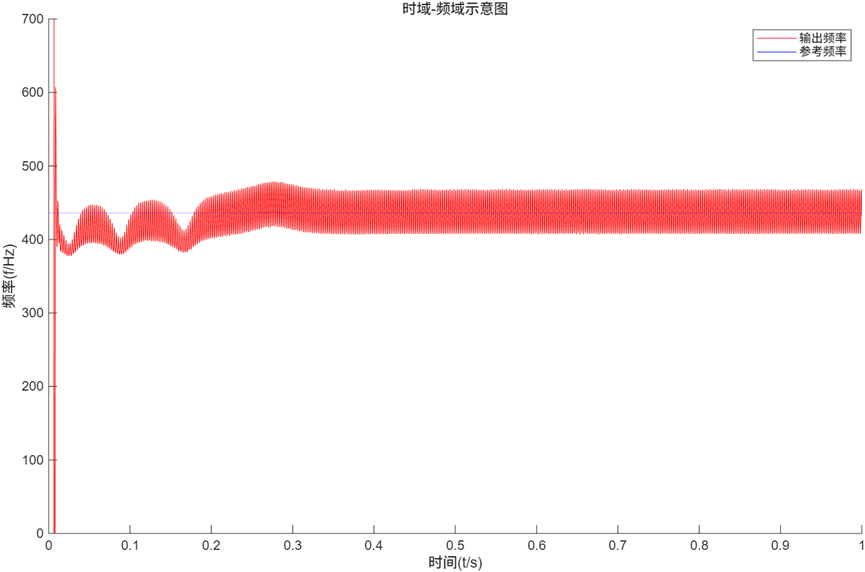

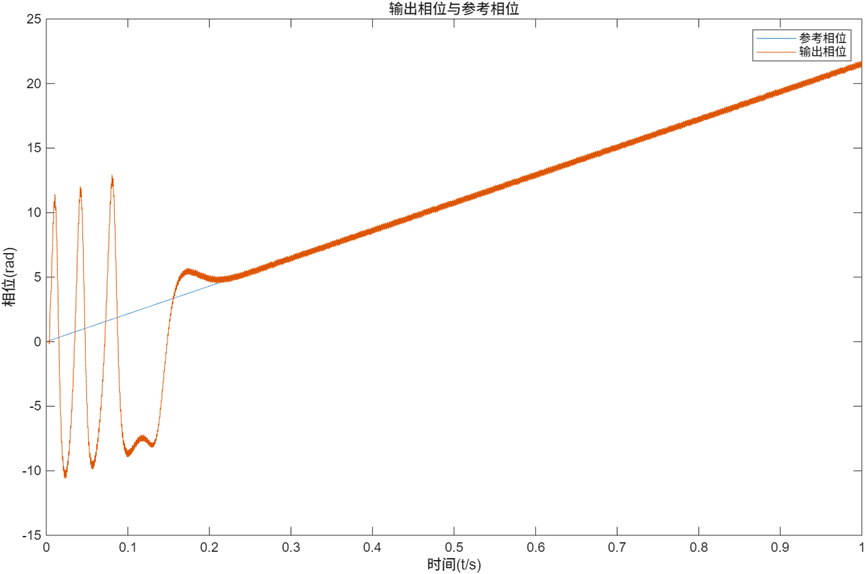

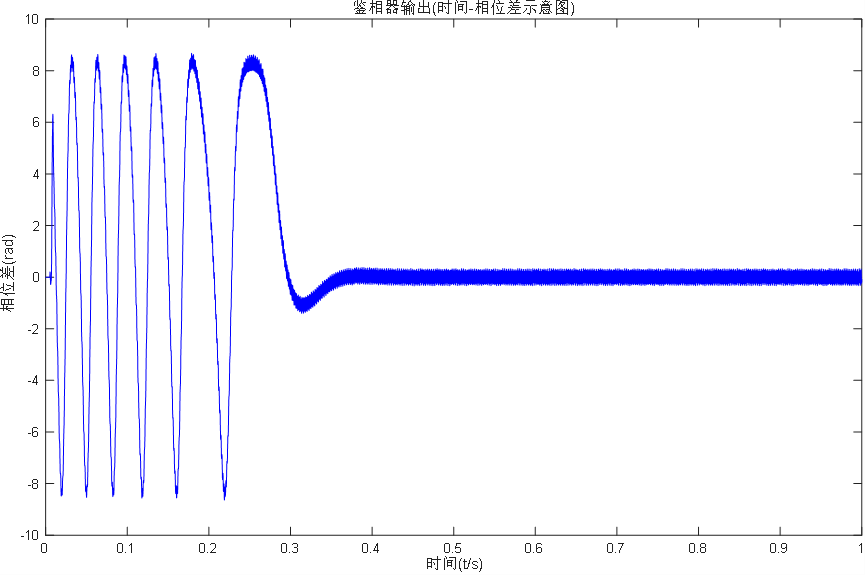

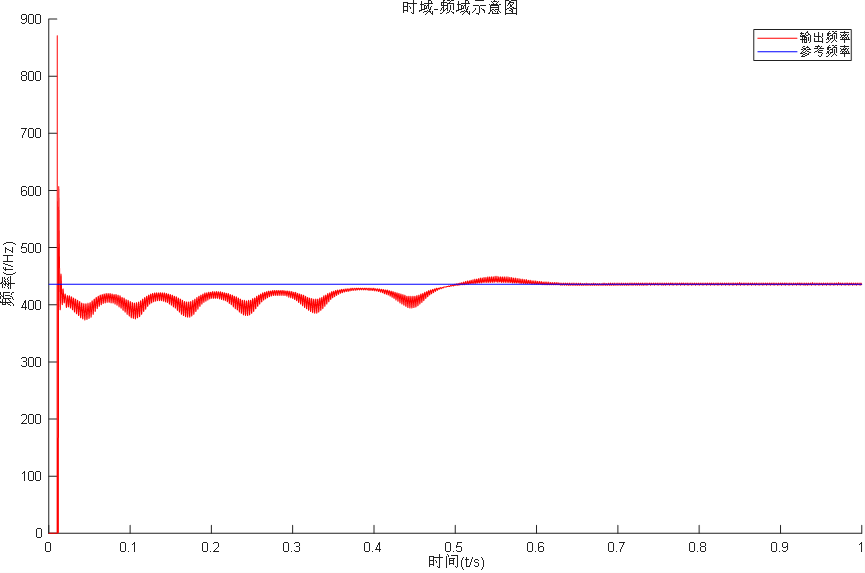

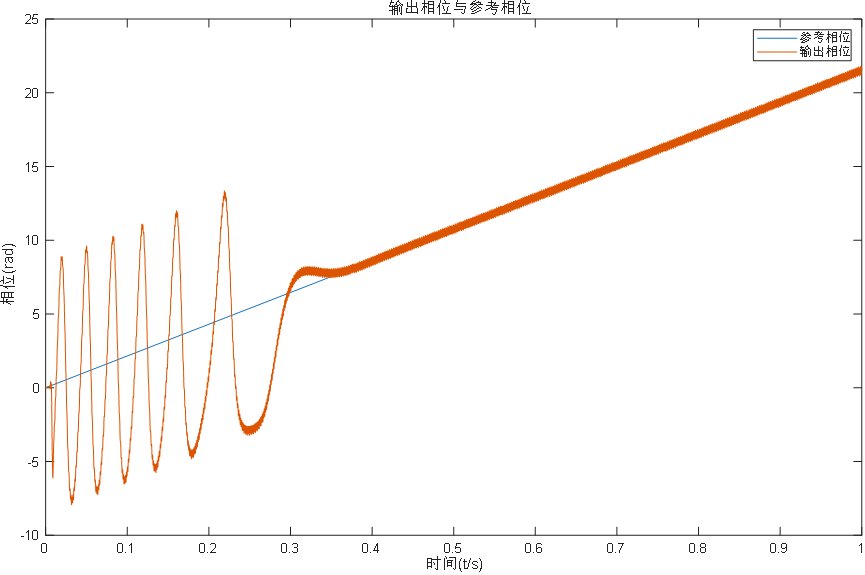

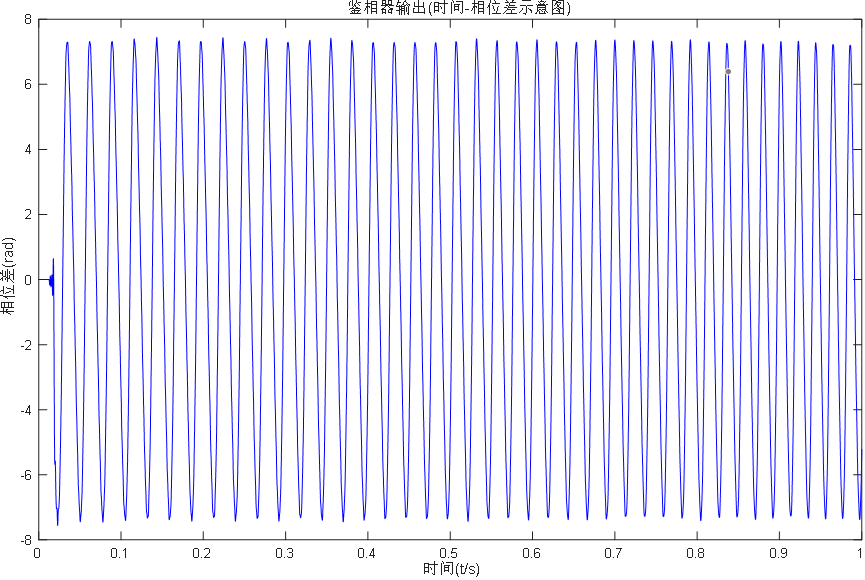

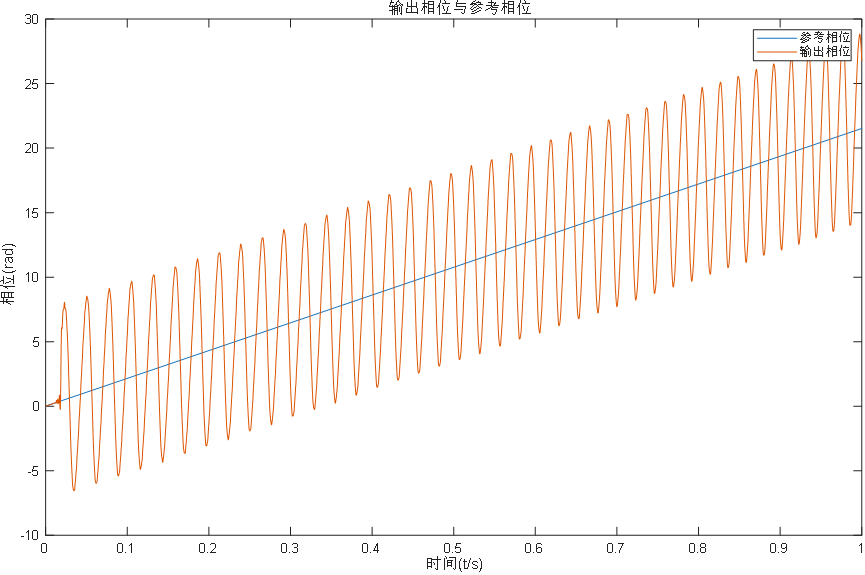

做有源比例积分滤波器的仿真:

带宽宽[200 600]

带宽[350 600]

带宽[500 600]

参考文献:最终代码有参考南京大学的一位大佬,但是我找不到他博客地址了,如果看到在此感谢