引言

本文基于 STM32F407 系列芯片,详细拆解嵌入式系统核心的存储系统与时钟系统。存储系统是数据和程序的 "仓库",时钟系统是设备同步工作的 "节拍器",两者共同支撑嵌入式设备稳定运行。文中将补充细节说明、规范格式,并优化代码可读性,适合嵌入式开发入门及实战参考。

2.1 嵌入式存储系统概述

存储系统是嵌入式计算机系统的核心组成部分,用于满足不同类型数据的临时或永久存储需求,是程序运行和数据处理的基础。

2.1.1 核心作用

-

存储程序代码:嵌入式设备上电后,CPU 会从存储介质中读取指令并顺序执行。

-

存储运行时数据:包括程序运行过程中产生的变量、堆栈数据,以及传感器采集的临时数据。

-

存储持久化信息:系统配置参数、用户自定义设置等,要求掉电后数据不丢失。

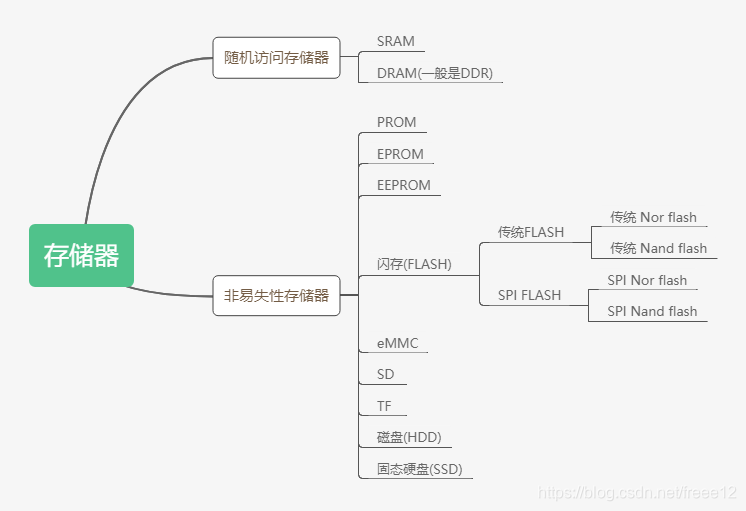

2.1.2 存储介质分类

嵌入式存储介质按 "掉电后数据是否保留" 分为易失性存储器 和非易失性存储器两大类,具体分类及特性如下:

1. 易失性存储器(RAM)

随机访问存储器(RAM)掉电后数据立即丢失,按存储机制分为 DRAM 和 SRAM:

| 特性 | DRAM(动态随机存储器) | SRAM(静态随机存储器) |

|---|---|---|

| 存储原理 | 利用电容存储电荷(电荷有无代表 1/0) | 利用触发器电路存储数据 |

| 存取速度 | 较慢 | 较快 |

| 集成度 | 较高 | 较低 |

| 生产成本 | 较低 | 较高 |

| 是否需要刷新 | 是(定期补充电容电荷) | 否(电路稳定保持数据) |

| 常见类型 | DDR SDRAM、DDR2/3 SDRAM 等 | 片内 SRAM、缓存 Cache 等 |

2. 非易失性存储器

掉电后数据长期保留,核心类型包括 ROM、Flash、机械硬盘、光盘等,其中 Flash 是嵌入式系统的主流选择:

| 存储类型 | 核心特性 | 典型应用场景 |

|---|---|---|

| MASK ROM | 出厂时固化数据,不可修改 | 批量生产的固定程序存储 |

| OTPROM | 一次可编程,写入后不可修改 | 低成本、固定参数存储 |

| PROM | 可一次性编程,需专用设备 | 早期工业控制设备 |

| EPROM | 可擦除重写(需紫外线照射) | 早期开发板、实验设备 |

| EEPROM | 电可擦除重写,字节级操作 | 小容量配置参数存储(如 I2C 接口) |

| NOR Flash | 支持随机访问,读取速度快 | 固件、操作系统、配置数据存储 |

| NAND Flash | 不支持随机访问,容量密度高 | 大数据存储(音视频、文件系统) |

| 机械硬盘 / 光盘 | 容量大、成本低,速度较慢 | 外部扩展存储(如嵌入式 PC) |

注意:STM32F407 系列默认使用 NOR Flash,支持随机访问特性,因此程序可直接在 Flash 中运行(无需拷贝到 RAM)。

2.1.3 STM32F407 片内存储详情

STM32F407VET6 芯片内置 192KB SRAM,按功能划分为三部分,各司其职:

-

主 SRAM(128KB):最常用的存储区域,用于存放全局变量、局部变量、函数堆栈等运行时数据。

-

CCM RAM(64KB):内核专属 RAM,不经过总线矩阵,访问速度更快。需通过关键字指定变量存储位置,示例代码:

cpp// 定义存储在CCM RAM中的高速缓冲区 uint32_t __attribute__((section(".ccmram"))) high_speed_buffer[1024]; -

备份 SRAM(16KB):需通过备份域供电,掉电后可通过备用电源(如纽扣电池)保持数据,适合存储关键配置参数。

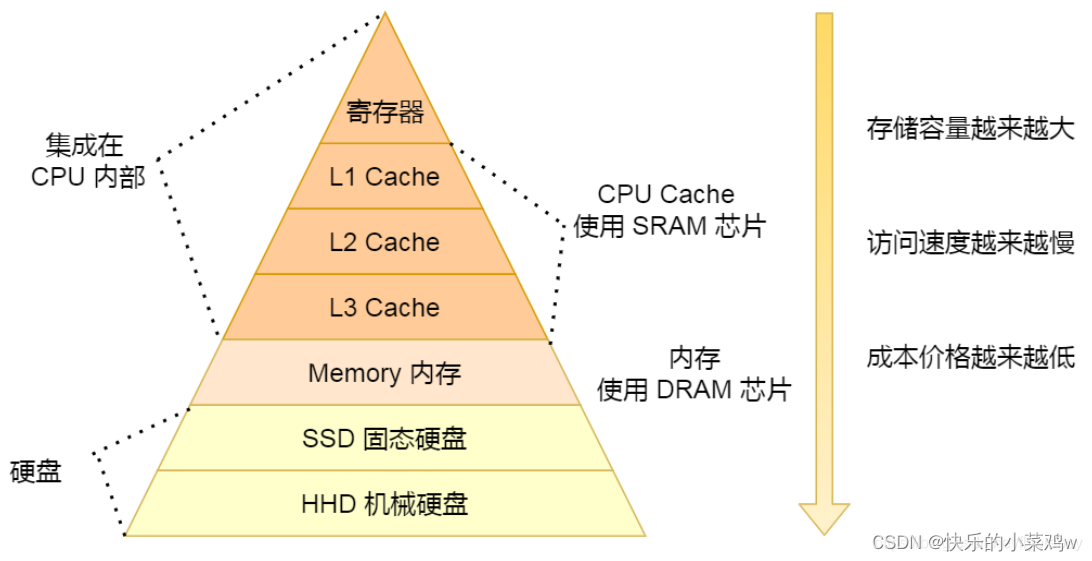

2.1.4 嵌入式存储体系架构

嵌入式存储系统以 CPU 为核心,融合片内和片外存储资源,形成 "速度递减、容量递增、成本递减" 的分层架构:

- 缓存(Cache):速度最快、容量最小,用于缓存 CPU 频繁访问的指令和数据,减少主存访问延迟。

- 主存储器(SRAM/SDRAM):速度较快,用于存放程序运行时的变量、堆栈等临时数据。

- 程序存储器(Flash):速度中等,用于存储固件、操作系统等可执行代码。

- 外部扩展存储器(eMMC、SD 卡等):容量大、成本低,用于存储大量用户数据、大型应用程序。

存储体系工作流程

- 系统上电后,CPU 从程序存储器(如 NOR Flash)的固定地址取出第一条指令。

- 指令和高频访问数据被加载到 Cache 和 CPU 寄存器中,提升执行效率。

- 程序运行时产生的变量、堆栈数据实时写入主存储器(SRAM/SDRAM)。

- 当需要运行大型应用或访问海量数据时,系统从外部扩展存储器(如 eMMC)读取数据到主存供 CPU 处理。

2.2 嵌入式时钟系统

时钟系统是嵌入式设备的 "心脏节拍器",为 CPU 和外设提供同步工作的时间基准,没有时钟信号,CPU 和外设无法协调运行。

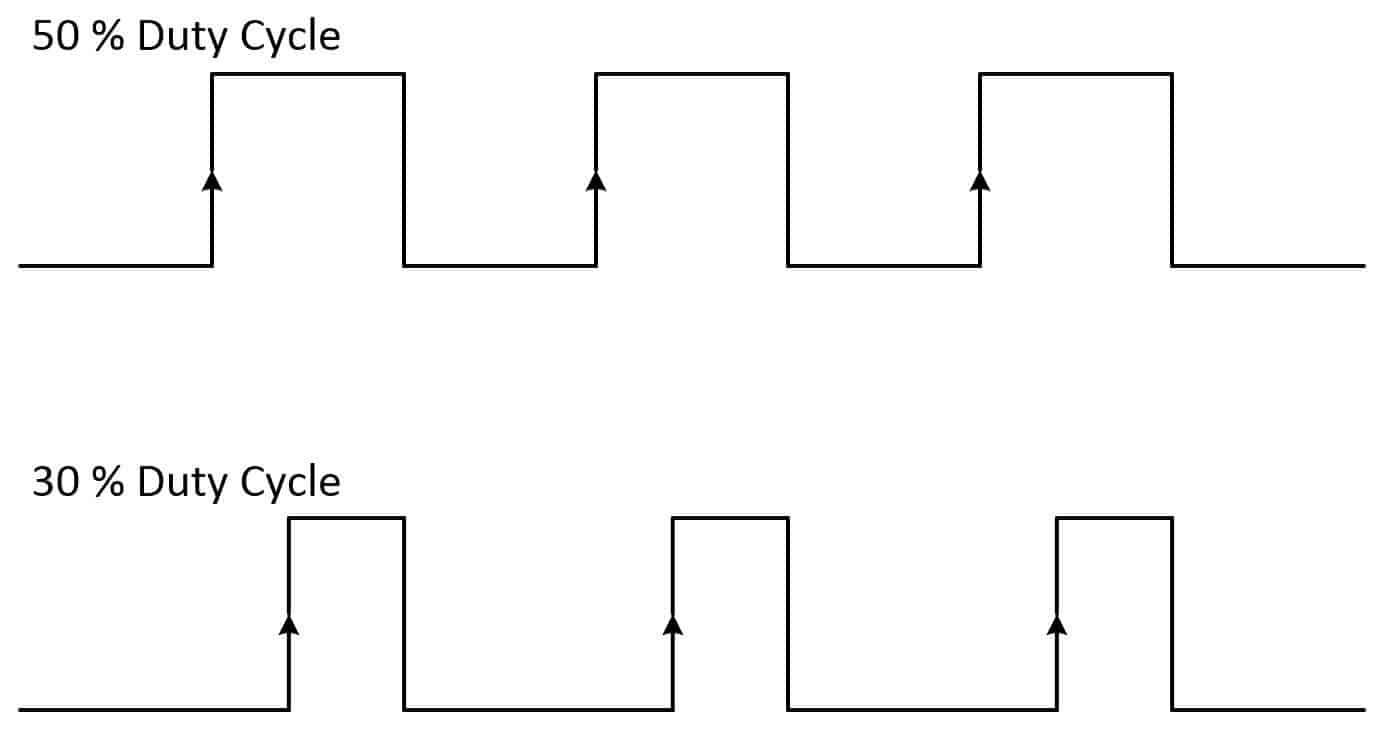

2.2.1 时钟信号的定义

时钟信号是具有固定周期的方波信号,通过高低电平的周期性交替,为数字电路提供同步时序。信号的周期决定时钟频率,频率越高,CPU 执行指令的速度越快。

2.2.2 时钟系统的核心作用

时钟信号是 STM32 各模块协同工作的 "时间基准",主要承担以下角色:

- CPU 指令执行 :Cortex-M4 内核执行指令分为取指令、译码、执行三个阶段,时钟信号控制执行节奏。若一个周期执行一条指令,频率越高则单位时间内执行的指令数越多。

- 外设控制:STM32 的 GPIO、UART、定时器等所有外设均通过寄存器操作,寄存器值修改、外设功能触发必须在时钟信号配合下完成。

- 数据传输同步:串行通信(如 UART、SPI)需依赖时钟同步收发双方,确保数据正确传达。

- 定时与计数:时钟是 "时间的标尺",通过计数时钟周期可实现定时(如定时器中断)和计数功能。

2.2.3时钟源分类

为解决功耗浪费 (外设时钟无用时持续耗电)和速度兼容(不同外设工作频率差异大)问题,STM32 采用 "多时钟源 + 按需分配" 设计。四类核心时钟源对比如下:

| 时钟源 | 名称 | 材质 / 实现 | 频率范围 | 典型应用 |

|---|---|---|---|---|

| HSE | 外部高速振荡时钟 | 石英晶体(精度高) | 4-26MHz(常用 8MHz) | 系统主时钟(经 PLL 倍频) |

| LSE | 外部低速振荡时钟 | 石英晶体 | 32.768KHz | RTC 实时时钟、低功耗定时 |

| HSI | 内部高速振荡时钟 | RC 振荡电路(精度低) | 16MHz | 系统时钟备份、启动阶段时钟 |

| LSI | 内部低速振荡时钟 | RC 振荡电路 | 32KHz | 独立看门狗、低功耗模式时钟 |

2.2.4时钟树与 PLL 锁相环

时钟树概念

微控制器的时钟传输路径如同 "大树的养分流动":从外部晶振输入开始,经分频、倍频后分配到 CPU、外设、总线等各模块,这一路径称为时钟树。

PLL 锁相环(倍频核心)

PLL(锁相环)是 "倍频" 核心,可将 HSE/HSI 的低频信号放大到高频。例如,STM32F407 的 168MHz 系统主频即由8MHz HSE + PLL 倍频实现。

2.2.5RCC - 时钟的总控制器

RCC(Reset and Clock Control,复位与时钟控制)是管理 STM32 "时钟" 与 "复位" 的核心外设,通过寄存器集合实现所有时钟操作。

RCC 寄存器结构(关键模块)

cpp

typedef struct {

__IO uint32_t CR; // 时钟控制:使能HSE/HSI、检测时钟就绪

__IO uint32_t PLLCFGR; // PLL配置:设置分频/倍频系数(M/N/P/Q)

__IO uint32_t CFGR; // 时钟配置:选择系统时钟源、总线预分频

__IO uint32_t CIR; // 时钟中断:使能时钟就绪中断

__IO uint32_t AHB1RSTR; // AHB1外设复位

__IO uint32_t AHB2RSTR; // AHB2外设复位

__IO uint32_t AHB3RSTR; // AHB3外设复位

uint32_t RESERVED0; // 保留位

__IO uint32_t APB1RSTR; // APB1外设复位

__IO uint32_t APB2RSTR; // APB2外设复位

uint32_t RESERVED1[2]; // 保留位

__IO uint32_t AHB1ENR; // AHB1外设时钟使能(如GPIOA、DMA)

__IO uint32_t AHB2ENR; // AHB2外设时钟使能

__IO uint32_t AHB3ENR; // AHB3外设时钟使能

uint32_t RESERVED2; // 保留位

__IO uint32_t APB1ENR; // APB1外设时钟使能(如UART2、TIM2)

__IO uint32_t APB2ENR; // APB2外设时钟使能(如UART1、TIM1)

// 低功耗、备份域等寄存器略

} RCC_TypeDef;RCC 的核心功能

- 使能时钟源 :通过

CR寄存器操作(如RCC->CR |= RCC_CR_HSEON使能 HSE)。 - 配置 PLL :通过

PLLCFGR设置分频系数(M)、倍频系数(N)、系统时钟分频系数(P)。 - 使能外设时钟 :通过

AHBxENR/APBxENR(如RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN使能 GPIOA 时钟)。 - 选择系统时钟源 :通过

CFGR寄存器选择 PLL、HSE 或 HSI 作为 SYSCLK。