📋 项目概述

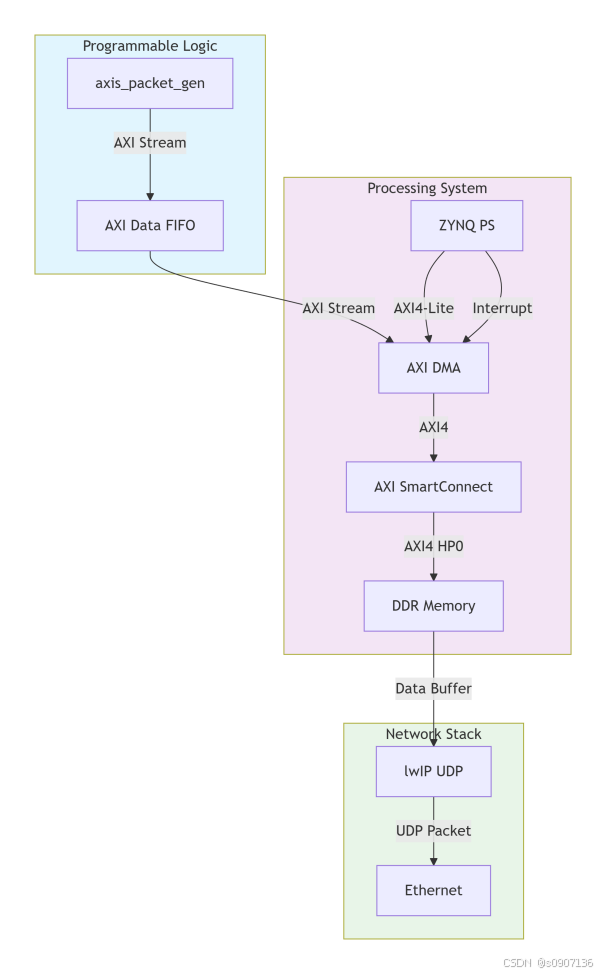

本项目实现了一个基于Xilinx ZYNQ-7000系列FPGA的完整数据传输系统,通过AXI DMA从PL(可编程逻辑)端接收数据流,并在PS(处理系统)端通过lwIP协议栈将数据封装为UDP包发送到网络。

🎯 系统功能

-

PL端: 生成测试数据包并通过AXI Stream接口发送

-

DMA传输: 将PL数据高效传输到DDR内存

-

PS处理: 处理DMA中断,封装UDP数据包

-

网络传输: 通过以太网发送UDP数据包

🏗️ 硬件架构

系统框图

🔧 核心IP组件

1. ZYNQ Processing System (PS7)

-

芯片型号: xc7z035ffg676-2

-

时钟配置:

-

CPU频率: 666.67MHz

-

DMA时钟: 50MHz

-

以太网: 125MHz

-

-

外设配置:

-

千兆以太网 (MIO 16-27)

-

UART1 (MIO 12-13)

-

SD卡接口 (MIO 40-45)

-

QSPI Flash (MIO 1-6)

-

2. AXI DMA (axi_dma_0)

-

工作模式: 简单模式 (非Scatter-Gather)

-

通道配置:

-

仅使能S2MM (Stream to Memory Map)

-

数据宽度: 32位

-

最大突发长度: 256

-

-

中断配置: S2MM完成中断

3. AXI SmartConnect

-

连接DMA与PS的HP0端口

-

实现高效的AXI总线互联

4. AXI Data FIFO

-

缓冲AXI Stream数据

-

配置: 32位数据宽度,支持TLAST/TKEEP

🔌 接口定义

AXI Stream接口 (PL→PS)

c

// 数据信号

input wire [31:0] m_axis_tdata, // 32位数据

output wire [3:0] m_axis_tkeep, // 字节使能

input wire m_axis_tvalid, // 数据有效

output wire m_axis_tready, // 接收就绪

input wire m_axis_tlast // 包结束标志时钟与复位

-

主时钟: 50MHz (PsClk)

-

复位: 低电平有效异步复位

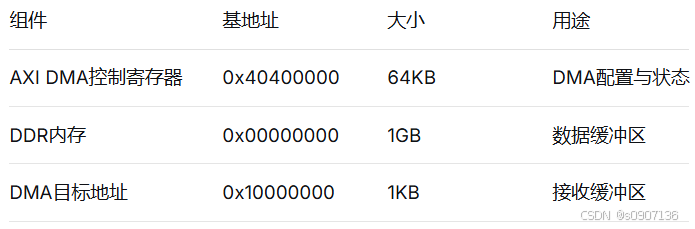

📊 地址映射

💻 软件架构

主要功能模块

1. DMA驱动层

c

// DMA初始化与配置

XAxiDma_CfgInitialize(&AxiDma, DmaConfig);

XAxiDma_SimpleTransfer(&AxiDma, buffer_addr, length, direction);

// 中断处理

static void RxIntrHandler(void *Callback)

{

// 处理传输完成中断

// 数据缓存一致性处理

// 重启DMA传输

}2. 网络协议栈

c

c

// lwIP网络初始化

lwip_init();

xemac_add(&netif, &ipaddr, &netmask, &gw, ...);

// UDP数据发送

void send_udp_packet(u8 *data, int length)

{

struct udp_pcb *udp_conn = udp_new();

udp_sendto(udp_conn, p, &remote_addr, UDP_CLIENT_PORT);

}3. 系统管理

-

内存访问验证

-

错误检测与恢复

-

寄存器状态监控

🔄 数据处理流程

-

PL数据生成

-

axis_packet_gen模块每秒生成1024字节测试数据

-

数据模式: 递增字节序列

-

-

DMA传输

-

AXI Stream数据通过FIFO缓冲

-

DMA将数据写入DDR指定地址(0x10000000)

-

传输完成触发中断

-

-

网络发送

-

中断处理函数读取DDR中的数据

-

通过lwIP封装UDP包

-

发送到目标IP: 192.168.1.100:1235

-

⚙️ 配置参数

网络配置

c

#define UDP_CLIENT_PORT 1235

IP4_ADDR(&ipaddr, 192, 168, 1, 10); // 本地IP

IP4_ADDR(&netmask, 255, 255, 255, 0); // 子网掩码

IP4_ADDR(&gw, 192, 168, 1, 1); // 网关

IP4_ADDR(&remote_addr, 192, 168, 1, 100); // 目标IPDMA配置

c

#define PACKET_SIZE 1024 // 数据包大小

#define DMA_RX_BUFFER_ADDRESS 0x10000000 // 缓冲区地址🛠️ 调试与诊断

调试功能

- 内存访问测试: 验证DDR访问权限

- 寄存器转储: DMA状态监控

- 数据完整性检查: 全零数据检测

- 错误状态分析: 详细的DMA错误诊断

错误处理

-

DMA传输错误自动恢复

-

内存访问失败时的备用地址

-

网络发送失败重试机制

📈 性能特性

-

数据传输率: 1024字节/秒 (测试模式)

-

网络延迟: 基于lwIP优化的低延迟

-

内存带宽: 通过HP0端口的高带宽DDR访问

-

中断响应: 快速中断处理确保实时性

🔧 构建与部署

硬件生成

c

# tcl

# 使用Vivado运行PsSys.tcl

source PsSys.tcl

create_root_design ""软件编译

bash

# 使用Xilinx SDK编译

xsdk -workspace . -hwsystem system.hdf系统配置

- 生成比特流文件

- 导出硬件到SDK

- 编译应用程序

- 下载到目标板

📝 测试验证

测试项目

- PL数据生成验证: 确认测试数据模式

- DMA传输测试: 验证数据完整性

- 中断功能测试: 确认中断响应

- 网络通信测试: UDP包收发验证

- 系统稳定性测试: 长时间运行测试

预期结果

-

每秒接收到1024字节UDP数据包

-

数据内容为递增字节序列

-

网络传输稳定无丢包