昇腾NPU

问:昇腾

答:

已深度思考(用时5秒)

好的,用户突然只发了"昇腾"两个字,我得先确定他到底想知道什么。首先,得看看对话历史有没有上下文,但这里历史是空的,说明可能是第一次询问。

嗯,"昇腾"这个词通常指的是华为的昇腾AI处理器。用户可能是在新闻里看到,或者需要技术资料,也可能是想对比其他芯片。得考虑用户身份,如果是普通爱好者,可能需要基础介绍;如果是开发者或企业用户,可能更关注性能、应用场景或如何获取资源。

深层需求可能包括:想了解昇腾相比英伟达的优势,或者如何在项目中使用昇腾。也有可能在考虑采购或学习AI技术,需要评估昇腾的适用性。

另外,用户没提具体问题,所以回复既要全面又要结构清晰,方便他们找到重点。得涵盖定义、产品系列、特点、应用场景,最后提到获取途径,这样不同需求都能覆盖到。还要强调昇腾在国内的重要性,满足可能存在的国产化替代兴趣。

好的,这是一个关于"昇腾"的全面介绍。

"昇腾"特指华为公司自主研发的AI(人工智能)处理器系列,是华为全栈全场景AI解决方案的核心组成部分。它的名字寓意着"上升"和"腾飞",象征着华为在人工智能领域的雄心。

简单来说,昇腾就是华为的"AI芯片",类似于谷歌的TPU、英伟达的GPU,但有其独特的技术路线和生态定位。

昇腾的核心要点

1. 两大产品系列

昇腾系列主要包含两种类型的处理器,以适应不同的计算场景:

- •昇腾Ascend AI处理器 :这是主力产品,专为AI计算设计。•昇腾910 :核心是超高算力 ,主打训练 。它的计算密度和能效比在发布时达到了业界领先水平,主要用于数据中心、云环境,进行大规模、复杂的AI模型训练。•昇腾310 :核心是高能效和低功耗 ,主打推理。它适用于边缘计算、终端设备等场景,比如服务器推理、自动驾驶、智能摄像头等,能够高效地运行已经训练好的AI模型。

2. 达芬奇架构

昇腾处理器采用了华为自研的达芬奇架构,这是其技术核心。该架构的特点包括:

- •3D Cube技术:大幅提升矩阵运算效率,而矩阵运算是深度学习的基础。

- •多核异构:集成AI计算核心(Cube)、CPU核心和任务调度单元,实现高效协同。

- •覆盖全场景:从极致的低功耗到极致的大算力,达芬奇架构都能支持,这使得昇腾芯片可以应用于从物联网终端到数据中心的广泛场景。

3. 昇腾AI生态

华为围绕昇腾芯片构建了完整的软硬件生态,目的是让开发者更容易地使用昇腾的计算能力:

- •CANN :异构计算架构。它是连接上层AI框架和底层昇腾硬件的"桥梁",负责硬件资源的调度和优化,是性能发挥的关键。

- •AI框架 :支持主流的AI框架,如 MindSpore(华为自研)、TensorFlow、PyTorch等。通过CANN,这些框架的代码可以高效地在昇腾硬件上运行。

- •应用使能:提供模型仓库、开发工具链等,方便开发者进行应用创新和部署。

- •昇思MindSpore:这是一个需要特别提及的框架。它是华为自研的全场景AI计算框架,与昇腾硬件深度绑定,可以实现"软硬件协同优化",发挥出最佳性能。

昇腾的重要性与战略意义

- 1.打破垄断 :在AI计算领域,尤其是训练侧,英伟达的GPU长期占据主导地位。昇腾的出现,为市场提供了重要的国产化替代方案,对于中国的AI产业发展和科技自主可控具有战略意义。

- 2.全栈全场景优势:华为提供的是从芯片(昇腾)、硬件(Atlas系列服务器/设备)、操作系统(欧拉)、AI框架(MindSpore)到应用使能的完整解决方案。这种垂直整合能力有助于优化整体性能和降低成本。

- 3.应对技术封锁:在国际贸易环境变化的背景下,拥有自研的AI芯片和生态,可以有效降低对外部技术的依赖风险。

主要应用场景

昇腾AI解决方案已广泛应用于各行各业:

- •智慧城市:交通调度、人脸识别、视频分析。

- •科学研究:天文探索、药物研发、天气预报。

- •互联网服务:推荐系统、搜索引擎、内容审核。

- •智能制造:质量检测、设备预测性维护。

如何获取和使用昇腾的算力?

普通开发者和企业可以通过以下方式接触和使用昇腾:

- 华为云 :华为云提供了基于昇腾的AI计算服务(如ModelArts 平台、Ascend NPU 资源),用户无需购买实体硬件,即可按需租用算力。

- Atlas系列产品:华为推出了基于昇腾芯片的硬件产品,如Atlas 200/500/800/900等系列模块、板卡、服务器,企业可以采购这些设备部署在自己的数据中心。

总结

昇腾是华为在人工智能时代的基石性技术,它不仅仅是一颗芯片,更代表着一套从硬件到软件、从云到边缘的完整AI计算体系。它的发展直接关系到华为乃至中国在全球AI竞争中的地位。

NPU

问:NPU

答:

已深度思考(用时4秒)

好的,用户现在问的是"NPU",而之前的对话历史是在详细讨论华为的昇腾AI处理器。首先得确定用户为什么在了解昇腾之后突然提到NPU。可能他们注意到昇腾被归类为NPU,想进一步了解NPU本身的概念,或者想理清昇腾和NPU的关系。

用户可能是刚接触AI硬件的小白,或者有一定技术背景但想深化理解。他们的直接需求是明确NPU的定义,但深层需求可能包括:为什么需要NPU(与CPU/GPU的区别),NPU的实际应用,以及昇腾在NPU中的定位。

得先给出NPU的核心定义,强调其专用性,然后对比现有处理器,突出优势。还要联系之前的昇腾内容,说明昇腾是NPU的一种实现,帮助用户建立知识关联。可能用户还想知道NPU的发展趋势,比如在端侧设备的重要性,以及华为昇腾在此领域的角色。

要注意避免技术术语过于复杂,用比喻和常见场景举例,比如手机拍照、语音助手,让概念更易懂。同时要点出NPU在AI普及中的关键作用,满足用户潜在的学习或应用需求。

好的,我们来详细解释一下 NPU。

NPU 是 神经网络处理器 的缩写,它是一种专门为执行人工智能 计算任务而设计的微处理器。你可以把它理解为一个"AI加速器 "或"AI大脑"。

简单来说,如果说CPU 是计算机的"全能大脑",负责各种通用任务;那么NPU就是专门为"思考"AI问题(如图像识别、语音处理)而生的"专家型大脑"。

NPU 的核心思想:为什么需要它?

AI计算,尤其是深度学习和神经网络的计算,有其独特的特点:

- 1.海量并行计算:神经网络通常包含数百万甚至数十亿个参数(神经元之间的连接),这些计算很多是可以同时进行的。

- 2.特定的运算模式 :主要涉及两种核心运算:乘积累加运算 和激活函数。

- 3.能效比要求高:无论是在云端数据中心(追求算力)还是在手机、摄像头等边缘设备(追求低功耗),都需要高效地完成AI计算。

通用处理器(如CPU) 虽然什么都能做,但面对上述这种高度重复、并行度极高的AI任务时,就像用瑞士军刀去砍树,能完成但效率低下、耗时长、功耗高。

NPU 就是为了解决这个问题而生的。它采用了一种称为 "数据流架构" 或"特定域架构"的设计,其内部有成千上万个专门为乘积累加运算设计的小核心,可以同时进行海量计算,从而在处理AI任务时实现高效率、低延迟、低功耗。

NPU 与其他处理器的对比

为了更好地理解NPU,可以将其与常见的处理器进行对比:

| 处理器类型 | 全称 | 角色比喻 | 特点 | 擅长任务 |

|---|---|---|---|---|

| CPU | 中央处理器 | 全能总经理 | 通用性强,擅长逻辑控制和复杂任务调度 | 运行操作系统、应用程序、处理各种复杂指令 |

| GPU | 图形处理器 | 大规模流水线工人 | 拥有数千个计算核心,极度擅长并行处理 | 图形渲染、科学计算、AI训练(通用性强) |

| NPU | 神经网络处理器 | AI专项特种兵 | 架构极度专一,为神经网络计算优化,能效比极高 | AI推理 (如图像识别、语音助手)、部分AI训练 |

简单关系:

- •CPU 负责整体调度和控制。

- •当有大型并行计算任务(如游戏画面、AI训练)时,GPU 作为强力助手。

- •当有专门的、需要极高能效的AI任务(如手机拍照的背景虚化、语音唤醒)时,NPU 作为最专业的助手出场。

现代芯片(如手机SoC、服务器CPU)通常采用 "异构计算" 架构,即 CPU + GPU + NPU 组合在一起,各司其职,协同工作,以实现最高效率和最佳性能。

NPU 的主要应用场景

NPU已经无处不在:

- 1.智能手机 :这是NPU最普及的应用。用于:•摄影 :人像模式虚化、夜景模式降噪、场景识别。•语音助手 :本地语音识别和唤醒(如"Hey Siri")。•面部解锁:快速、安全地识别面部特征。

- 2.自动驾驶:需要实时处理摄像头、雷达的海量数据,识别行人、车辆、交通标志,NPU的低延迟至关重要。

- 3.智能安防:摄像头实时分析视频流,进行人脸识别、车辆识别、异常行为检测。

- 4.云计算数据中心:处理来自全球的AI推理请求,如搜索引擎的智能推荐、内容审核等。

- 5.物联网设备:如智能音箱的语音识别、智能家居的传感器数据分析。

著名的 NPU 例子

- •华为麒麟/昇腾芯片中的NPU :采用自研的达芬奇架构,就是我们上一个话题讨论的"昇腾"的核心。

- •苹果A系列/M系列芯片中的Neural Engine:这就是苹果自家的NPU,为iPhone、iPad、Mac的AI功能提供强大动力。

- •高通骁龙芯片中的Hexagon处理器:集成了NPU核心,为安卓手机提供AI能力。

- •谷歌TPU:虽然名称是"张量处理器",但本质上也是一种特定类型的NPU,主要用于谷歌的云端AI服务。

总结

NPU 是人工智能时代硬件发展的必然产物。它代表了从"通用计算"向 "专用计算" 的转变,通过为特定的AI工作负载进行深度优化,极大地推动了AI技术在各行各业的落地和应用。当你享受手机拍照的瞬间美化、与语音助手流畅对话时,背后往往就有NPU在默默高效工作。

LLM算子

问:LLM算子

答:

已深度思考(用时5秒)

好的,用户现在问的是"LLM算子",我得先确定他们到底想知道什么。之前对话历史里已经讨论了昇腾NPU和NPU的基本概念,用户可能是在深入理解AI芯片如何具体支持大模型。

用户可能是开发者或者技术爱好者,可能在学习大模型技术,或者在实际工作中遇到性能优化问题。他们可能想了解算子层面的优化,以便更好地利用硬件,比如华为的昇腾。深层需求可能是想优化自己的LLM应用,或者解决训练、推理中的瓶颈。

首先得明确LLM算子的定义,不能只讲理论,要结合之前提到的昇腾NPU来说。比如提到MatMul和Attention在昇腾上如何通过达芬奇架构优化。用户可能想知道这些算子如何影响性能,以及如何针对特定硬件进行调优。

还要考虑用户可能对软硬件协同优化感兴趣,比如CANN和MindSpore的作用。需要解释清楚算子库和框架如何让开发者无需关注底层细节,直接提升效率。

另外,用户可能没直接说出来的需求是:如何选择或优化硬件来部署LLM,或者理解不同芯片(如NPU vs GPU)在算子支持上的差异。需要强调专用芯片(如昇腾)在特定算子上的优势,比如Flash Attention的优化。

最后,要确保解释足够具体,有实际例子,比如矩阵乘法的分块计算,避免过于抽象。同时联系之前提到的昇腾310和910,说明训练和推理中算子的不同侧重点。

好的,这是一个非常专业且核心的技术概念。我们来详细解释一下 LLM 算子。

核心概念:什么是 LLM 算子?

简单来说,LLM 算子 指的是大规模语言模型在计算过程中所依赖的基本计算操作单元。

你可以将它类比为数学中的"基本运算符号"(如加、减、乘、除)。任何一个复杂的数学公式,最终都可以分解为这些基本符号的组合。同样,一个庞大而复杂的LLM(如GPT、LLaMA),其整个计算图(从输入文本到输出文本)最终也可以被拆解成一系列更小的、优化过的"算子"的组合。

核心思想:

将复杂的模型计算分解成更小、更易于在硬件(如GPU、NPU)上并行化和极致优化的计算单元。

为什么 LLM 算子如此重要?

LLM拥有巨大的参数量和计算量,其性能瓶颈往往不在算法本身,而在计算效率上。算子的重要性体现在:

- 1.性能关键 :一个未经优化的算子实现可能只能发挥硬件(如GPU)理论算力的10%-20%。而一个高度优化的算子,可以通过利用硬件的特定特性(如Tensor Cores、内存层级、流水线),将性能提升数倍甚至数十倍,直接决定模型的训练速度 和推理延迟。

- 2.内存瓶颈:LLM的"注意力机制"等操作对内存带宽极其敏感。优秀的算子设计可以最大化数据复用,减少对显存带宽的依赖,从而避免"内存墙"问题,提升计算效率。

- 3.硬件适配:不同的硬件(NVIDIA GPU, AMD GPU, 华为昇腾NPU等)有其独特的架构。需要为这些硬件编写或生成高度优化的"算子实现",才能充分发挥其计算能力。这就是为什么各大厂商(如NVIDIA的CuDNN,华为的CANN)都投入巨大精力开发自己的高性能算子库。

常见的 LLM 核心算子

LLM的计算主要由以下几类关键算子构成:

1. 矩阵乘法 - GEMM

- •是什么:通用矩阵乘法。这是LLM中最基础、计算量最大的算子。模型中的每一个全连接层(Linear Layer)本质上都是一次或多次矩阵乘法。

- •为什么重要:它通常占据了LLM超过80%甚至90%的计算量。优化GEMM是提升LLM性能的重中之重。现代硬件(如GPU的Tensor Cores)都为其提供了专门的硬件加速单元。

2. 多头自注意力 - Multi-Head Attention

- •是什么 :Transformer架构的核心算子。其计算过程可以分解为:1.QKV投影 :三个矩阵乘法,将输入映射为查询、键、值。2.缩放点积注意力 :

Softmax(Q * K^T / sqrt(d_k)) * V。这里包含了矩阵乘法和Softmax。 - •为什么重要 :随着上下文长度的增加,

Q * K^T这个矩阵的规模会呈平方级增长,成为计算和内存的瓶颈。因此,出现了大量针对长上下文的注意力优化算子,如 FlashAttention,它通过巧妙的计算重排,避免了将巨大的中间矩阵写入显存,从而极大降低了内存占用并提升了速度。

3. 激活函数 - Activation Functions

- •是什么 :如 SiLU (Swish,用于GELU近似)、ReLU 、GeLU 等。它们是引入非线性的元素级操作。

- •为什么重要:虽然单个操作简单,但在整个网络中会执行亿万次。对其的优化(如融合)能带来可观的性能提升。

4. 层归一化 - LayerNorm

- •是什么:对每个样本进行归一化,稳定训练过程。涉及计算均值和方差,然后进行缩放和平移。

- •为什么重要:也是一个频繁调用的操作,其优化对稳定性有影响。

5. 其他算子

- •嵌入层查找:将输入的词索引转换为向量。

- •残差连接:简单的张量加法。

- •位置编码:为输入添加位置信息。

关键技术与趋势

1. 算子融合

这是最重要的优化技术之一。将多个连续的小算子(例如:LayerNorm -> GeLU -> Linear)融合成一个"超级算子"。

- •好处 :•减少内核启动开销 :GPU上启动一个内核有固定开销,融合后只需启动一次。•增加数据局部性:中间结果保留在高速缓存(Cache/Register)中,无需写回显存再读取,极大缓解内存带宽压力。

2. 内核优化

针对特定硬件指令集(如GPU的Tensor Cores, NPU的Cube单元)手工编写高度优化的汇编代码或使用底层编程模型(如CUDA),以最大化利用硬件算力。

3. 编译技术与自动代码生成

由于手动为每个算子和每种硬件架构编写优化代码工作量巨大,业界趋势是使用编译器技术(如MLIR, TVM):

- •开发者用高级语言描述算子的计算逻辑。

- •编译器自动根据目标硬件的特性,生成高度优化的底层代码。

- •代表 :PyTorch 2.0 的 TorchDynamo 和 Inductor 编译器就是通过捕获PyTorch模型的算子图,然后生成融合、优化后的代码来提升性能。

4. 动态形状支持

LLM推理时(尤其是使用解码策略时),输入的形状(如批次大小、序列长度)是动态变化的。优秀的算子需要能高效处理动态形状,避免因形状变化导致频繁重新编译或资源浪费。

总结

| 层面 | 内容 | 目标 |

|---|---|---|

| 算法层面 | Transformer架构、注意力机制 | 设计更好的模型 |

| 算子层面 | 将算法分解并实现为GEMM、Attention、LayerNorm等基本计算单元 | 极致优化每个单元的计算效率 |

| 硬件层面 | GPU、NPU、Tensor Cores、HBM显存 | 提供强大的算力和带宽 |

LLM算子 是连接上层AI算法与底层硬件芯片的关键桥梁。对大模型性能和效率的追求,最终都会落到对每一个算子的极致优化上。它是AI基础设施领域竞争的核心战场,直接决定了我们能否高效、低成本地训练和使用更强大的AI模型。

CPU流水线级数

问:CPU的流水线级数

答:

已深度思考(用时5秒)

好的,用户现在问的是"CPU的流水线级数",我得先确定他到底想知道什么。之前的历史对话里,他之前问了关于昇腾、NPU、LLM算子这些比较专业的内容,看起来他对计算机体系结构已经有了一定了解,可能是个学生或者从业者,正在深入学习CPU的设计细节。

用户可能是在学习处理器优化相关的知识,或者遇到性能方面的问题,想了解流水线级数对性能的影响。深层需求可能不只是定义,而是想理解不同级数如何在实际中权衡,比如为什么有些CPU用长流水线,有些用短流水线,以及这对实际应用(比如编程或系统设计)有什么影响。

得先解释基本概念,然后对比长短流水线的优缺点,用历史上的例子(比如Pentium 4和现代ARM处理器)来具体说明。还要提到现代CPU的趋势,比如适度流水线和解耦设计,这样用户能理解当前业界的实践。

要注意用户可能对技术术语熟悉,所以不用太基础的解释,但也不能跳过关键点。比如需要强调时钟频率、IPC、分支预测这些关键因素,以及它们如何相互制约。最后总结时,要联系实际应用,比如为什么手机芯片和服务器CPU选择不同的策略,帮助用户形成整体认知。

好的,这是一个非常核心的CPU架构问题。我们来详细解释一下CPU的流水线级数。

核心概念:什么是流水线?

想象一下汽车装配工厂。如果一辆汽车从零到完全组装好需要10个步骤,而每个步骤需要1小时,那么:

- •非流水线方式:完成第一辆车需要10小时后,才能开始生产第二辆车。效率极低。

- •流水线方式 :将生产线分为10个工位。当第一辆车完成步骤1、进入步骤2时,第二辆车立即开始步骤1。这样,虽然第一辆车还是需要10小时下线,但之后每隔1小时就有一辆新车下线。

CPU流水线也是完全相同的理念。它将一条指令的执行过程分解为多个离散的、更小的步骤(级)。每个步骤由专门的硬件电路在一个时钟周期内完成。这样,多条指令就可以像工厂的汽车一样,在流水线的不同阶段同时被执行,从而极大提高了吞吐率(单位时间内完成的指令数)。

流水线的典型级数

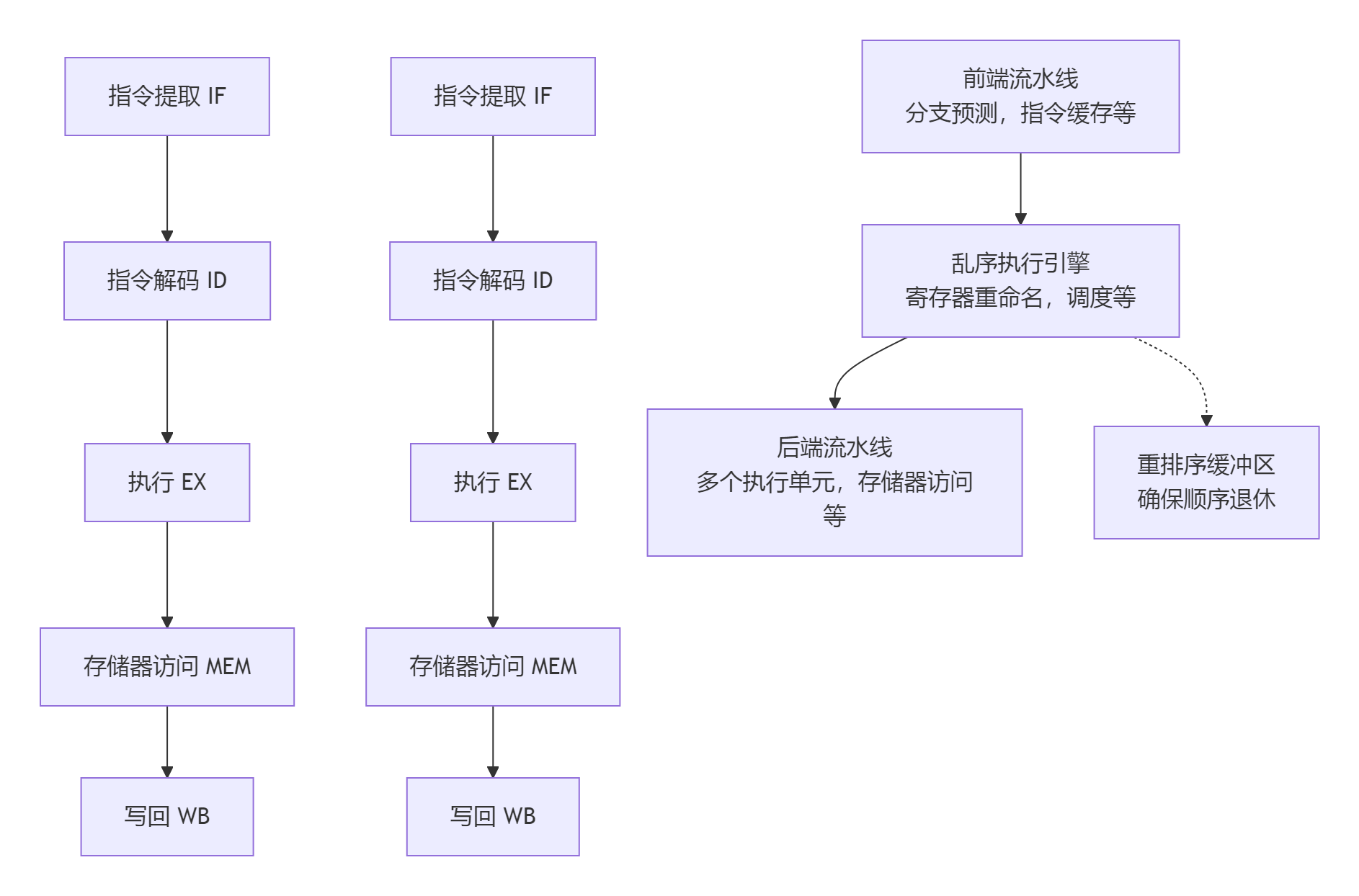

不同的CPU架构和设计目标导致了流水线级数的巨大差异。下图直观地展示了从简单到复杂的CPU流水线级数演变:

flowchart TD

A[指令提取 IF] --> B[指令解码 ID]

B --> C[执行 EX]

C --> D[存储器访问 MEM]

D --> E[写回 WB]

F[指令提取 IF] --> G[指令解码 ID]

G --> H[执行 EX]

H --> I[存储器访问 MEM]

I --> J[写回 WB]

K[前端流水线<br>分支预测,指令缓存等] --> L[乱序执行引擎<br>寄存器重命名,调度等]

L --> M[后端流水线<br>多个执行单元,存储器访问等]

L -.-> N[重排序缓冲区<br>确保顺序退休]1. 经典5级流水线(RISC处理器的起点)

这是教学和早期RISC处理器(如MIPS)中最经典的模型,对应上图上半部分:

- 1.IF:指令提取。从指令缓存中取指令。

- 2.ID:指令解码。解析指令,并读取寄存器操作数。

- 3.EX:执行。在ALU(算术逻辑单元)中进行计算。

- 4.MEM:存储器访问。如果需要,读写数据缓存。

- 5.WB:写回。将结果写回寄存器。

2. 现代台式机CPU:超长流水线(10级到20+级)

为了追求极高的时钟频率,现代高性能CPU(如Intel Core和AMD Ryzen系列)将流水线划分得极其细致,对应上图下半部分的复杂结构。

- •Intel NetBurst架构(Pentium 4) :这是一个极端例子,其Prescott核心的流水线达到了31级。这使得它的时钟频率潜力非常高(尽管带来了其他严重问题)。

- •现代主流CPU :通常在15级到20级左右。例如,Intel的Skylake架构大约14-16级,AMD的Zen架构大约19级。

3. 嵌入式/低功耗CPU:较短流水线(通常少于10级)

这类CPU(如ARM Cortex-A5/A7)优先考虑能效比和低延迟,而非绝对峰值性能。

- •级数 :通常在8级到10级左右。

流水线级数长短的权衡

这是一个典型的工程权衡,核心是时钟频率 、吞吐率 和单指令延迟之间的博弈。

| 特性 | 长流水线(例如15-20+级) | 短流水线(例如5-10级) |

|---|---|---|

| 优点 | 1. 高时钟频率潜力 : 每一级的电路逻辑非常简单,信号传播延迟短,允许更高的时钟频率。 2. 高吞吐率: 在理想情况下,指令完成的"带宽"很高。 | 1. 低单指令延迟 : 一条指令从开始到结束所需的时间(延迟)更短。 2. 高效能比 : 硬件更简单,功耗更低。 3. 对分支预测错误惩罚小(见下文)。 |

| 缺点 | 1. 高分支误预测惩罚 : 一旦CPU预测错了分支(if/else,循环),需要清空整个长长的流水线,损失十几个甚至几十个时钟周期。 2. 高功耗 : 更多的流水线寄存器消耗更多功耗。 3. 设计复杂。 | 1. 时钟频率上限较低: 每一级的逻辑组合更复杂,限制了频率提升。 |

核心挑战:"分支预测错误惩罚"

这是长流水线最主要的代价。

- •惩罚 = 流水线深度

- •在5级流水线中,预测错误可能损失约5个周期。

- •在20级流水线中,预测错误可能损失约20个周期!

- •因此,现代CPU必须配备极其精准的分支预测器,否则高频率的优势会被频繁的清空流水线操作所抵消。

历史案例与趋势:Pentium 4的教训

Intel的Pentium 4(NetBurst架构)是追求超长流水线的典型。

- •目标:通过超长流水线(从Willamette的20级到Prescott的31级)来冲击极高的时钟频率(最终达到3.8GHz以上)。

- •问题 :1.分支预测惩罚巨大 :一旦预测错误,性能损失惨重。2.功耗和发热失控:高频和长流水线导致功耗密度急剧上升,著名的"功耗墙"问题限制了其进一步发展。

- •教训:单纯追求流水线深度和时钟频率是不可持续的。后续的Core架构又回归到了相对更短、更高效的流水线设计。

现代趋势:不再是简单地增加或减少级数,而是采用更复杂的结构,如:

- •解耦的超标量乱序执行:流水线被分为"前端"、"乱序执行引擎"、"后端"等多个部分,各部分可独立优化。

- •宏操作(uops)缓存:将解码后的指令缓存起来,绕过复杂的解码流水线。

- •更智能的分支预测 和推测执行。

总结

- •流水线级数 是CPU在高吞吐率 和低延迟/低功耗之间权衡的关键设计选择。

- •长流水线 (~15-20级)旨在实现高频率和高吞吐率,但代价是更高的分支预测错误惩罚和功耗。

- •短流水线 (~5-10级)旨在实现高能效和低延迟,但牺牲了峰值频率。

- •现代高性能CPU通过极其复杂的技术(如乱序执行、高级分支预测)来克服长流水线带来的负面影响。

Cache一致性

问:Cache一致性协议

答:

已深度思考(用时7秒)

好的,用户这次问的是"Cache一致性协议"。从对话历史来看,用户对计算机体系结构的基础概念有持续的兴趣,而且问题越来越深入------从昇腾NPU、LLM算子到CPU流水线,现在深入到多核处理器并行性的核心问题。这可能是计算机专业的学生、开发者或硬件爱好者,在系统性地夯实底层知识。

用户表面上是询问协议的定义,但结合之前讨论过CPU流水线和多级Cache,ta的真实需求可能更具体:理解多核CPU如何高效协同工作而不出错。尤其是在现代多核处理器普及的背景下,ta可能遇到过并发编程的问题(比如数据竞争),想从硬件层面理解解决方案。深层需求或许是:为并发编程、性能优化或软硬件设计打下基础。

之前的回复都采用了"概述-核心问题-实现方案-总结"的结构,且用户没有负面反馈,说明ta认可这种由浅入深的框架。这次需要延续清晰的结构,但重点突出"共享内存"这个场景如何引发问题,以及协议如何像交通规则一样解决冲突。

用户对技术细节接受度高(比如之前解释了LLM算子的底层优化),所以可以引入MESI这样的具体协议状态机细节。但要用生活化比喻(如便签)降低理解门槛,同时明确状态转换的逻辑和硬件行为。最后要点明"性能与复杂性权衡"的设计哲学,与CPU流水线等前文形成知识串联。

安全方面没问题,这是纯技术问题。回复要避免过度展开具体厂商实现(如Intel的MESIF),聚焦通用原理。

好的,Cache一致性协议是支撑所有现代多核处理器(Chip-Multiprocessor, CMP)能够高效、正确运行的基石级技术。它非常核心,也稍微有点复杂,我们一步步来解释。

核心问题:为什么需要Cache一致性?

首先,想象一个场景:一个双核系统,每个核心都有自己的私有L1缓存,但它们共享同一块主内存。

- 核心A和核心B都读取了内存地址

X处的数据,于是X的副本分别存在于核心A的Cache和核心B的Cache中。 - 核心A现在计算并修改了

X的值(比如X = X + 1)。这个修改首先发生在我核心A的私有Cache中。 - 此时,问题来了:•核心A的Cache中的

X已经更新为新值。•核心B的Cache中的X还是旧的脏数据。•主内存中的X也是旧数据。

这就导致了数据不一致 。如果核心B继续去读它Cache里的X,它读到的是一个错误的值,程序就会出错。

Cache一致性协议 就是为了解决这个问题而诞生的。它是一套由硬件实现的、所有核心的Cache控制器都必须遵守的规则,用于跟踪每个Cache行的状态,并在数据被修改时自动通知其他核心,从而维护多个Cache副本之间的一致性。

核心概念:Cache行的状态

协议的核心是为每一个Cache行(Cache Line,Cache管理数据的基本单位,通常为64字节)维护一个状态机。这个状态机由几个状态和触发状态转换的消息构成。

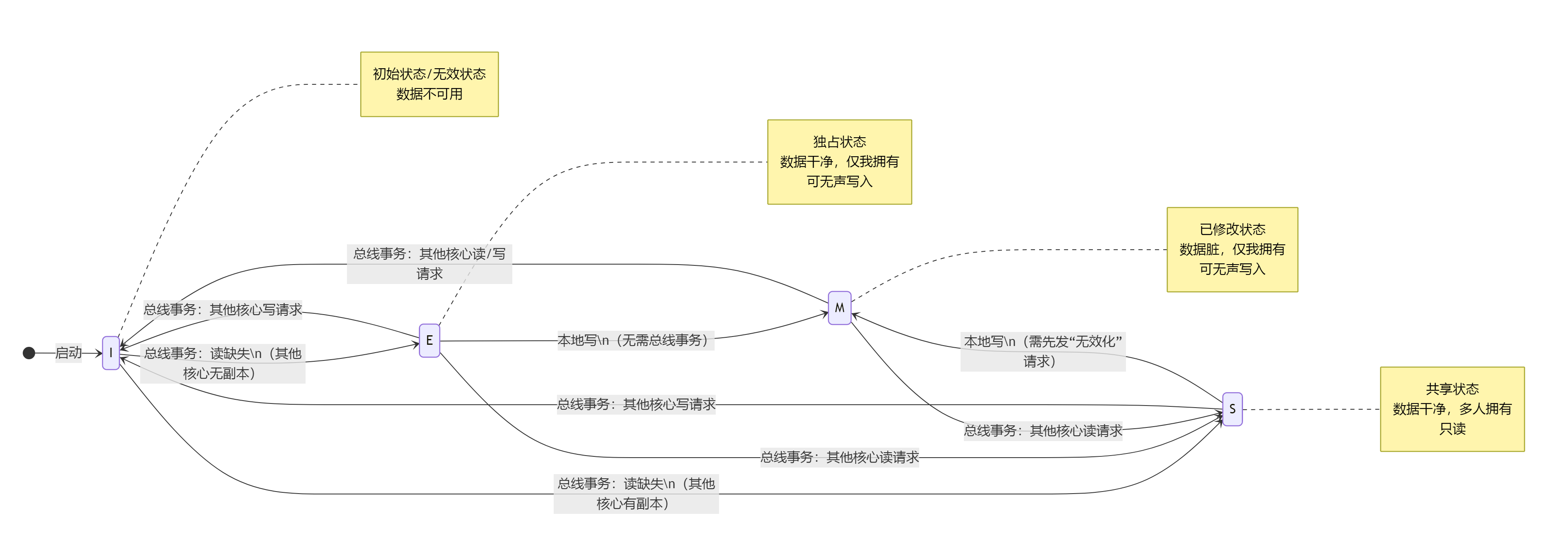

最著名、最经典的协议是MESI协议,我们就以它为例来详细说明。

MESI协议的四种状态

MESI是四种状态的首字母缩写:

- M - Modified(已修改) •含义 :当前Cache行中的数据已经被修改 ,与主内存中的数据不同(是"脏"数据)。并且,它是系统中唯一有效 的副本(其他核心的Cache中没有这个数据的副本)。•权限 :拥有该Cache行的核心可以随意读写它。如果被替换,必须写回主内存。•类比:你从图书馆(主内存)借了一本唯一的书,并在上面做了笔记。只有你拥有这本书的最新版本。

- E - Exclusive(独占) •含义 :当前Cache行中的数据与主内存一致 ,并且是系统中唯一的副本 。其他核心的Cache中没有这个数据。•权限 :拥有该Cache行的核心可以"安静地"读写它。如果要写,可以直接将状态从

E转为M,而无需通知其他核心,因为我知道没有其他副本。•类比:你从图书馆借了一本书,并且你是唯一借这本书的人。书是干净的,你可以在上面做笔记(写),但需要先告知图书馆(状态改变)。 - S - Shared(共享) •含义 :当前Cache行中的数据与主内存一致 ,但系统中可能存在多个副本 (多个核心的Cache中都有这个数据)。•权限 :核心只能读 这个数据。如果想要写 ,必须先通知其他核心,使它们的副本失效 。•类比:你和几个人一起看同一本书的复印件。大家都只能读。如果你想修改内容,必须先把所有人的复印件都收回来销毁,然后在你自己的复印件上修改。

- I - Invalid(无效) •含义 :当前Cache行中的数据是过时的、无效的 。不能使用它。•权限 :无。如果需要读这个数据,必须重新从其他Cache或主内存中获取。•类比:你有一份文件的复印件,但被告知原件已被更新,你的复印件作废了。

MESI协议如何工作:消息传递与状态转换

各个核心的Cache控制器通过一条特殊的总线(如总线嗅探机制)来通信。它们会"偷听"总线上其他核心发出的关于Cache操作的请求,并根据请求和自身Cache行的状态来更新状态。

下图直观地展示了MESI协议中,一个Cache行状态转换的完整工作流程:

stateDiagram-v2

direction LR

[*] --> I : 启动

I --> E : 总线事务:读缺失\n(其他核心无副本)

I --> S : 总线事务:读缺失\n(其他核心有副本)

E --> M : 本地写\n(无需总线事务)

E --> S : 总线事务:其他核心读请求

E --> I : 总线事务:其他核心写请求

S --> I : 总线事务:其他核心写请求

S --> M : 本地写\n(需先发"无效化"请求)

M --> I : 总线事务:其他核心读/写请求

M --> S : 总线事务:其他核心读请求

note right of I

初始状态/无效状态

数据不可用

end note

note right of E

独占状态

数据干净,仅我拥有

可无声写入

end note

note right of S

共享状态

数据干净,多人拥有

只读

end note

note right of M

已修改状态

数据脏,仅我拥有

可无声写入

end note关键点:

- •读未命中 :当一个核心需要读取一个数据,但自己的Cache是

I状态时,它会发起一个"总线读"事务。其他核心的Cache控制器会"嗅探"到这个请求。•如果其他核心有这份数据且状态是M(脏数据),这个核心会拦截 请求,先将自己的脏数据写回内存,然后将状态转为S,并提供数据。请求方和提供方都变为S。•如果其他核心有这份数据且状态是E或S,它们会声明"我有副本",然后所有拥有副本的核心(包括新加入的)都变为S状态。如果之前没有副本,则请求方变为E。 - •写操作 :当一个核心要写入一个数据时:•如果状态是

E或M,说明我是唯一所有者,可以直接悄悄地写(状态变为或保持M)。•如果状态是S,说明有多个副本。核心必须先在总线上发起一个"无效化"请求,让其他所有核心将它们的Cache行状态变为I,然后它才能执行写操作,并将自己的状态变为M。

MESI协议的变种:MOESI

为了进一步提升效率(比如减少不必要的写回主存),在MESI基础上还有一个更强大的协议:MOESI,它增加了一个状态:

- •O - Owned(拥有) •这个状态类似于

S(共享)和M(已修改)的结合体。•数据是"脏"的(与主内存不一致),但系统中存在多个副本(共享)。•处于O状态的Cache是数据的"负责人"。当其他核心需要读数据时,由它提供数据;当Cache行被替换时,由它负责写回主内存。•这避免了在共享"脏"数据时必须先写回主内存的开销,提升了性能。AMD的CPU广泛使用了MOESI或其变种。

总结

| 特性 | 描述 |

|---|---|

| 目标 | 保证多核系统中,每个核心的Cache数据副本是一致的。 |

| 方法 | 为每个Cache行维护一个状态(M、E、S、I),通过总线嗅探和消息传递来自动触发状态转换。 |

| 核心思想 | 写传播 (一个核心的写入必须最终让其他核心知道)和写串行化(所有核心看到的写入顺序必须一致)。 |

| 重要性 | 没有它,多核编程几乎是不可能的。你写的程序之所以能在多核CPU上正确运行,底层全靠它在默默工作。 |

简单来说,Cache一致性协议就是多核CPU内部Cache之间的"交通规则"和"通信协议",确保了整个系统在高速并行运转时不会因为数据混乱而"撞车"。