见人见多了想看海,看海看多了想见人,那如果好看的海和有趣的人都看见了,接下来想干什么呢?

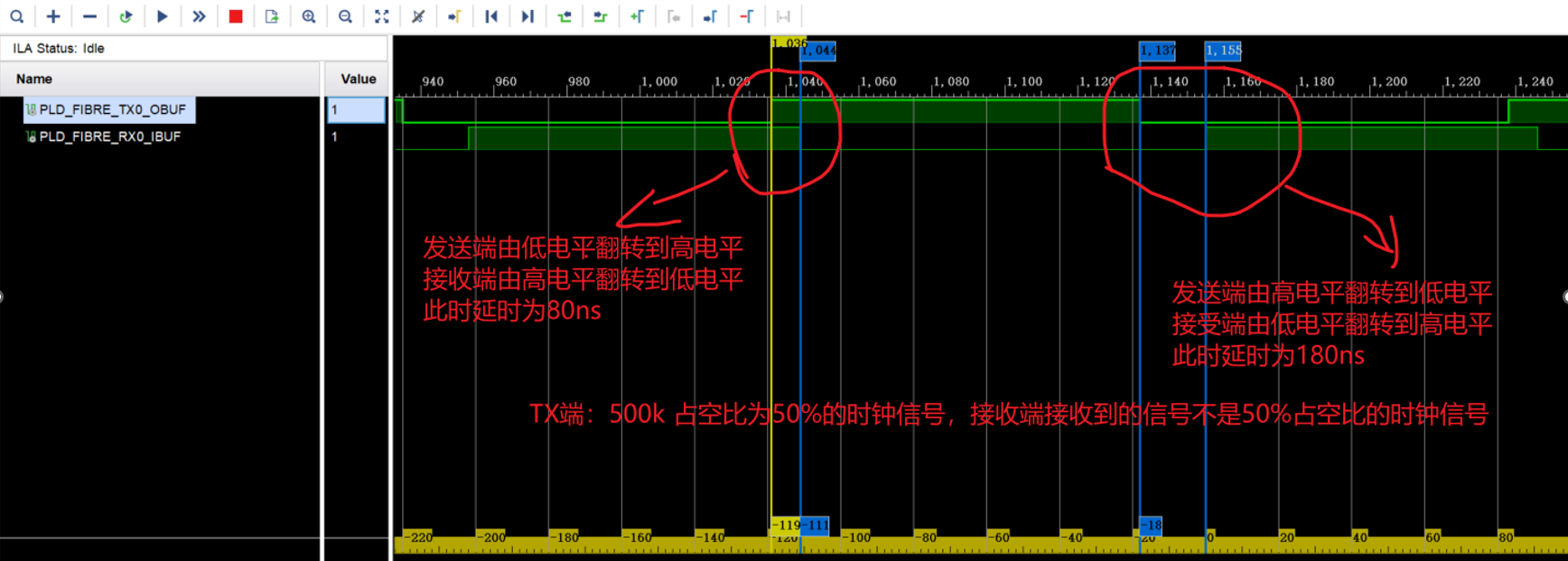

进入新工作时,遇到光纤收发器接口传输数据时,上升沿的跳变和下降沿跳变不一致,及当发送端发送一个占空比为50%的方波时,使用接收端接收的方波占空比不再是50%。

问题如下:

接收端由高电平翻转到低电平的延时为80ns,但是由低电平翻转到高电平的延时为180ns

图1 发送端和接收端方波占空比不一致

图1 发送端和接收端方波占空比不一致

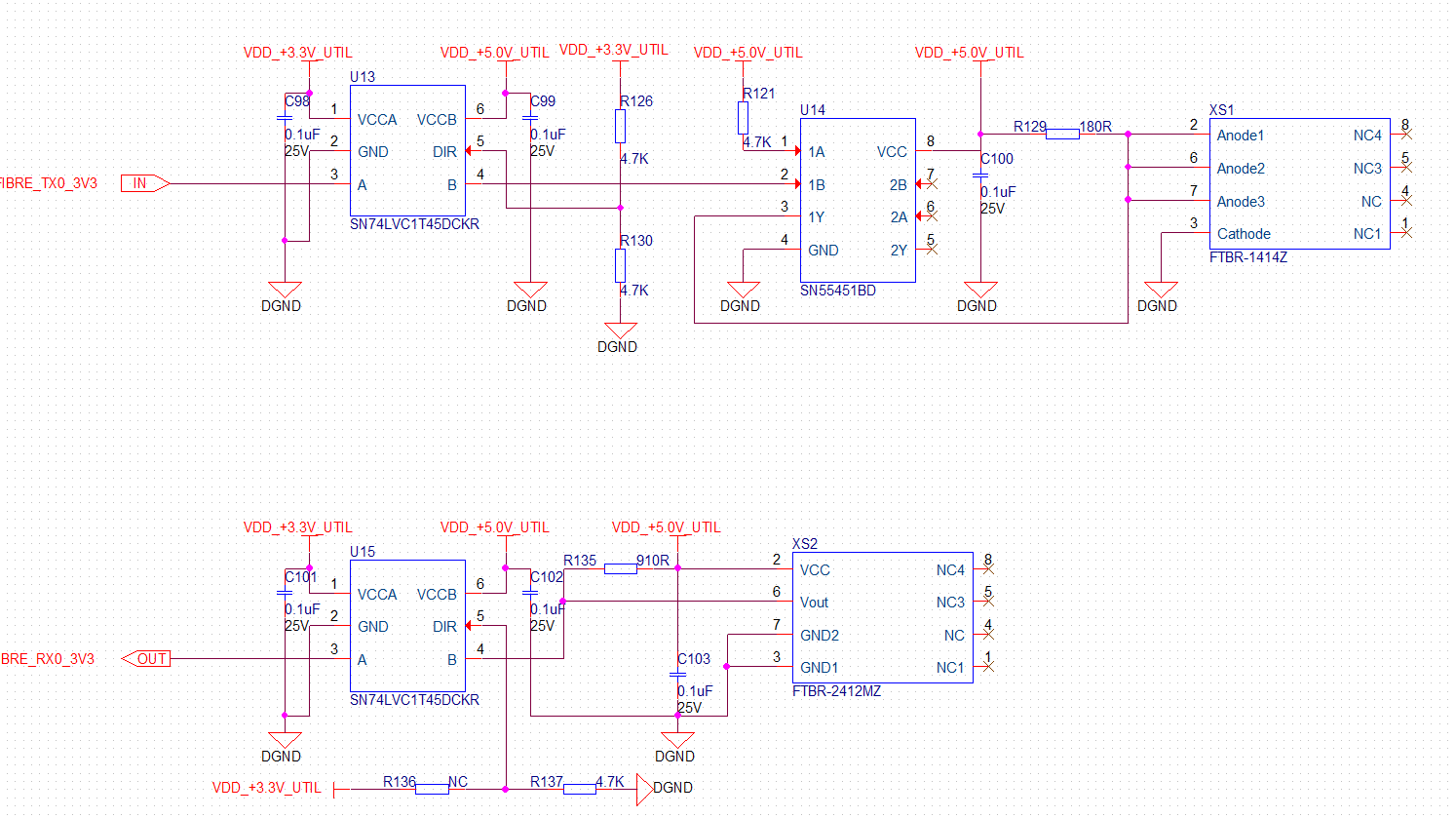

设计原理图:

图2 光纤收发器原理图

图2 光纤收发器原理图

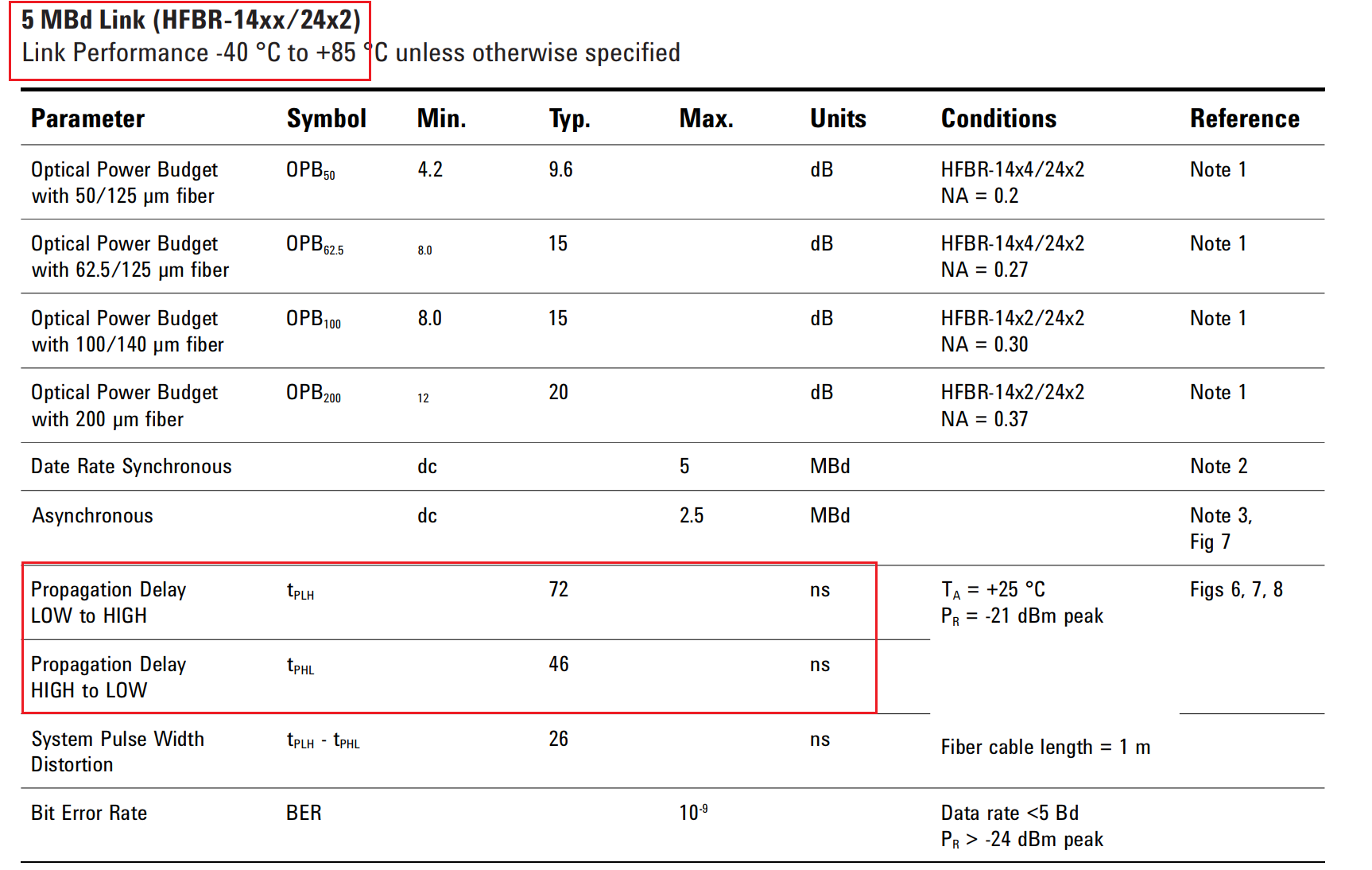

查询手册时发现:发送端和接收端的延时本来就不一致,但是不会像图中这么大,手册中典型值如下:

图3 datasheet参数

图3 datasheet参数

开始时以为是R129设置错误导致的(原来为4.7K),找FAE询问也建议减小R129的阻值,看延时会不会变化,但是卸下来测量发现板子上上件的阻值为47Ω.。。。

调试时发现,R135和R129上件数值和手册中推荐值不一样,其中R129上件的阻值太小导致使用时发热,R135上件的阻值太大,导致接收到上升沿不够陡峭,导致了方波占空比失真的问题。

以上:

5M的速率限制应该也是因为上下沿的延时不一致导致的