简介

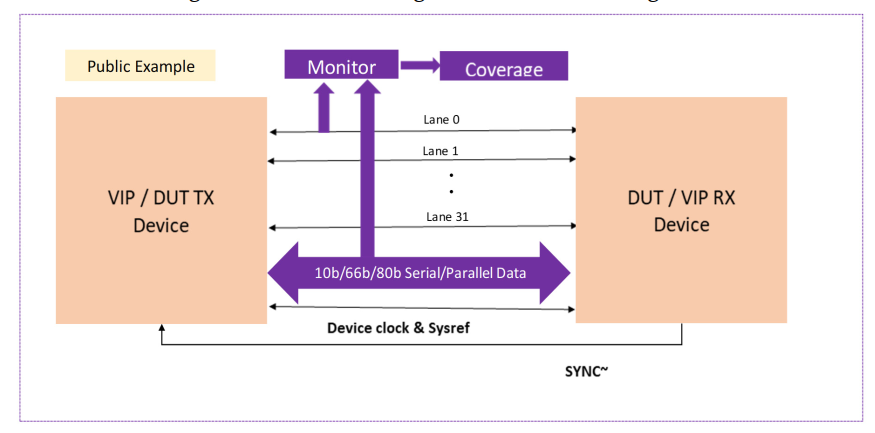

Synopsys JESD204 VIP支持协议版本JESD204A、JESD204B、JESD204C。JESD204B协议支持子类Subclass0、1、2,JESD204C协议支持64b66b、64b80b编码,此外还包含链路初始化、重建、测试模式等功能。

VIP组件包括jesd204_agent_svt、jesd204_ll_svt、jesd204_pl_svt、jesd204_tl_svt,其中jesd204_agent_svt为整体的RX或TX设备,后面三个svt分别对应独立的链路层、物理层和传输层。

VIP可以作为TX也可以作为RX,通过lane和DUT连接,对于一些没有PHY的场景连接形式也可以为并行。

jesd204_agent_svt在传输层、链路层和物理层分别有Analysis Port,可以供数据比对或覆盖率统计,通常使用传输层观测口即可。

• tx_tl_xact_observed_port

• rx_tl_xact_observed_port

• tx_ll_xact_observed_port

• rx_ll_xact_observed_port

• tx_pl_xact_observed_port

• rx_pl_xact_observed_port

jesd204_agent_svt在传输层、链路层和物理层分别有Callback方法,可以用来注入用户信息。

• svt_jesd204_tl_callback

• svt_jesd204_ll_callback

• svt_jesd204_pl_callback

类

组件类

svt_jesd204_agent

agent可以是一个TX或RX设备,首先包含顶层sequencer和状态。

svt_jesd204_virtual_sequencer virt_seqr;

svt_jesd204_status shared_status;然后包含transport/link/phy layer的子组件。不加后缀就是driver,_monitor是监视器。剩余包含一些callback,不再列举。

svt_jesd204_tl tl;

svt_jesd204_tl_monitor tl_mon;

svt_jesd204_transaction_sequencer tl_seqr;

svt_jesd204_ll ll;

svt_jesd204_ll_monitor ll_mon;

svt_jesd204_transaction_sequencer ll_seqr;

svt_jesd204_pl pl;

svt_jesd204_pl_monitor pl_mon;

svt_jesd204_transaction_sequencer pl_seqr;配置类

svt_jesd204_agent_configuration

用于集成svt_jesd204_agent时进行配置,是svt_jesd204_configuration的子类,子类的新变量只有覆盖率、调试信息使能,协议参数模式等相关配置都在父类中。

svt_jesd204_configuration

no_of_lane:指定link里的lane数量。

rand bit[5:0] no_of_lane = 1;device_mode:设备模式,支持TX和RX。

interface_type:接口模式,可配为SERIAL_MODE、PARALLEL_MODE。

mode:每个frame单采样点/多采样点,可配为FUNDAMENTAL_MODE、OVERSAMPLED_MODE。

svt_jesd204_types::device_mode_enum device_mode = svt_jesd204_types::TX_DEVICE;

svt_jesd204_types::interface_type_enum interface_type = svt_jesd204_types::SERIAL_MODE;

svt_jesd204_types::mode_enum mode = svt_jesd204_types::FUNDAMENTAL_MODE;rev_num:协议版本,支持JESD204A、JESD204B、JESD204C。

subclass_type:协议子类,支持subclass0、subclass1、subclass2。

coding_type:协议编码模式,支持8b10b、64b66b、64b80b。

rand svt_jesd204_types::version_enum rev_num = svt_jesd204_types::JESD204_VER_B;

rand svt_jesd204_types::subclass_type_enum subclass_type = svt_jesd204_types::SUBCLASS_0;

rand svt_jesd204_types::coding_type_enum coding_type = svt_jesd204_types::JESD204_8B_10B_CODING;k_multiframe :协议参数K,每个多帧里的帧数。

m_converter :协议参数M,有多少个转换器。

s_sample :协议参数S,每帧的采样点。

f_octets :协议参数F,每帧总计的8bit数。

data_sample_size :协议参数N,采样点bit数。

net_sample_size :协议参数N',采样点对齐后bit数。

num_of_ctrl_word :协议参数CF,每帧补的点。

num_of_ctrl_bits :协议参数CS,每个采样点补的点。

rand bit[31:0] k_multiframe = 1;

rand bit[8:0] m_converter = 1;

rand bit[5:0] s_sample = 1;

rand bit[8:0] f_octets = 1;

rand bit[5:0] data_sample_size = 1;

rand bit[5:0] net_sample_size = 4;

rand bit[5:0] num_of_ctrl_word = 0;

rand bit[1:0] num_of_ctrl_bits = 0;hd:对应协议HD

num_of_multiframe_in_ila :建连时发送几个多帧。

rand bit hd = 1'b0;

rand bit[31:0] num_of_multiframe_in_ila = 4;

bit[1:0] stop_tx_dummy_data_driving = 0;

bit[1:0] sh_emb_user_defined_data = 0;svt_jesd204_types

类中包含各种枚举变量定义。

包含设备模式TX、RX、协议subclass0/1/2、版本204A/B/C、编码8b10b/64b66b/64b/80b、接口模式串/并等信息。

typedef enum bit [1:0] {

TX_DEVICE = `SVT_JESD204_TX_DEVICE,

RX_DEVICE = `SVT_JESD204_RX_DEVICE

} device_mode_enum;

typedef enum bit[1:0] {

SUBCLASS_0 = `SVT_JESD204_SUBCLASS_0 ,

SUBCLASS_1 = `SVT_JESD204_SUBCLASS_1 ,

SUBCLASS_2 = `SVT_JESD204_SUBCLASS_2

} subclass_type_enum;

typedef enum bit[1:0] {

JESD204_VER_A = `SVT_JESD204_VER_A,

JESD204_VER_B = `SVT_JESD204_VER_B,

JESD204_VER_C = `SVT_JESD204_VER_C

} version_enum;

typedef enum bit[1:0] {

JESD204_8B_10B_CODING = `SVT_JESD204_8B_10B_CODING,

JESD204_64B_66B_CODING = `SVT_JESD204_64B_66B_CODING,

JESD204_64B_80B_CODING = `SVT_JESD204_64B_80B_CODING

} coding_type_enum;

typedef enum bit {

SERIAL_MODE = `SVT_JESD204_SERIAL_MODE ,

PARALLEL_MODE = `SVT_JESD204_PARALLEL_MODE

} interface_type_enum;包含link、lane状态,1个link包含多个lane。

typedef enum bit[2:0] {

LINK_IDLE = `SVT_JESD204_LINK_IDLE,

LINK_ACTIVE = `SVT_JESD204_LINK_ACTIVE

} link_state_enum;

typedef enum bit[2:0] {

LANE_IDLE = `SVT_JESD204_LANE_IDLE ,

LANE_ACTIVE = `SVT_JESD204_LANE_ACTIVE

} lane_state_enum;传输类

svt_jesd204_transaction

cmd_type:指定传输类型。

rand cmd_type_enum cmd_type = CODE_GROUP_SYNC_COMMAND;

typedef enum bit[3:0] {

LONG_TEST_PATTERN_COMMAND = `SVT_JESD204_LONG_TEST_PATTERN_COMMAND,

SHORT_TEST_PATTERN_COMMAND = `SVT_JESD204_SHORT_TEST_PATTERN_COMMAND,

LINK_LAYER_TEST_COMMAND = `SVT_JESD204_LINK_LAYER_TEST_COMMAND,

CODE_GROUP_SYNC_COMMAND = `SVT_JESD204_CODE_GROUP_SYNC_COMMAND,

ILA_COMMAND = `SVT_JESD204_ILA_COMMAND,

DATA_COMMAND = `SVT_JESD204_DATA_COMMAND,

CMD_CHANNEL_CODE = `SVT_JESD204_CMD_CHANNEL_CODE

} cmd_type_enum;sample:采样点数组,宽度为N',假如是M个转换器需要自行把数据穿插好。

ctrl/tail_bits:控制位和结尾位数组,深度和sample数组相同,宽度分别为CS、T,可以参照协议公式N′=N+CS+T。

rand bit [`SVT_JESD204_MAX_RESOLUTION-1:0] sample[];

rand bit [`SVT_JESD204_MAX_NUM_CONTROL_BITS-1:0] ctrl_bits[];

rand bit [`SVT_JESD204_MAX_NUM_TAIL_BITS-1:0] tail_bits[];接口

svt_jesd204_if

TX和RX设备均使用svt_jesd204_if接口,其实DUT连接只需要dp、dn、sync和sysref即可,其余主要用于调试。

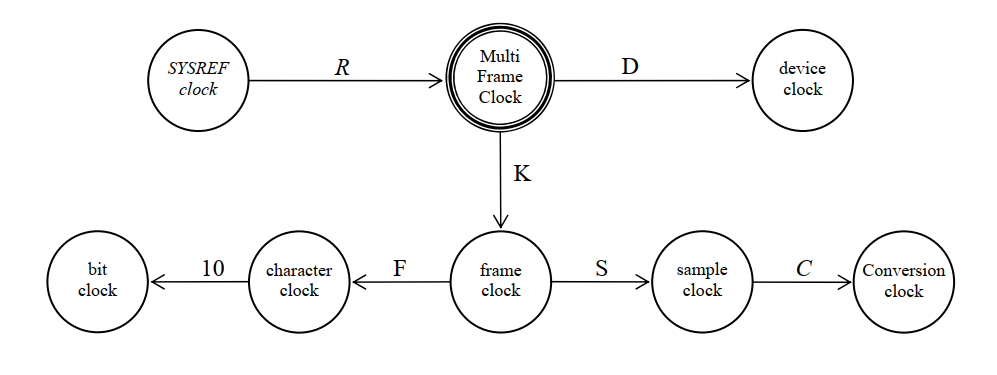

interface svt_jesd204_if (input logic reset);dev_clk:device clock设备时钟,对于TX和RX都是输入。

frame_clk:帧时钟,对应一次F参数。

lmfc_clk:LMFC多帧时钟。

lemc:204C新增帧概念。

adjustment_clk:调整时钟,Subclass2新增。

sample_clk:采样时钟,对应一次N'参数。

logic dev_clk;

logic frame_clk;

logic lmfc_clk;

logic adjustment_clk;

logic sample_clk;sync:协议中SYNC~,RX输出、TX输入。

sysref:Subclass 1新增,对于TX和RX都是输入。

logic sync;

logic sysref;

logic [3:0] soft_sync;

logic soft_sync_interrupt;lane:每个lane对应单独的子interface。由于interface不能按数组访问,所以可以通过get_lane_if方法获得指定lane的虚接口。

svt_jesd204_lane_if lane[`SVT_JESD204_MAX_NUM_LANE]();

function svt_jesd204_lane_vif get_lane_if(int lane_no);sample:采样值,即N。

logic [31:0] sample;svt_jesd204_lane_if

dp/dn:差分串行线。

logic dp;

logic dn;bit_clk:线速率时钟,即dp/dn的时钟

char_clk:字符时钟,假如8b/10b编码,那频率就是bit_clk的十分之一。

serdes_clk:并行serdes模式的时钟。

octet_clk:octet时钟,从波形上看就是char_clk。

logic bit_clk;

logic char_clk;

logic serdes_clk;

logic octet_clk;char_data:编码后的字符值,即10b。

octet_data:编码前octet值,即8b,和总interface中sample的区别是可以额外看到链路层的数据。

rd_value:disparity值,即8b10b编码中的RD+和RD-。

debug_state:链路状态,要ASCII格式查看,包括SYNC、ILA、DATA等(这个比较有用)。

logic [79:0] char_data;

logic [7:0] octet_data[8];

logic [1:0] rd_value[8];

logic [95:0] debug_state;最后放一张协议中的时钟关系图,以便于理解。