《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第十六篇内容

上一篇:FPGA基础知识(十五):Xilinx Clocking Wizard IP核完全指南--从基础到高级应用-CSDN博客

**下一篇:**关注我,第一时间获取更新!!

在FPGA设计中,高效的片上存储管理是提升性能的关键。Vivado提供了两个至关重要的存储IP核:Block Memory Generator 和 FIFO Generator。许多开发者在使用时存在困惑:它们到底有什么区别?何时该用哪一个?

今天,作为系列文章的第一篇,我们将深入探讨Block Memory Generator的核心定位,并详细解析其第一个配置页面------Basic。

1、Block Memory vs FIFO:架构师的选择

1.1 核心差异

Block Memory Generator 本质上是一个可随机访问的存储阵列 。你可以把它想象成一个高度可定制的硬件数组,通过地址线直接访问任意位置的数据。

FIFO Generator 则是一个先进先出的队列管理器。它更像一个传送带,数据按顺序进入,按相同顺序离开,你无法直接访问中间的数据。

1.2 接口设计的根本不同

让我们看看两者给用户暴露的接口差异:

// Block Memory典型接口(简单双端口)

input wire clk_a, clk_b;

input wire [ADDR_WIDTH-1:0] addra, addrb;

input wire [DATA_WIDTH-1:0] dina;

output wire [DATA_WIDTH-1:0] doutb;

input wire wea, ena, enb;

// FIFO典型接口

input wire wr_clk, rd_clk;

input wire [DATA_WIDTH-1:0] din;

output wire [DATA_WIDTH-1:0] dout;

input wire wr_en, rd_en;

output wire full, empty, almost_full, almost_empty;关键差异:

-

Block Memory有显式的地址线 (

addra,addrb) -

FIFO有状态标志 (

full,empty等),但没有地址线

2.3 何时选择哪个?决策流程图

需要存储数据吗?

├── 需要随机访问任意位置? → Block Memory

├── 只需要顺序存取? → FIFO

│ ├── 需要跨时钟域? → 异步FIFO

│ └── 同时钟域? → 同步FIFO

└── 两者都需要? → Block Memory + 自定义控制器

2.4 性能与资源考量

| 特性 | Block Memory | FIFO |

|---|---|---|

| 访问方式 | 随机访问 | 顺序访问 |

| 控制复杂度 | 需要自行管理地址 | 自动管理读写指针 |

| 灵活性 | 极高(可配为RAM/ROM) | 固定FIFO行为 |

| 资源占用 | 仅存储单元+必要逻辑 | 存储单元+指针管理逻辑 |

| 典型延迟 | 1-2时钟周期 | 1-2时钟周期 |

重要洞察:FIFO内部通常是用Block Memory实现的!当你使用FIFO Generator时,IP核自动为你生成了存储器和指针管理逻辑。这解释了为什么在复杂系统中,我们有时直接用Block Memory实现自定义缓冲结构。

2、Basic配置页面详解

打开Block Memory Generator IP核,首先映入眼帘的就是Basic页面。这里的每一个选择都决定了存储器的基本架构。

2.1 Component Name(组件名称)

建议:使用有意义的命名约定

-

包含类型、规格信息

-

示例:

bram_sdp_32kx8(简单双端口,32K深度,8位宽) -

避免使用

bram_0、bram_1这类无意义名称

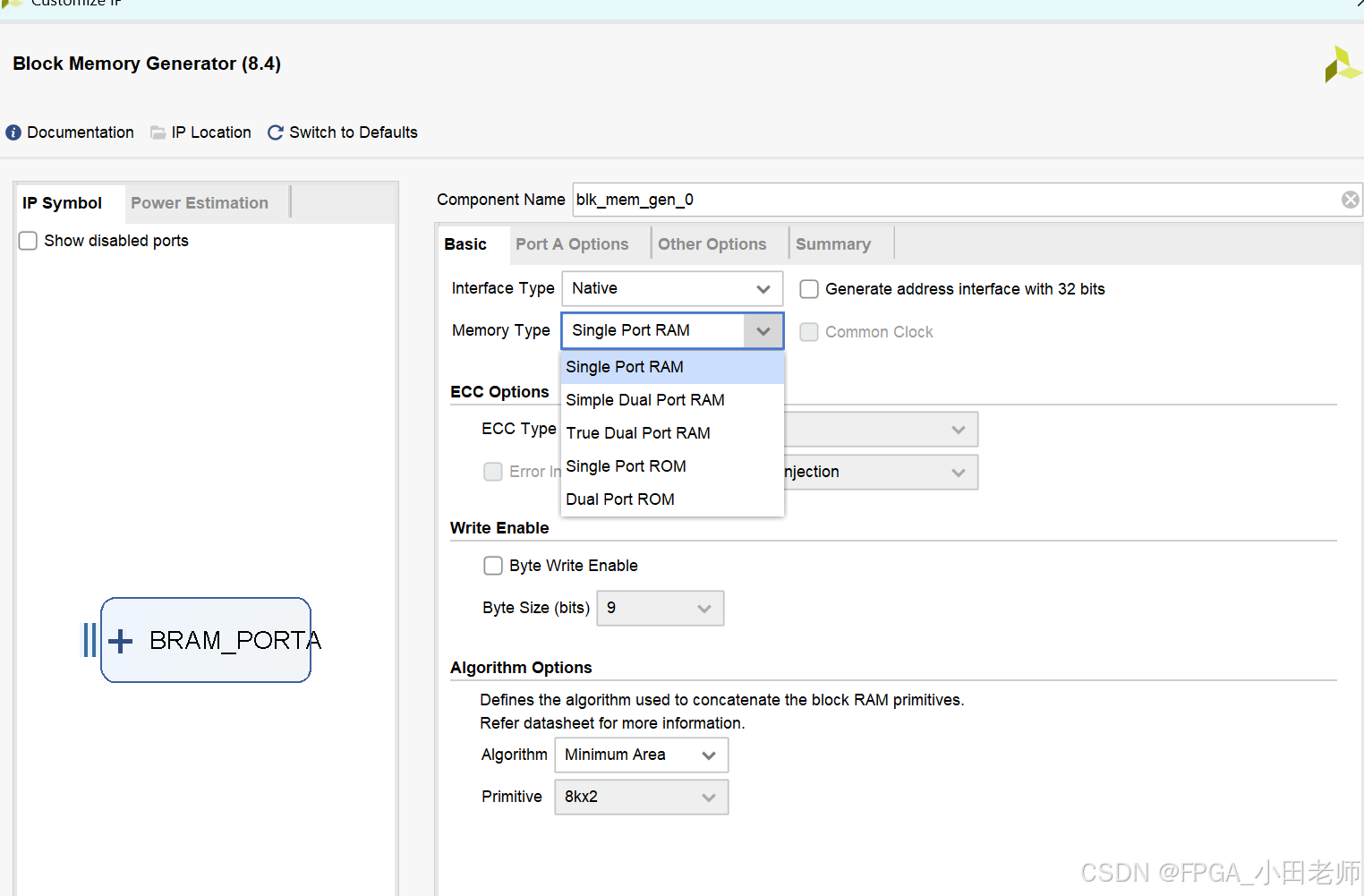

2.2. Memory Type(存储器类型) - 最重要的选择

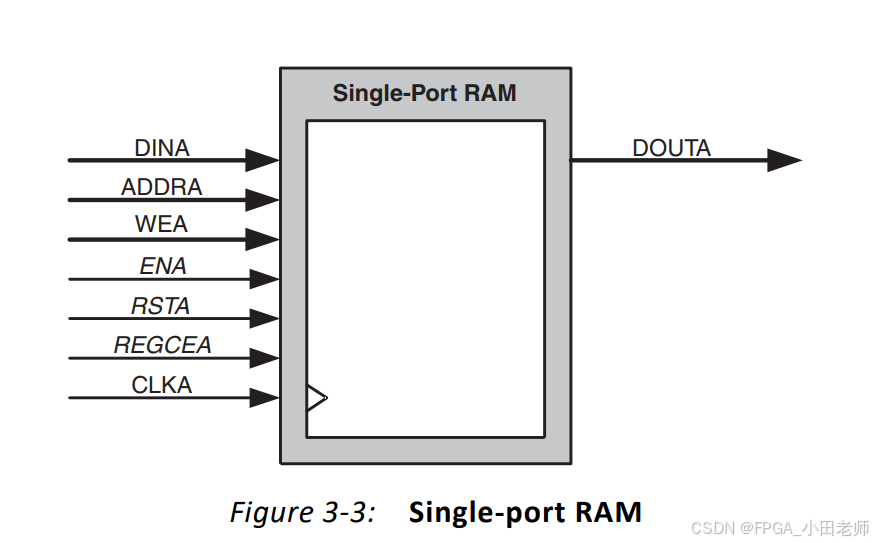

2.2.1 单端口RAM

特点:

-

一个时钟,一个地址端口

-

每个周期只能读或写,不能同时进行

-

最省资源的选择

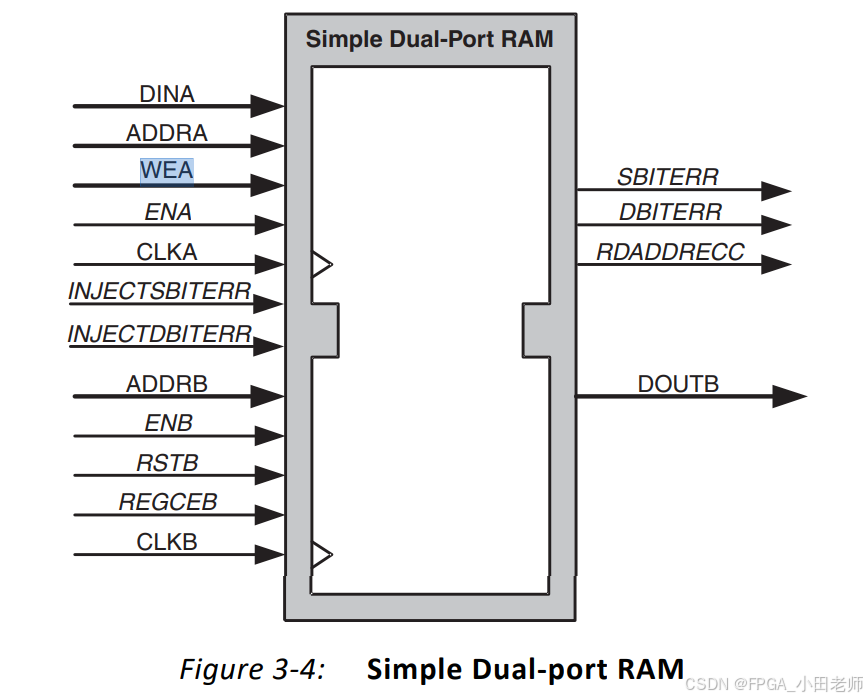

2.2.2 简单双端口RAM - 最常用

特点:

-

端口A专用于写,端口B专用于读

-

可配置独立时钟(用于跨时钟域)

-

位宽可不同(自动处理宽窄转换)

-

异步FIFO的基石

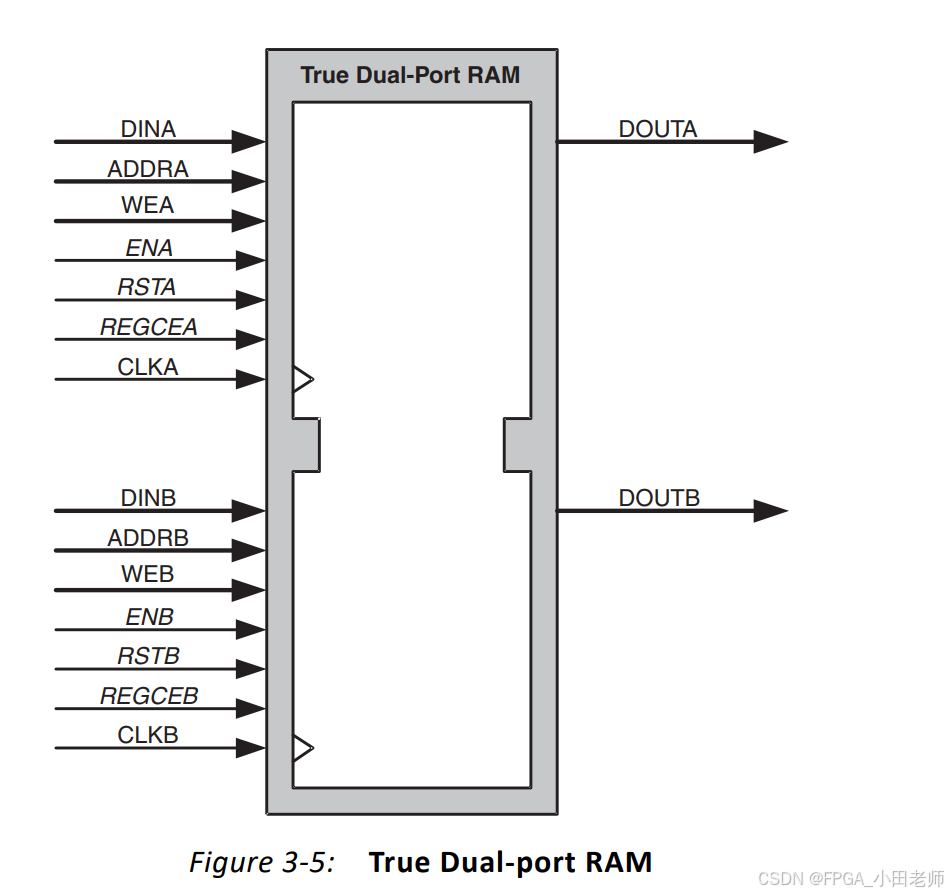

2.2.3 真双端口RAM

特点:

-

两个完全对称的端口,都可独立读写

-

支持并发操作(同时读A读B、同时写A写B等)

-

资源消耗最大,功能最强大

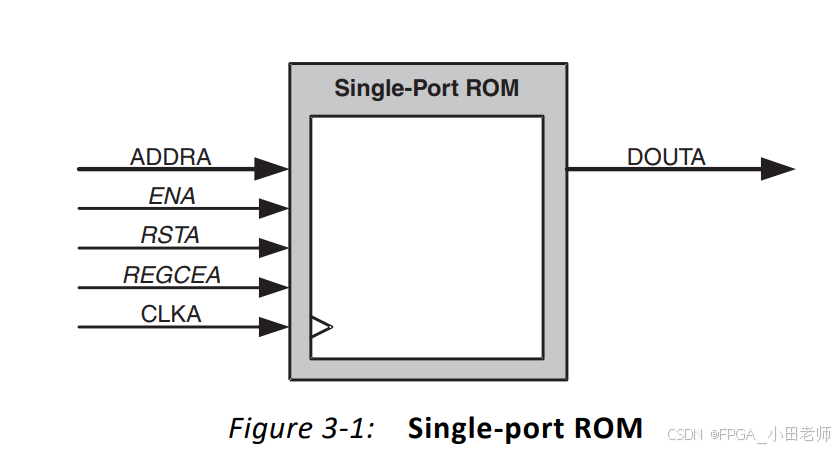

2.2.4 ROM类型

-

单端口/双端口ROM

-

必须通过.coe文件初始化

-

只读,无法写入(综合时会优化掉写逻辑)

2.3 ECC选项(错误校验与纠正)

适用场景:高可靠性要求的系统(航天、医疗、金融)

工作原理:

原始数据:32位

ECC编码后:32位数据 + 7位校验位 = 39位

存储空间:实际占用39位/存储单元优点:

-

检测并纠正单比特错误

-

检测双比特错误

代价:

-

增加约22%的存储开销(32→39位)

-

增加1个时钟周期的读延迟

-

需要额外的逻辑资源

配置建议:除非有明确的高可靠性需求,否则保持默认(不启用)。

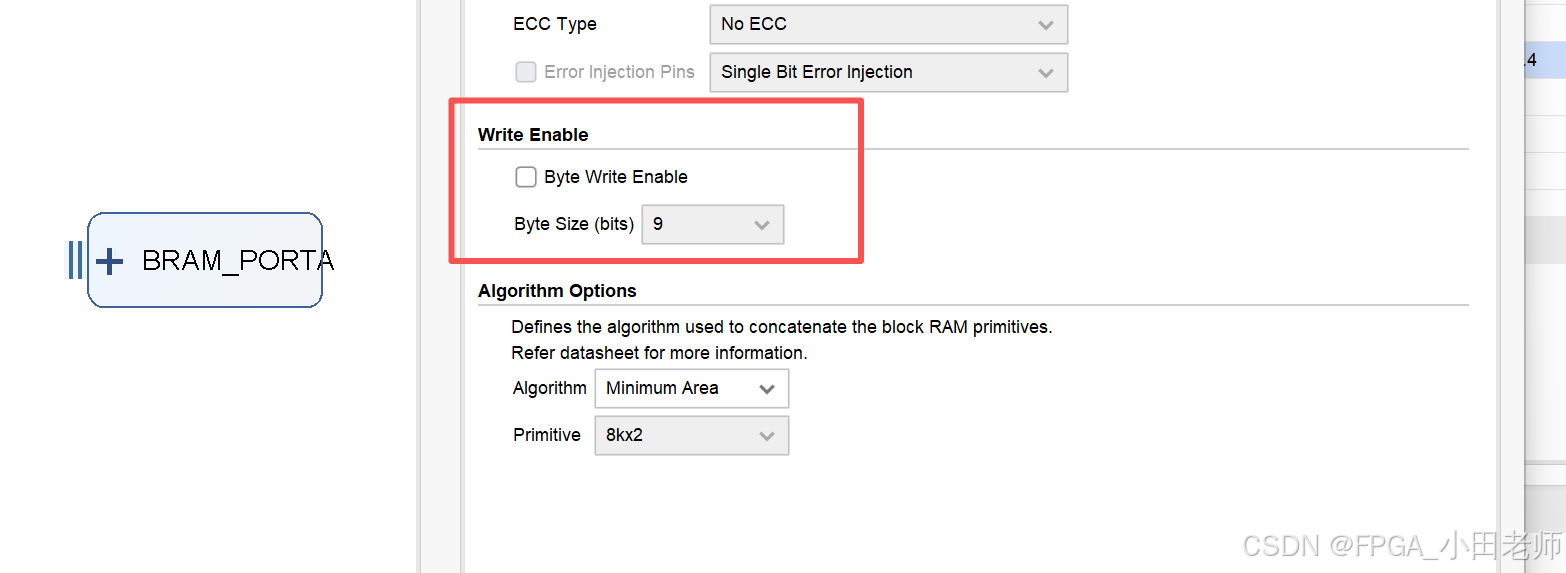

2.4 Write Enable & Algorithm Options(写使能与算法选项)

2.4.1 Byte Enable(字节使能)

作用:允许按字节粒度写入

// 假设32位数据,启用Byte Enable

input [31:0] dina;

input [3:0] wea; // 每个bit控制一个字节的写入

// wea = 4'b0011 表示只写入低16位(dina[15:0])

// 高16位保持原值典型应用:

-

CPU写内存(如MicroBlaze的D$接口)

-

仅更新部分数据字段

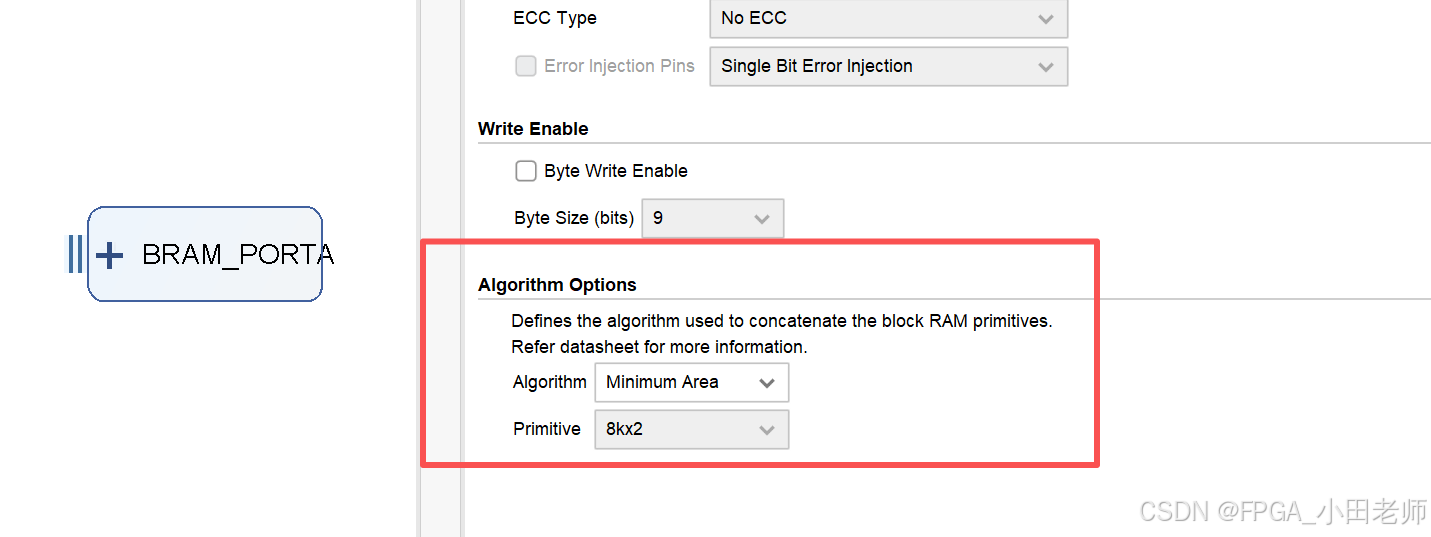

2.4.2 Algorithm(算法选项)

当你的存储器需求超过单个BRAM容量时,IP如何拼接多个BRAM:

| 算法选项 | 描述 | 适用场景 |

|---|---|---|

| Minimum Area | 尽量减少BRAM使用数量 | 资源紧张的设计 |

| Low Power | 优化功耗,可能使用更多BRAM | 低功耗应用 |

| Fixed Primitives | 强制使用指定数量的BRAM | 需要精确布局控制 |

性能影响分析:

-

Minimum Area:可能使用非对称分割,导致某些访问路径变长 -

Low Power:通过降低每个BRAM的利用率来减少翻转率 -

推荐 :对于大多数应用,选择

Minimum Area

3、实战配置示例

场景1:实现一个8K×32bit的异步数据缓冲

-

Component Name :

bram_async_buffer_8kx32 -

Memory Type :

Simple Dual Port RAM -

ECC Options: 不启用(默认)

-

Write Enable : 启用

Byte Enable(按需) -

Algorithm :

Minimum Area

理由:异步缓冲需要独立时钟,简单双端口是最佳选择。

场景2:视频处理的720p行缓冲

-

Component Name :

bram_line_buffer_1280x16 -

Memory Type :

True Dual Port RAM -

ECC Options: 不启用

-

Write Enable: 启用(可能需要按像素更新)

-

Algorithm :

Minimum Area或Low Power

理由:视频处理需要同时读写不同位置,真双端口是必须的。

4、常见陷阱与最佳实践

陷阱1:错误选择Memory Type

-

症状:设计功能异常或性能瓶颈

-

检查:确认是否需要同时读写、是否需要独立时钟

陷阱2:忽略Byte Enable的影响

-

症状:部分数据更新失败

-

解决:明确是否需要字节粒度控制,不需要则保持简单

最佳实践清单:

-

✅ 命名规范化,包含关键规格信息

-

✅ 优先考虑简单双端口,除非需要真双端口功能

-

✅ 除非必要,否则不启用ECC(避免不必要的延迟)

-

✅ 了解Byte Enable需求,避免过度设计

-

✅ 使用

Minimum Area算法,除非有特殊功耗要求

5 总结

Block Memory Generator是FPGA设计中构建高效存储系统的基石。理解其与FIFO的根本区别,是正确选择存储方案的前提。在Basic配置页面中,Memory Type的选择最为关键,它决定了存储器的基本架构和适用场景。

记住这个核心原则:FIFO是"开箱即用"的队列,Block Memory是"自由构建"的存储阵列。

在下一篇文章中,我们将深入Port A/Port B配置页面,探讨如何精确控制每个端口的时序、宽度和操作模式,敬请期待!