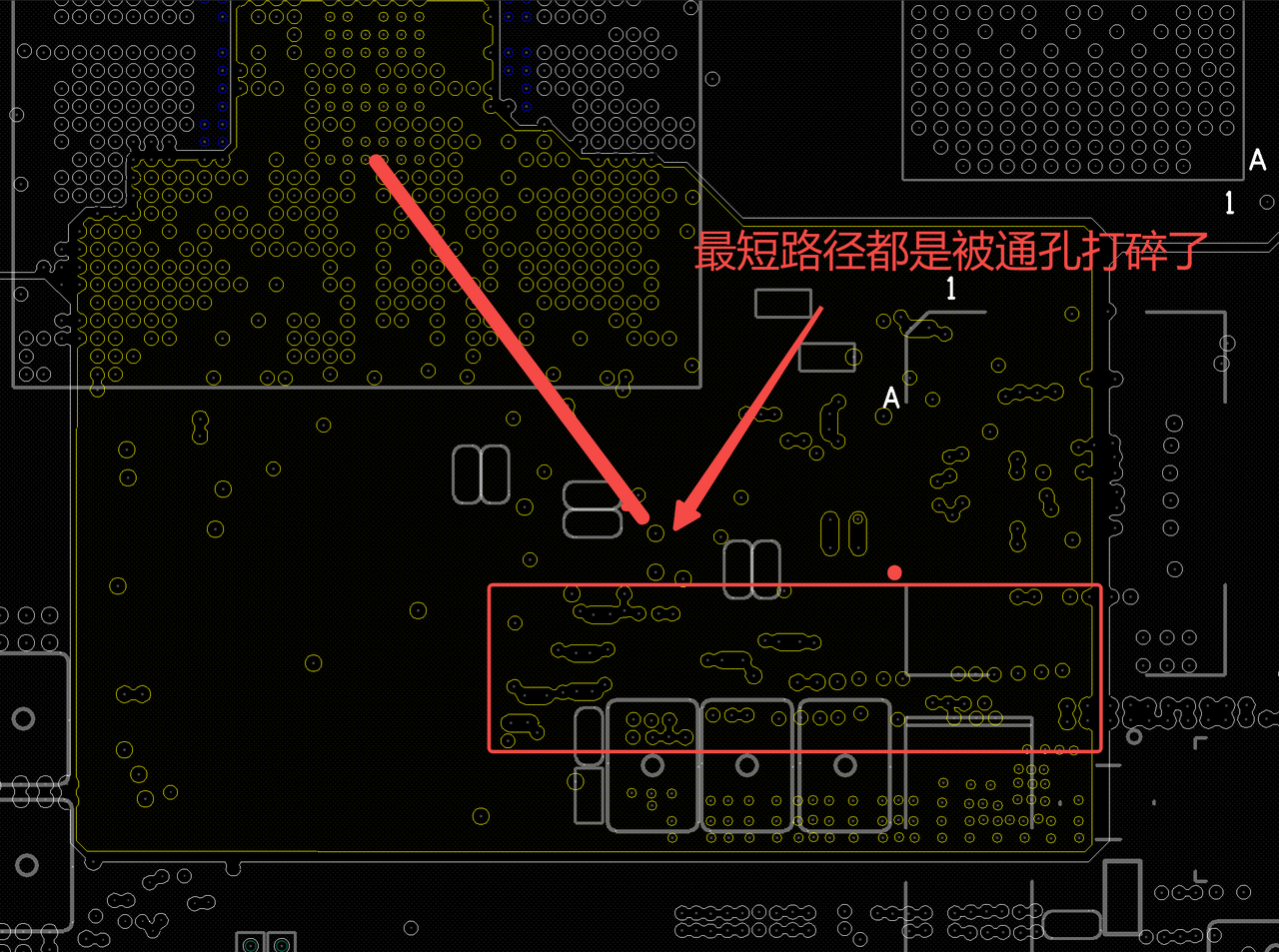

当电源层的铺铜路径被大量非自身信号的过孔打碎时,路径上的ESR会显著增加,并且会对该路电源的PDN表现产生明确的负面影响。

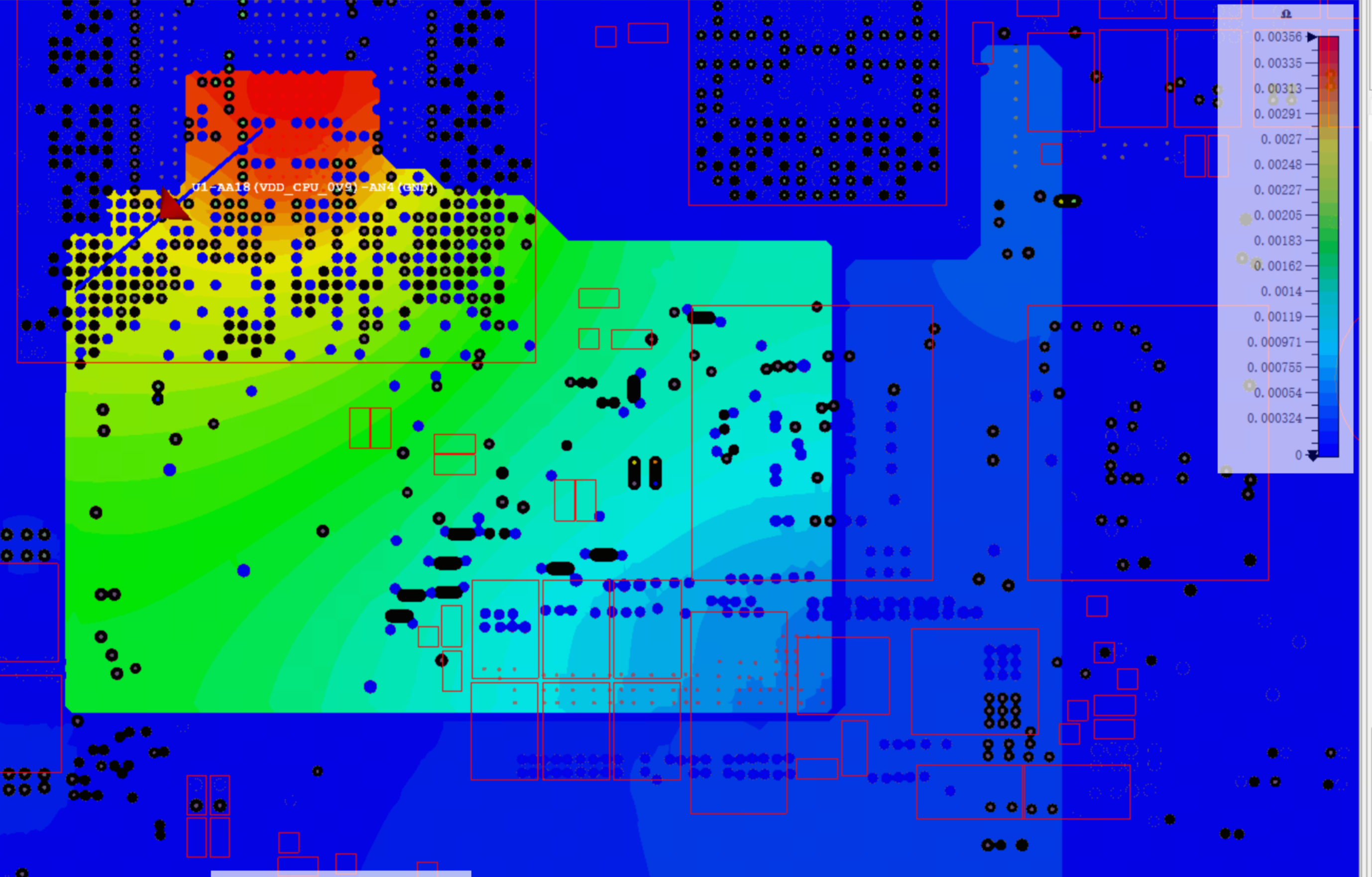

导入到仿真软件中的效果:

下面将由小编我为诸位道友们分步详细解释,一一道来。

一,ESR是如何变化的?

ESR代表等效串联电阻。在PCB的电源层,它主要由铜箔的直流电阻构成。

变化原理:

-

截面积减小: 电流在铜箔中流动,其路径的直流电阻公式为:

R = ρ * L / A其中:-

ρ是铜的电阻率 -

L是电流路径的长度 -

A是电流路径的横截面积(对于PCB平面,通常是铜厚乘以走线宽度)

-

-

当过孔(尤其是接地或其它信号网络的过孔)密集地打在电源路径上时,它们会"侵占"掉原本用于传导电流的铜箔面积。这相当于极大地减小了有效横截面积

A。 -

路径变长与变窄: 电流像水流一样,会绕过这些"障碍物"(过孔)。这迫使电流寻找曲折的路径前进,从而增加了有效路径长度

L。同时,在过孔之间的狭窄通道处,电流密度会急剧增大,这进一步加剧了该局部区域的电阻。

结果: 由于 A 的急剧减小和 L 的增加,根据公式,该路径的总体直流电阻会显著上升。这个增加的直流电阻,就是ESR增大的主要部分。

小编我举一个列子:

一条宽阔的马路(完整的电源平面)上车流(电流)可以顺畅通行。现在马路上被打上了无数个桩子(过孔),车流只能在这些桩子之间狭窄的缝隙中蜿蜒穿行,导致通行效率大大降低,拥堵和阻力(ESR)显著增加。

二,对PDN表现的影响

PDN的目标是在所有频率和时间内,为负载器件提供稳定、干净的电压。被破坏的电源路径主要通过以下几个方面影响PDN性能:

直流压降增大

-

原理: 根据欧姆定律

V_drop = I * R。由于路径电阻R增大,当负载芯片吸取较大电流I时,在电源路径上产生的电压降V_drop会变大。 -

影响: 到达芯片电源引脚的实际电压

V_chip = V_source - V_drop会降低。如果这个压降过大,可能导致芯片供电电压低于其正常工作所需的最低电压,造成系统不稳定甚至复位。在大电流应用中(如CPU、FPGA、GPU),这个问题尤为突出。

交流阻抗恶化

-

原理: PDN的交流阻抗是衡量其性能的关键指标,理想情况下应在目标频段内保持低于一定的目标阻抗。被破坏的电源路径增加了PDN网络中的电阻成分。

-

影响:

-

低频段阻抗升高: 在kHz到数MHz的频率范围内,PDN阻抗主要由电源路径的ESR决定。ESR的增加会直接导致该频段的阻抗峰值升高。

-

瞬态响应变差: 当芯片工作电流发生剧烈跳变时,PDN需要快速响应来补充电荷。更高的阻抗意味着在电流突变期间会产生更大的电压噪声(

ΔV = Z * ΔI)。这表现为电源轨道上的纹波和噪声增大,可能引起信号完整性问题和逻辑错误。

-

去耦电容的有效性降低

-

原理: 去耦电容和电源路径共同构成一个充放电回路。如果通往某个去耦电容的路径电阻很大,那么当芯片需要瞬时电流时,电荷无法快速通过这个高阻路径到达芯片。

-

影响: 这个去耦电容就相当于"被孤立"了,其高频性能无法发挥出来。整个去耦网络的效率大打折扣,无法有效抑制高频噪声。

可能引入额外的寄生电感

-

原理: 电流在绕过密集过孔时形成的长而窄的路径,本身会带来更多的寄生电感。

-

影响: 寄生电感会与去耦电容形成谐振,可能在某个频率点产生很高的阻抗峰值,这进一步恶化了高频段的PDN性能。同时,电感会抵抗电流的快速变化,加剧瞬态电压噪声。

总结与设计建议

|----------|-------|--------|---------------|

| 特性 | 路径完整时 | 路径被打碎时 | 对PDN的影响 |

| ESR/直流电阻 | 低 | 显著增高 | 直流压降增大,低频阻抗升高 |

| 电流路径 | 短而宽 | 长而窄,曲折 | 效率低,局部发热风险 |

| 去耦效率 | 高 | 降低 | 无法有效抑制中高频噪声 |

| 寄生电感 | 小 | 可能增加 | 可能引发谐振,恶化高频性能 |

小编我这边给诸位同行们PCB_LAYOUT工程师的建议:

-

规划是关键: 在布局初期,就要规划好大电流电源的路径,尽可能让其宽阔、顺畅,远离过孔密集区。

-

使用电源平面: 对于关键电源,尽量为其分配一个完整的、未被分割的电源层。这是提供低阻抗路径的最佳方式。

-

过孔管理:

-

在布线规则中设置禁止布线区,保护关键的电源路径。

-

对非关键信号的过孔进行"整齐排布",避免随机散落,将它们引导到对电源平面影响较小的区域。

-

在密度很高的板子上,可以考虑使用背钻或盲埋孔技术来减少通孔对内部平面的破坏。

-

-

仿真验证: 对于高速、大电流设计,必须使用SI/PI仿真工具(如Sigrity, HyperLynx,CST等)对PDN阻抗和直流压降进行分析,提前发现并修复此类问题。

总之,电源路径被过孔打碎是一个严重的PCB设计问题,它会从直流和交流两个方面全面恶化PDN性能,必须在设计阶段予以高度重视和避免,最好是利用仿真软件做一下评估。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!