pll电荷泵锁相环 (已流片) 内部含有仿真环境 流片验证 有版图 电路架构为三阶二型锁相环,含有环形振荡器 ring vco 模块,鉴频鉴相器PFD模块,分频器DIV模块 ,ps 计数器和电荷泵CP模块 [闪亮][闪亮]指标如下: 参考频率50-100MHz 分频比可调 锁定频率600M-2GHz 锁定时间4us

最近完成了一个超有意思的项目------PLL 电荷泵锁相环,并且已经成功流片啦,迫不及待来和大家分享分享。

一、电路架构探秘

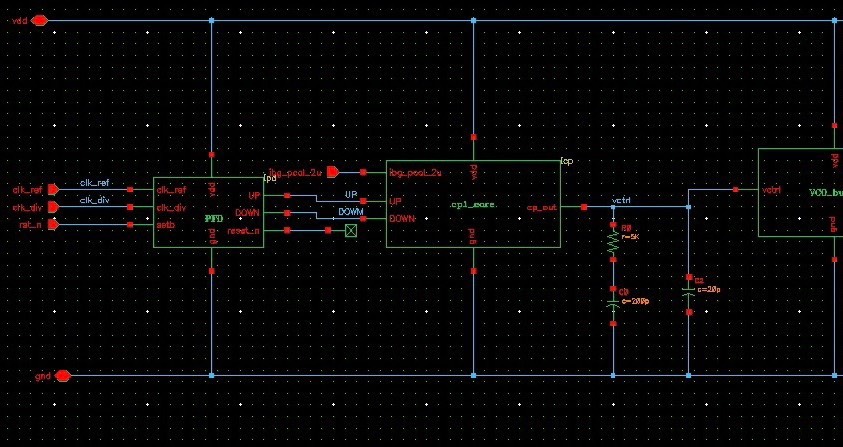

咱这个锁相环采用的是经典的三阶二型锁相环架构,里面集成了好几个关键模块。

1. 环形振荡器 ring vco 模块

环形振荡器(ring vco)那可是产生高频信号的得力干将。简单来说,它通过一系列反相器首尾相连构成环形结构,信号在这个环里循环振荡,从而输出高频时钟信号。代码示例(以 Verilog 为例):

verilog

module ring_vco #(

parameter STAGES = 5

) (

input wire clk,

input wire rst,

output reg [STAGES - 1:0] osc_out

);

always @(posedge clk or posedge rst) begin

if (rst) begin

osc_out <= {STAGES{1'b0}};

end else begin

osc_out <= {osc_out[STAGES - 2:0], ~osc_out[STAGES - 1]};

end

end

endmodule这里通过一个简单的环形结构,在时钟和复位信号的控制下,实现了信号的振荡输出。STAGES 参数可以控制环形振荡器的级数,级数不同,振荡频率也会有所不同。

2. 鉴频鉴相器 PFD 模块

鉴频鉴相器(PFD)的作用是比较输入信号和反馈信号的频率与相位,然后输出相应的控制信号。当两个信号的频率和相位不一致时,PFD 就会给出信号去调整,让它们慢慢趋于一致。Verilog 代码如下:

verilog

module pfd (

input wire clk_ref,

input wire clk_feedback,

output reg up,

output reg down

);

always @(posedge clk_ref or posedge clk_feedback) begin

if (clk_ref &&!clk_feedback) begin

up <= 1'b1;

down <= 1'b0;

end else if (clk_feedback &&!clk_ref) begin

up <= 1'b0;

down <= 1'b1;

end else begin

up <= 1'b0;

down <= 1'b0;

end

end

endmodule在这个代码里,通过比较 clkref**和 clk feedback 的上升沿,来判断两者的相位关系,进而输出 up 和 down 信号,用于后续对电荷泵的控制。

3. 分频器 DIV 模块

分频器(DIV)能把高频信号按照一定比例分频,得到我们想要的低频信号。比如说我们输入一个高频时钟信号,通过设置合适的分频比,就能得到频率较低的信号,方便和参考信号进行比较。代码如下:

verilog

module div #(

parameter DIVISOR = 10

) (

input wire clk_in,

input wire rst,

output reg clk_out

);

reg [31:0] counter;

always @(posedge clk_in or posedge rst) begin

if (rst) begin

counter <= 32'd0;

clk_out <= 1'b0;

end else begin

if (counter == (DIVISOR - 1)) begin

counter <= 32'd0;

clk_out <= ~clk_out;

end else begin

counter <= counter + 1;

end

end

end

endmodule这里通过一个计数器 counter 来对输入时钟 clkin**进行计数,当计数值达到 DIVISOR - 1 时,就翻转输出时钟 clk out 的电平,实现分频功能。DIVISOR 参数决定了分频比。

4. ps 计数器和电荷泵 CP 模块

ps 计数器可以精确测量相位差,电荷泵(CP)则根据 PFD 输出的信号,通过充电或放电来调整电压,进而控制 VCO 的频率。

verilog

module cp (

input wire up,

input wire down,

output reg [15:0] charge

);

always @(posedge up or posedge down) begin

if (up) begin

charge <= charge + 1;

end else if (down) begin

charge <= charge - 1;

end

end

endmodule在这个电荷泵代码里,up 信号使 charge 增加,down 信号使 charge 减少,通过这种方式来调整控制电压。

二、仿真与验证

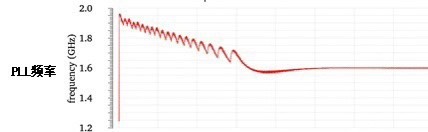

这个 PLL 电荷泵锁相环内部还集成了仿真环境,这可太重要啦。在实际流片之前,通过仿真可以验证各个模块的功能是否正常,以及整个锁相环的性能指标能不能达到预期。比如说,我们可以通过仿真来观察参考频率在 50 - 100MHz 变化时,锁相环的锁定情况;还能看看分频比调整时,输出频率是否符合预期。通过不断调整参数、优化代码,让整个锁相环在仿真环境中达到最佳状态,这样流片成功的几率就大大增加啦。

三、流片验证与版图设计

经过了漫长的仿真优化,终于迎来了流片验证的时刻。流片就像是把我们精心设计的电路"印"到芯片上,实际检验它的性能。当然,在流片之前,版图设计是必不可少的一步。版图设计要考虑到各个模块之间的布局、布线,要尽量减小信号干扰,提高电路的稳定性。我们根据电路架构,精心绘制了版图,让各个模块合理分布,确保最终流片出来的芯片能正常工作。

四、亮眼的指标

最后来看看咱这个锁相环的指标,简直不要太厉害。参考频率能在 50 - 100MHz 灵活变动,分频比也是可调的。锁定频率范围更是宽广,从 600M - 2GHz 都能轻松驾驭,而且锁定时间超级快,只需要 4us 。这些指标在实际应用中可是非常有竞争力的,无论是在通信领域还是其他对时钟精度要求较高的场景,都能发挥重要作用。

总之,这次 PLL 电荷泵锁相环的项目经历,让我对锁相环的设计、仿真、流片等环节有了更深入的理解,希望我的分享也能给大家带来一些启发。