本博文主要交流设计思路,在本博客已给出相关博文约150篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。若有NVME或RDMA 产品及项目需求,请看B站视频后联系。

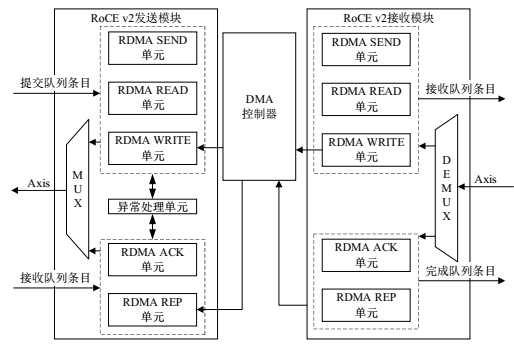

RoCE v2 发送及接收模块负责将用户指令组装为 RoCE v2 数据包或从 RoCE v2数据包中解析出远程主机信息及数据。RoCE v2 发送及接收模块的结构和数据转移方式如图1所示。RoCE v2 发送及接收模块均由五个单元组成,分别为 SEND 单元、READ 单元、WRITE 单元、ACK 单元和 REP 单元。其中 SEND 单元、READ 单元及WRITE 单元负责组装或解析这三种类型的请求包,而 ACK 单元与 REP 单元则负责组装或解析这两种类型的回复包。

图1 RoCE v2 发送及接收模块结构及数据转移图

在 RoCE v2 协议中,SEND 指令为双边语义,发送及接收均需要远程主机 CPU 参与,数据交换速率相对较慢、延迟相对较高。因此在RoCE v2 发送及接收模块中,SEND 单元只用于进行主机间的信息参数交换,不直接涉及大批量的数据传输操作,可以在一定程度上降低传输延迟、增加数据吞吐量。而DMA 控制器在其中负责数据交换,即把 AXI4 总线接口的数据和 AXI-Stream 总线接口的数据进行相互转换,分别与直接涉及到数据操作的 WRITE 单元和 REP 单元相连接。接下来将分别对 RoCE v2 发送和接收模块的结构设计和工作流程进行具体分析。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望