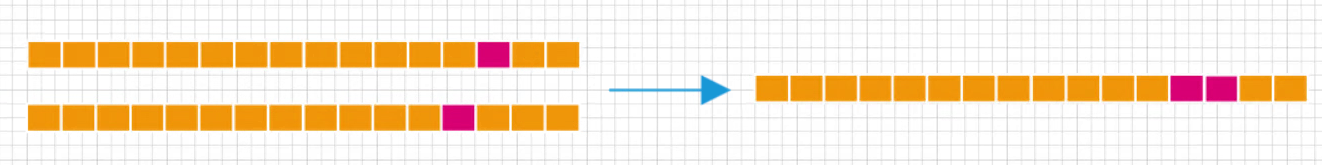

要完成16byte中byte的合并:

首先verilog 不支持可变范围的bit选择,所以下面两种写法,lint 都会报错:

// write style 1

always (*)begin

map_wdata ='b0;

map_wdata[127:lower_byte_addr*8]= wdata[127:lower_byte_addr*8];

map_wdata[(lower_byte_addr-1)*8+:8]= wone_size ? wone_data_store:wdata[(lower_byte_addr-1)*8+:8];

map_wdata[(lower_byte_addr-1)*8-1:0]= wdata[(lower_byte_addr-1)*8-1:0];

end

// write style 2

assign map_wdata = wone_size ? {wdata[127:lower_byte_addr*8],wone_data_store,wdata[(lower_byte_addr-1)*8-1:0]}:wdata;正确的写法是下面的,将可变范围变成按byte进行选择:

// write style 3

always @(*)begin

if(wone_size)

for(i=0; i<STRB_WIDTH;i=i+1)begin

if(i==lower_byte_addr)

map_wdata[i*8+:8]= wdata[i*8+:8];

else

map_wdata[i*8+:8]= wone_data_store;

end

else begin

map_wdata = wdata;

end

end