一、介绍

ARMv7 架构下核心寄存器分为通用寄存器、程序状态寄存器、专用寄存器三类,不同模式下部分寄存器有备份(banked),作用如下:

- 通用寄存器 (R0-R15)

-

R0-R7:未备份通用寄存器,所有处理器模式共享,用于临时数据存储、函数参数传递与返回值传递。

-

R8-R12:部分备份寄存器,FIQ 模式有独立备份(R8_fiq-R12_fiq),避免 FIQ 中断处理破坏原有数据。

-

R13 (SP):栈指针寄存器,各模式有独立备份,存放当前模式下栈顶地址。

-

R14 (LR):链接寄存器,各模式有独立备份,保存函数调用的返回地址或异常处理的返回地址。

-

R15 (PC):程序计数器,存储下一条要执行的指令地址,ARM 状态下指向当前指令 + 8 字节。

- 程序状态寄存器 (CPSR/SPSR)

-

CPSR:当前程序状态寄存器,记录 ALU 运算标志(N/Z/C/V)、中断屏蔽位(I/F)、处理器模式位(M[4:0])等,所有模式共享。

-

SPSR:备份程序状态寄存器,仅异常模式拥有,用于保存进入异常前的 CPSR 值,异常返回时恢复 CPSR。

- 专用寄存器

- 包括 CP15 协处理器寄存器(用于存储系统控制、内存管理、缓存配置等信息)、TPIDRPRW(线程 ID 寄存器)等,负责架构的底层控制与扩展功能。

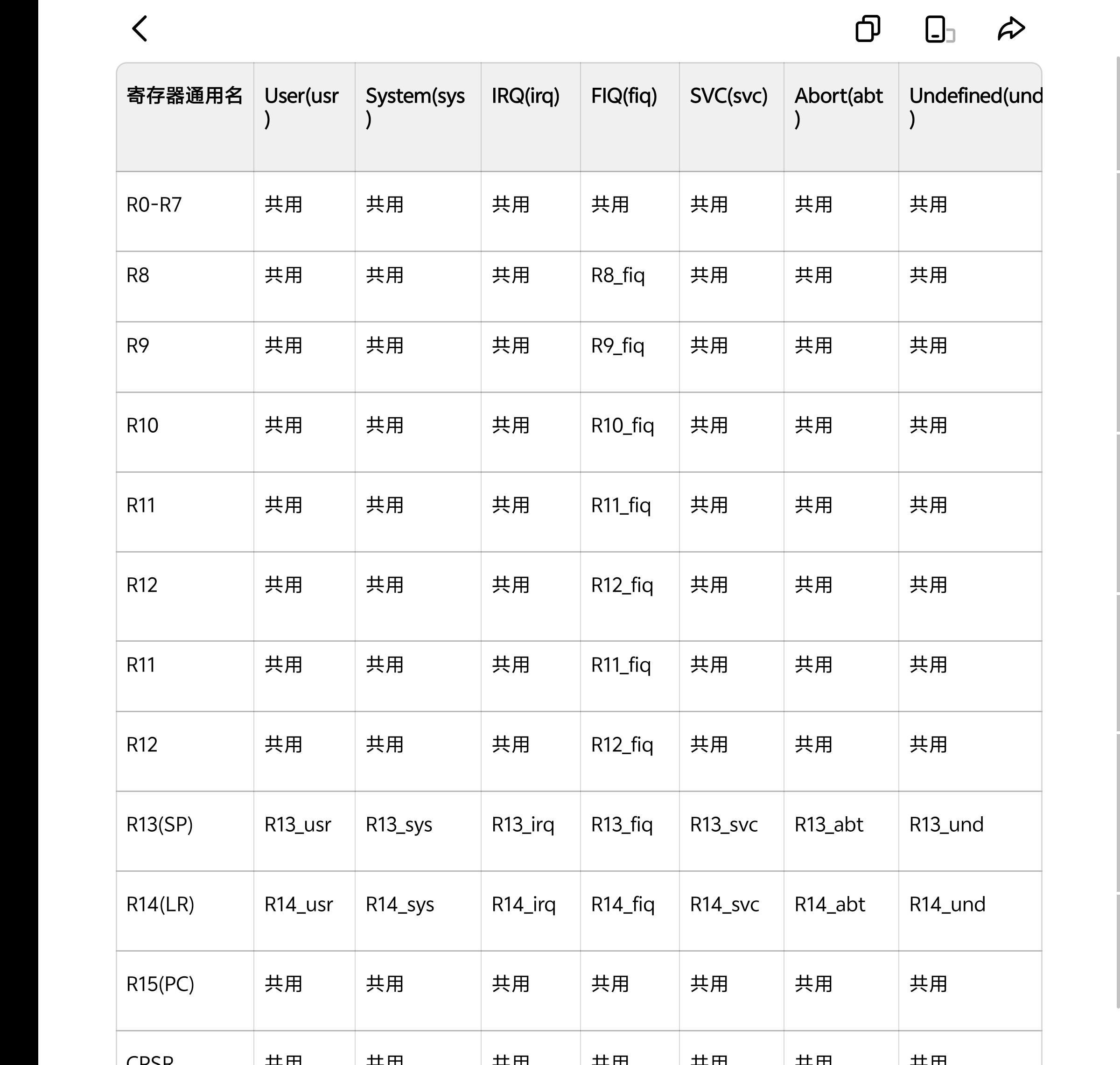

二、不同模式下的寄存器

ARMv7 支User/System/IRQ/FIQ/SVC/Abort/Undefined 7 种模式,其中 User/System 为非异常模式,其余为异常模式,不同模式下寄存器的 banked(备份)情况不同,映射如下:

说明:

- System 模式与 User 模式寄存器完全相同,无 SPSR,用于运行特权级系统任务。

- FIQ 模式对 R8-R12 额外备份,目的是减少中断处理时的寄存器入栈开销,提升响应速度。

- 所有异常模式均有独立的 R13/R14 和 SPSR,避免异常处理破坏原模式的运行上下文