目录

-

- 一、概述

- 二、协议解析

-

- [2.1 全局寄存器](#2.1 全局寄存器)

-

- [1. DMAC_CFG(DMAC Configuration Register)](#1. DMAC_CFG(DMAC Configuration Register))

- [2. DMAC_CHEN(Channel Enable Register)](#2. DMAC_CHEN(Channel Enable Register))

- [3. DMAC_ID / DMAC_VERSION](#3. DMAC_ID / DMAC_VERSION)

- [2.2 通道寄存器](#2.2 通道寄存器)

-

- [1. CH_SAR(Source Address Register)](#1. CH_SAR(Source Address Register))

- [2. CH_DAR(Destination Address Register)](#2. CH_DAR(Destination Address Register))

- [3. CH_BLOCK_TS(Block Transfer Size)](#3. CH_BLOCK_TS(Block Transfer Size))

- [4. CH_CTL(Channel Control Register)](#4. CH_CTL(Channel Control Register))

- [5. CH_CFG(Channel Configuration Register)](#5. CH_CFG(Channel Configuration Register))

- [6. CH_LLP(Linked List Pointer)](#6. CH_LLP(Linked List Pointer))

- [2.3 中断相关寄存器](#2.3 中断相关寄存器)

-

- [1. DMAC_INTSTATUS](#1. DMAC_INTSTATUS)

- [2. DMAC_COMMON_INTCLEAR](#2. DMAC_COMMON_INTCLEAR)

- [3. Channel 中断状态](#3. Channel 中断状态)

- 三、配置流程

- 四、其他相关链接

-

- [[1. Synopsys APB I2C协议总结](https://blog.csdn.net/Luckiers/article/details/155387876?spm=1011.2124.3001.6209)](#1. Synopsys APB I2C协议总结)

- [[2. SPI协议详细总结附实例图文讲解通信过程](https://blog.csdn.net/Luckiers/article/details/131297469)](#2. SPI协议详细总结附实例图文讲解通信过程)

- [[3. Synopsys APB UART协议总结](https://blog.csdn.net/Luckiers/article/details/155986836)](#3. Synopsys APB UART协议总结)

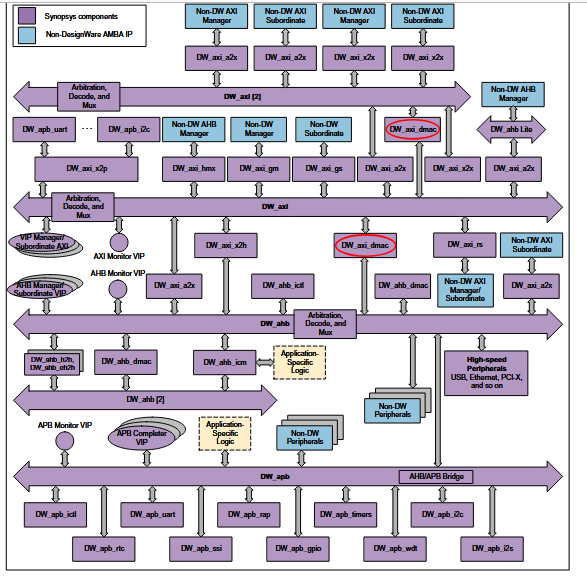

一、概述

本文主要讲解Synopsys AXI DMAC Databook中常见寄存器的功能,讲述DMAC配置流程。

二、协议解析

2.1 全局寄存器

1. DMAC_CFG(DMAC Configuration Register)

DMA 控制器全局使能

| bit | 名称 | 说明 |

|---|---|---|

| 0 | DMAC_EN | 1 = 使能 DMAC |

| others | - | 保留 |

Note:

所有 channel 配置完成后再置 DMAC_EN=1

Disable DMAC 会强制停止所有通道

2. DMAC_CHEN(Channel Enable Register)

| bit | 名称 | 说明 |

|---|---|---|

| [7:0] | CH_EN | 对应 channel 使能 |

| [15:8] | CH_EN_WE | 写 1 才允许修改对应 CH_EN |

| 典型写法: |

c

DMAC_CHEN = (1 << ch) | (1 << (ch + 8));3. DMAC_ID / DMAC_VERSION

| 寄存器 | 说明 |

|---|---|

| DMAC_ID | 固定 IP ID |

| DMAC_VERSION | IP 版本号(区分 v3/v4/v5) |

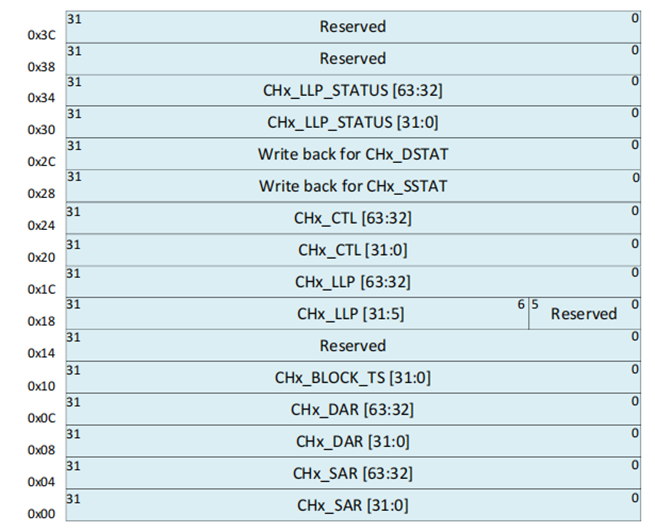

2.2 通道寄存器

以下寄存器 每个 Channel 都有一组,基地址一般是:

bash

CHn_BASE = DMAC_BASE + 0x100 * n1. CH_SAR(Source Address Register)

解析:DMA传输源地址

特性:

物理地址

支持 32 / 64 bit(取决于配置)

2. CH_DAR(Destination Address Register)

解析:DMA传输目的地址

物理地址

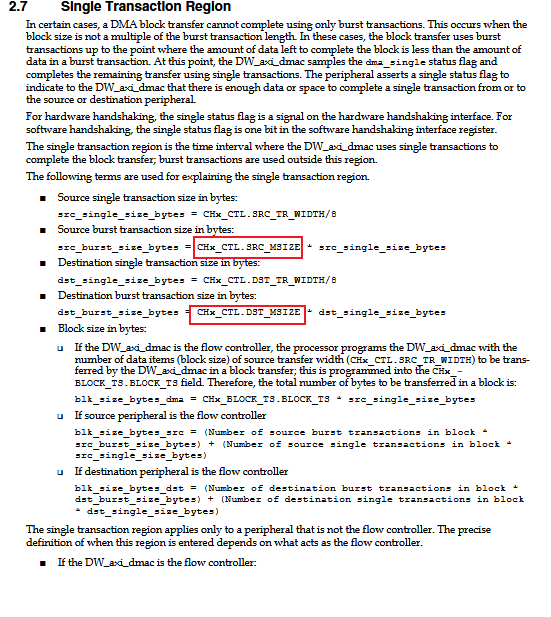

3. CH_BLOCK_TS(Block Transfer Size)

BLOCK_TS 一次 block 传输的传输次数

📌 真实传输字节数

bash

bytes = BLOCK_TS × SRC/DST Transfer WidthNote:

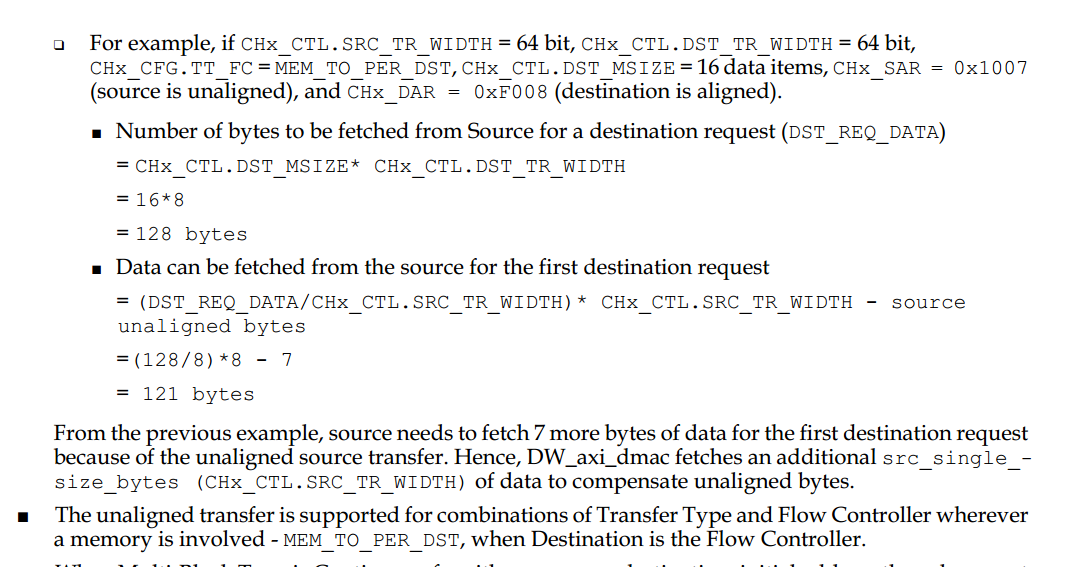

如果有burst传输,则需要再乘以MSIZE(在CH_CTL对应bit设置),具体计算如下公式。

具体示例:

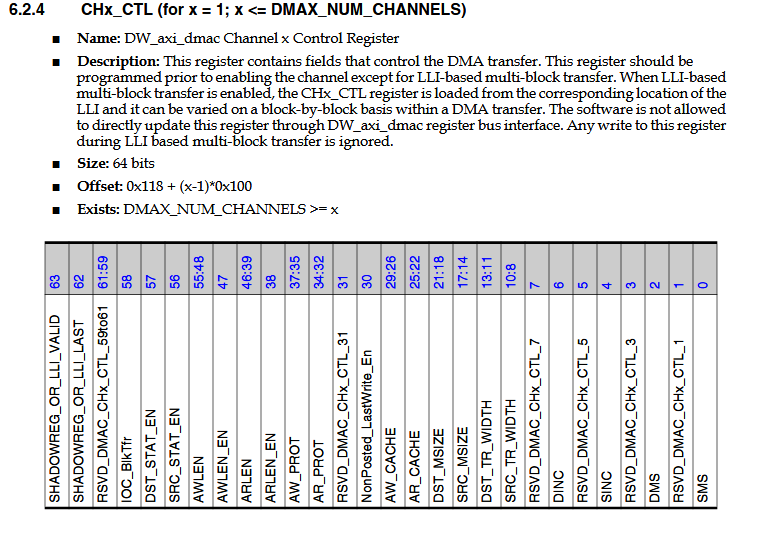

4. CH_CTL(Channel Control Register)

最关键寄存器之一

常见字段:

| bit | 名称 |

|---|---|

| SRC_TR_WIDTH | 源传输宽度(8/16/32/64bit) |

| DST_TR_WIDTH | 目的传输宽度 |

| SRC_INC | 源地址是否递增 |

| DST_INC | 目的地址是否递增 |

| SRC_MSIZE | Source burst 长度 |

| DST_MSIZE | Dest burst 长度 |

| IOC_BLKTFR | Block 完成产生中断 |

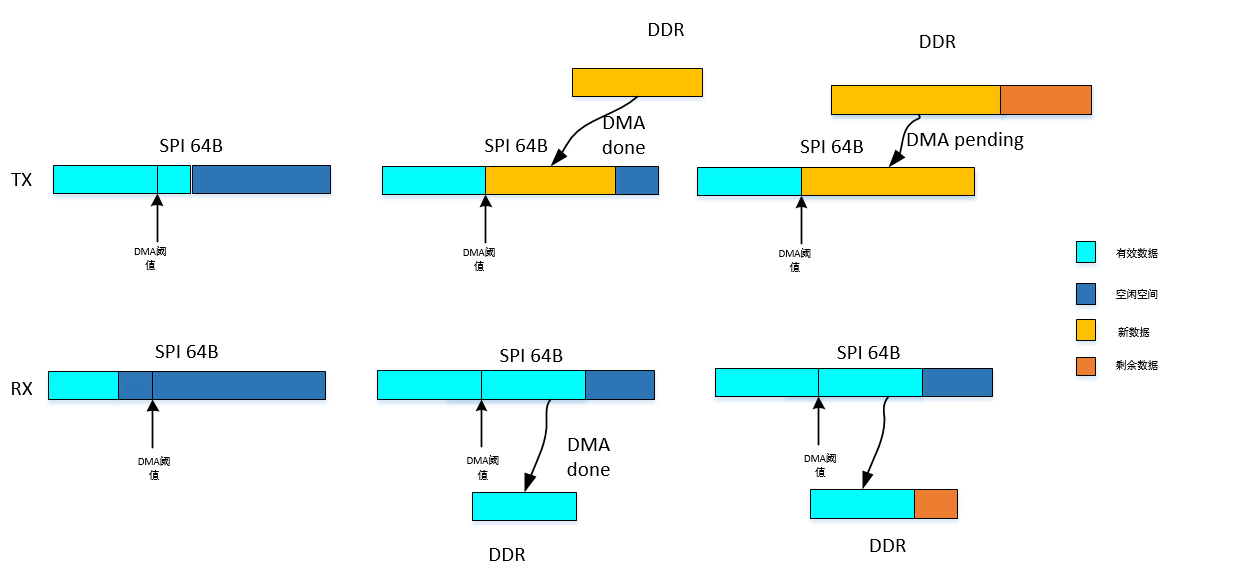

注意设置MSIZ的意义在于:DMA在一次总线控制权获取之后,连续传输多个数据单元,而不是每传输一个数据就重新请求一次总线。

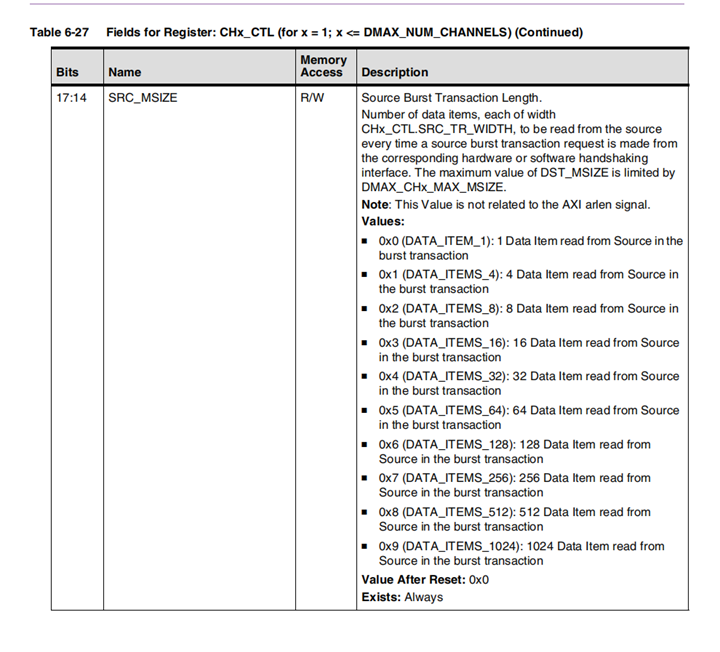

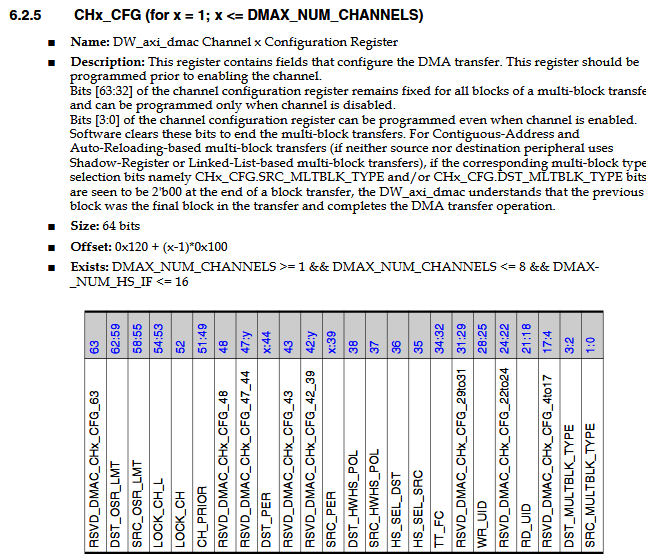

5. CH_CFG(Channel Configuration Register)

| 字段 | 说明 |

|---|---|

| HS_SEL_SRC | 源 handshake:HW / SW |

| HS_SEL_DST | 目的 handshake |

| SRC_PER | 源外设号 |

| DST_PER | 目的外设号 |

| TT_FC | Transfer Type & Flow Control |

TT_FC(重点)决定传输的方向

| 值 | 含义 |

|---|---|

| 0x0 | M2M (DMA 控制) |

| 0x1 | M2P |

| 0x2 | P2M |

| 0x3 | P2P |

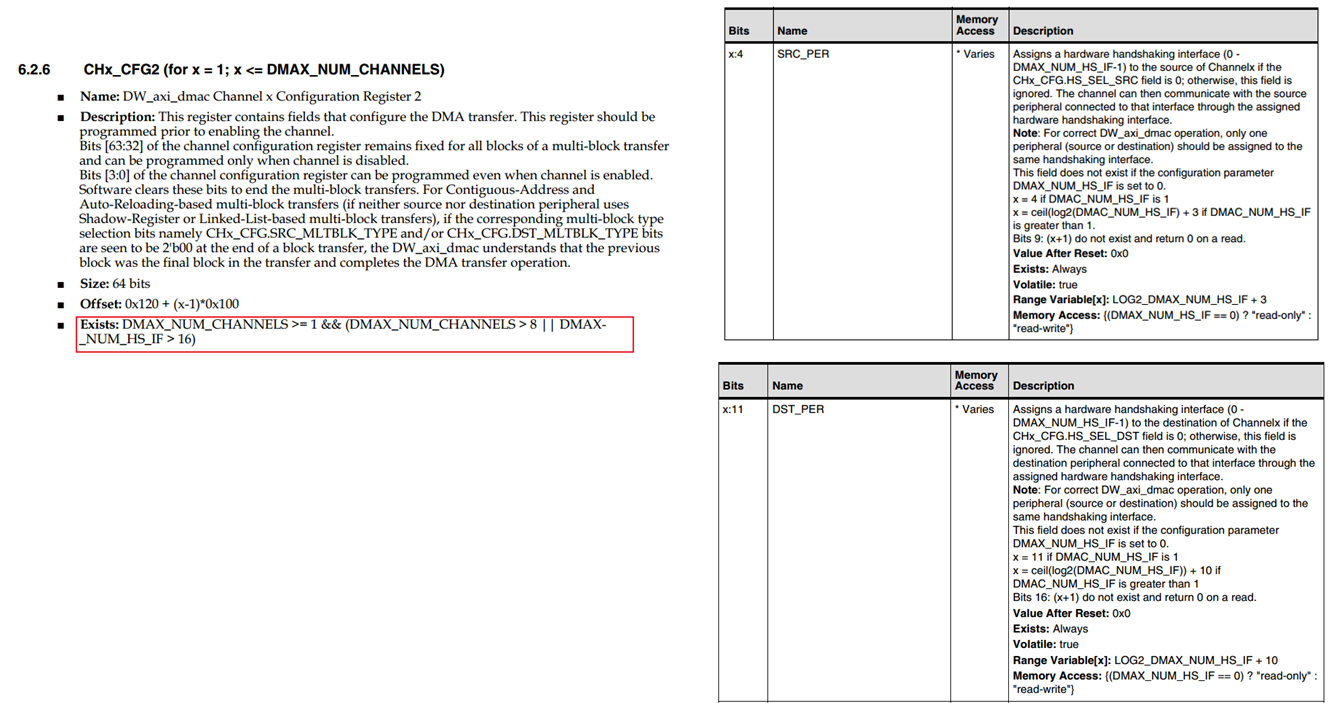

Note:CH_CFG是针对小于等于8个channel的控制器,大于8小于16的控制器要使用CH_CFG2

6. CH_LLP(Linked List Pointer)

链表模式:

指向下一个 LLI 描述符,非LLP模式,每次DMA都需要重新配置DMAC_CFG,采用LLP模式,相当于将配置统一存放在申请的内存中,由硬件按偏移一次读取配置进行DMA操作。

支持 scatter-gather

📌 如果不用链表:

CH_LLP = 0

LLI具体解析

LLI 是用于组织多个 DMA 传输描述符的数据结构,使 DMA 控制器可以自动连续处理多个传输任务,而无需 CPU 干预。

普通的 DMA 传输一次只能处理一段数据(源地址、目的地址、传输长度),当要传多个段时,就需要 CPU 多次配置 DMA。为减少 CPU 负担,引入 LLI 机制,允许将多个传输任务以链表的形式预设好,DMA 控制器可自动跳转执行下一个任务

2.3 中断相关寄存器

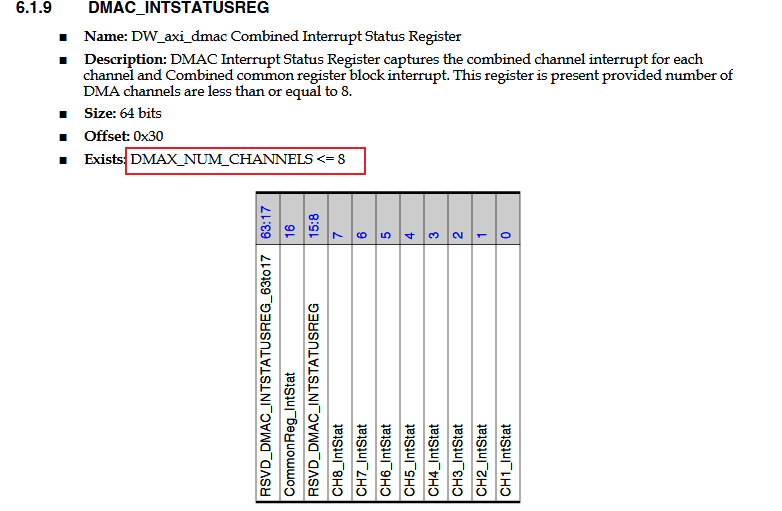

1. DMAC_INTSTATUS

中断总状态,此寄存器是在DMA channnel小于等于8时使用,大于8时读DMAC_INTSTATUSREG2。

当总的对应中断触发后,可查看对应的channel中断,确定中断触发类型。

2. DMAC_COMMON_INTCLEAR

清除中断

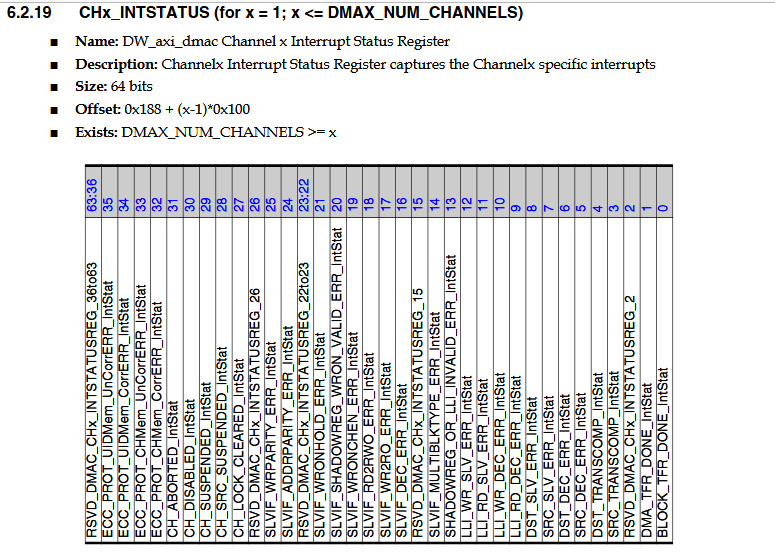

3. Channel 中断状态

| 寄存器 | 说明 |

|---|---|

| CH_INTSTATUS | 单 channel 中断状态 |

| CH_INTCLEAR | 清除 channel 中断 |

| CH_INTMASK | 中断屏蔽 |

三、配置流程

DMAC_CFG.DMAC_EN = 0 配置 CH_SAR / CH_DAR 配置 CH_CTL 配置 CH_CFG CH_LLP = 0非链表 使能中断--可选 DMAC_CHEN 使能 channel DMAC_CFG.DMAC_EN = 1