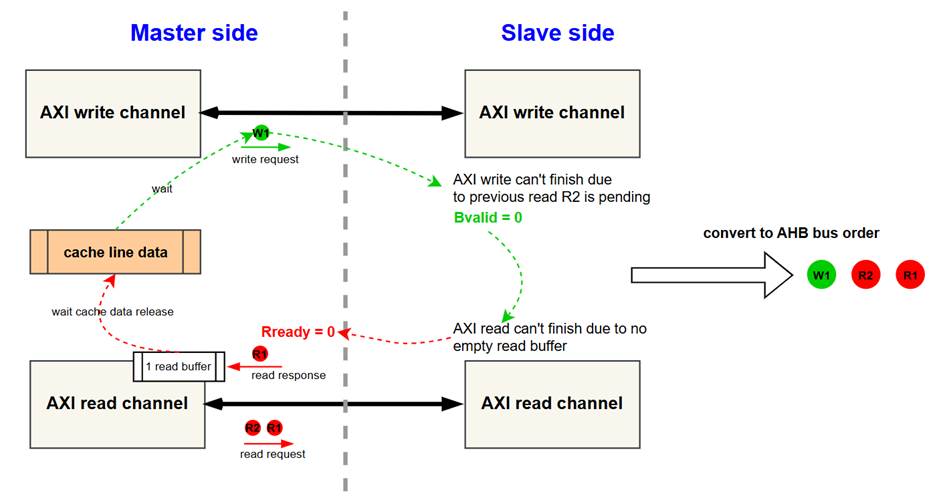

分享个AXI死锁场景,如下图所示,假如Master是CPU,Slave是AXI转AHB的桥。

Master往下游发起两笔读操作,每一笔都是读完整的cache line数据,但内部只有一个read buffer来存储返回的数据,大小为1个cache line。因此Master必须先缓存R1的数据,然后再缓存R2的数据,所以Master暂时不接收R2的数据了。

Master往下游发起两笔读操作,每一笔都是读完整的cache line数据,但内部只有一个read buffer来存储返回的数据,大小为1个cache line。因此Master必须先缓存R1的数据,然后再缓存R2的数据,所以Master暂时不接收R2的数据了。

Master 在收到R1的数据并放到read buffer后,会先拉低Rready信号,等到read buffer的数据放到cache中对应的set/way位置后,再拉高Rready信号,表示read buffer可以继续接收数据。但由于要放入的set/way是dirty数据,所以Master需要先把set/way原先的数据写回下游,所以master发起了W1写操作。

W1写请求被slave收到后,发现前面R2的操作还没有完成,因为R2的数据还没有被Master收下,这样W1也就无法完成了。

这样一个死锁环就形成了。Read buffer中的R1需要CPU cache腾出某set/way的空间->CPU cache在腾该set/way的写操作无法被slave接收->slave之所以不接收,是因为slave发现R2还没有做完->R2之所以没有做完,是因为CPU master无法接收R2的数据了->CPU master之所以无法接收新数据,是因为read buffer被R1占据了。

那么这种死锁环可以怎么验证出来呢?

常见的方式是在Slave测挂的AXI slave VIP去测Master CPU时,要在AXI slave VIP内实现读请求永远优先于写请求的机制模式。