晶振输入47脚为27MHZ

只需安装教育版云源软件一个软件,正常情况不用安装编程器软件

云源软件很轻量,编译的很快

按键led测试

led_prj.cst

bash

IO_LOC "o_led[2]" 11;

IO_PORT "o_led[2]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_led[1]" 10;

IO_PORT "o_led[1]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "o_led[0]" 9;

IO_PORT "o_led[0]" IO_TYPE=LVCMOS33 PULL_MODE=UP DRIVE=8;

IO_LOC "i_rst_n" 13;

IO_PORT "i_rst_n" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "i_clk" 47;

IO_PORT "i_clk" IO_TYPE=LVCMOS33 PULL_MODE=UP;

IO_LOC "i_key_B" 44;

IO_PORT "i_key_B" IO_TYPE=LVCMOS33 PULL_MODE=UP;led.v

verilog

module led

#(

parameter P_CLK_FREQ_MHZ = 27, // 时钟频率,单位MHz,默认27MHz

parameter P_DEBOUNCE_MS = 20, // 消抖时间,单位ms,默认20ms

parameter L_CNT_WIDTH = 32 // 需要外部计算后传入

)

(

input wire i_clk , //系统时钟50Mhz

input wire i_rst_n , //全局复位

input wire i_key_B , //按键B输入信号

output reg [2:0] o_led // 110 R, 101 B, 011 G

);

// 根据时钟频率和消抖时间计算需要计数的最大值

localparam L_MAX_CNT = P_CLK_FREQ_MHZ * 1000 * P_DEBOUNCE_MS;

reg [L_CNT_WIDTH-1:0] r_cnt ;

// ==================================================

// r_cnt :记录按键按键的时间

// ==================================================

always@(posedge i_clk or negedge i_rst_n)

if(i_rst_n == 1'b0)

r_cnt <= {(L_CNT_WIDTH+1){1'b0}};

//按键松开,计数器清零

else if(i_key_B == 1)

r_cnt <= {(L_CNT_WIDTH+1){1'b0}};

//按键按下时,计数器计数

else if(i_key_B == 1'b0 && r_cnt < L_MAX_CNT-1)

r_cnt <= r_cnt + 1'b1;

else

//如果按键一直不释放,则r_cnt维持最大值,防止多次触发

r_cnt <= r_cnt;

// ==================================================

// o_led :输出灯信号

// ==================================================

always@(posedge i_clk or negedge i_rst_n)

if(i_rst_n == 1'b0)

o_led <= 3'b000;

//计数快满时,产生一个时钟周期的脉冲,因为按住不松手时,计数器会维持在L_MAX_CNT-1

else if(r_cnt == L_MAX_CNT-3)

o_led <= o_led+1;

else

o_led <= o_led;

endmoduleled_prj.tcl

tcl

set rtl_dir "D:/workspace/gitee/0/ming-verilog_prj/ming-verilog/src/gowin/rtl"

add_file $rtl_dir/led.v

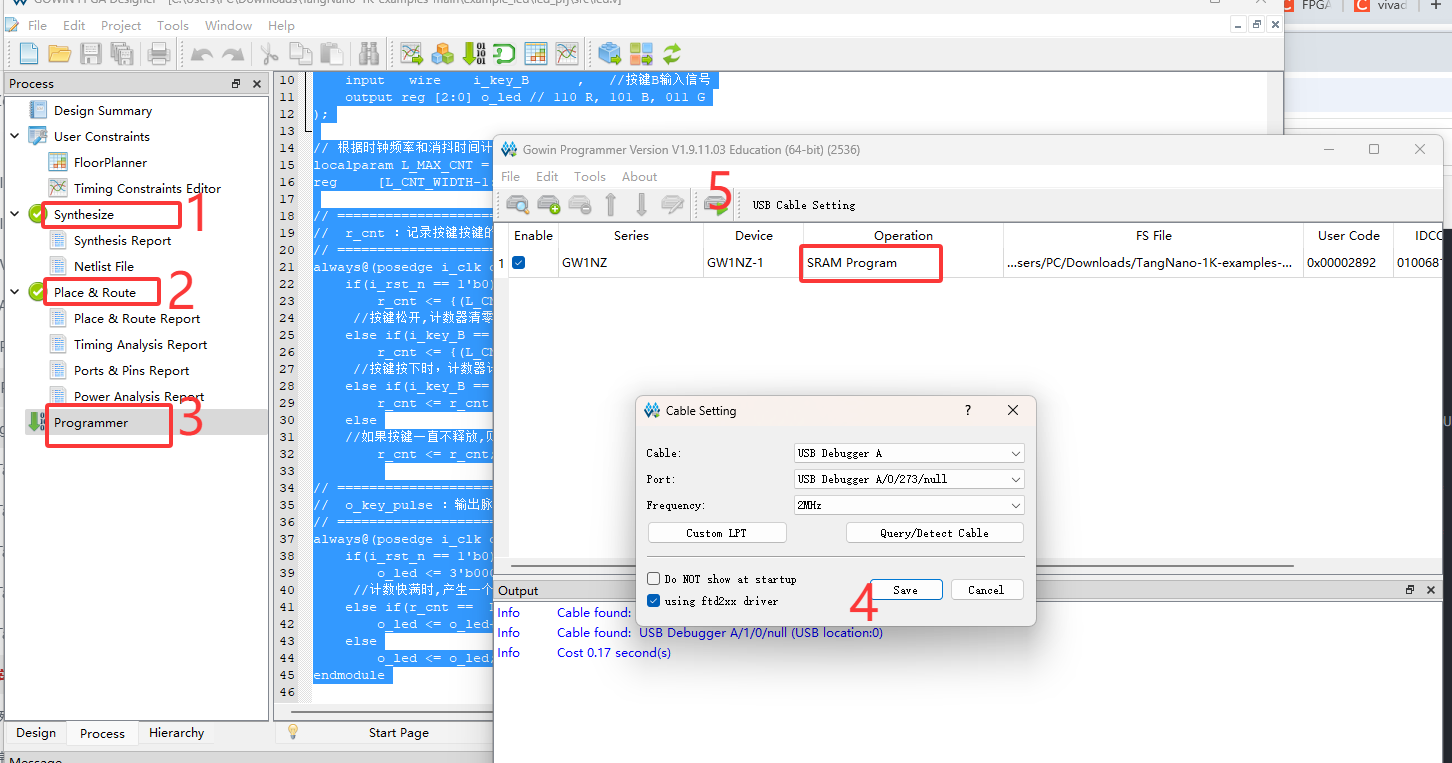

add_file $rtl_dir/led_prj.cst编译下载

依次点击 1,2,3,4,5 下载程序运行