目录

Costas环作为一种经典的载波同步算法,凭借无需恢复基带信号、结构简洁、同步精度高的优势,被广泛应用于PSK、QAM等调制信号的载波恢复场景。本次学习围绕Costas环展开全流程探究,覆盖原理分析、MATLAB仿真验证、FPGA硬件开发与测试等多个维度,形成了从理论到实践的完整知识体系。

1.Costas环基本原理的深度剖析

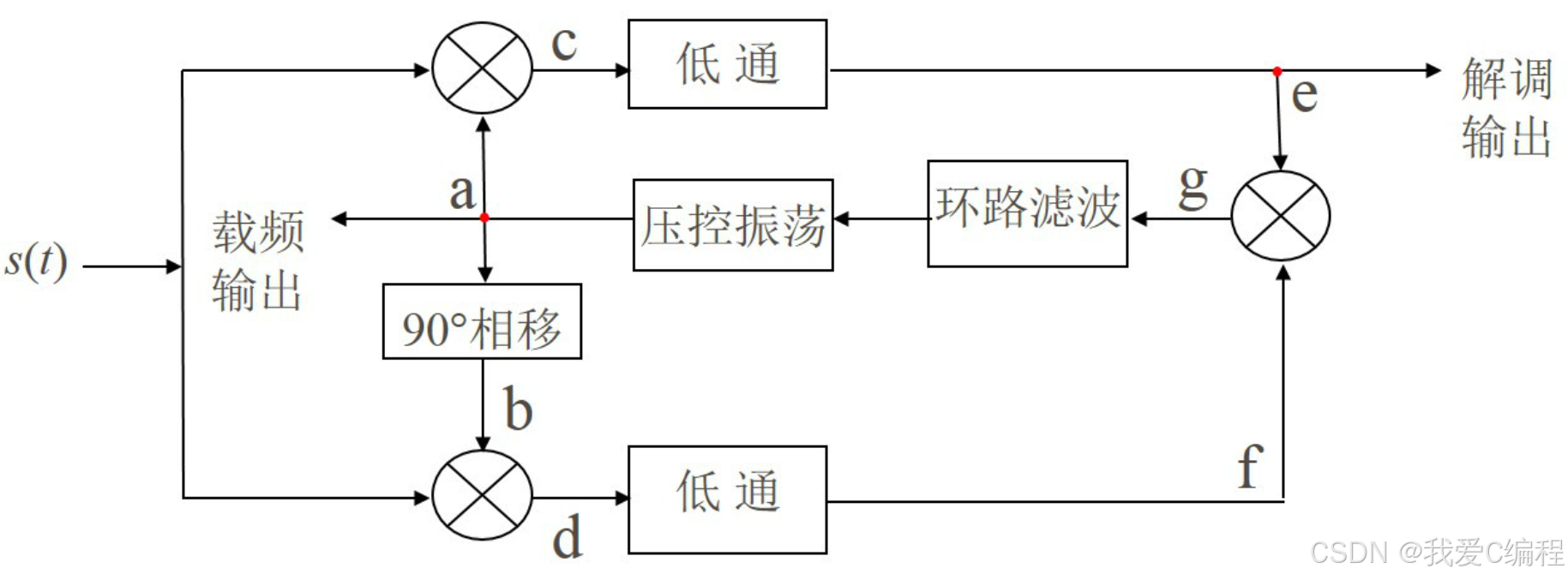

学习的首要环节是深入理解Costas环的核心工作机制。Costas环本质是一种锁相环,其核心特征是利用正交鉴相器替代传统锁相环中的鉴相器与低通滤波器组合,直接对中频调制信号进行处理。其基本结构包含压控振荡器(VCO)、正交乘法器、低通滤波器(LPF)和鉴相器四个关键模块。

中频输入信号与VCO输出的两路正交载波分别相乘,得到I路和Q路信号,经低通滤波后去除高频分量,保留包含载波相位信息的基带分量。鉴相器对I、Q两路基带信号进行鉴相运算,输出与相位差成正比的误差电压,该误差电压通过环路滤波器滤波后反馈至VCO,调整VCO输出载波的相位与频率,最终实现输入信号载波与VCO输出载波的同频同相,完成载波同步。相较于传统的平方环法,Costas环无需对输入信号进行平方运算,有效避免了平方器件带来的非线性失真,同时减少了信号频谱的展宽,在低信噪比场景下具备更优的同步性能。

对应课程内容:

2.基于MATLAB的Costas环仿真与性能分析

理论学习之后,借助MATLAB开展了Costas 环的仿真验证与性能影响因素分析。

首先,搭建了Costas环的基础仿真模型,包含信号产生、正交解调、鉴相运算、环路滤波、VCO 控制。生成BPSK调制信号作为输入,观察I、Q路信号的收敛过程与载波同步结果,验证Costas环的载波恢复能力。为了更直观地呈现仿真过程,博主制作了操作讲解视频,详细演示了程序的运行步骤、参数设置方法与结果分析技巧。

然后,围绕三大性能影响因素展开分析。

第一,分析环路滤波器系数的影响,通过调整比例系数与积分系数,对比不同参数下环路的收敛速度与稳态误差,发现增大比例系数可加快收敛速度,但易导致环路振荡,增大积分系数可降低稳态误差,但会牺牲收敛速度,需根据实际需求进行参数权衡。

第二,探究频偏对系统性能的影响,通过设置不同的输入信号与VCO初始频偏,观察环路的锁定范围与收敛时间,结果表明Costas环的频偏锁定范围存在阈值,超出阈值后环路将无法实现同步。

第三,研究SNR的影响,通过在输入信号中添加不同强度的高斯白噪声,分析信噪比与环路同步概率、稳态相位误差的关系,发现当信噪比低于某一临界值时,环路的鉴相误差会显著增大,甚至出现失锁现象。

对应课程内容:

3.Costas环的性能影响因素分析1------环路滤波器系数对系统性能的影响

4.Costas环的性能影响因素分析2------------频偏对系统性能的影响

5.Costas环的性能影响因素分析3------------信噪比对系统性能的影响

3.基于FPGA的Costas环硬件开发与实现

FPGA开发将系统划分为发射端与解调端两大模块,每个模块再细分为若干子模块,逐一完成 Verilog代码编写与功能验证。

发射端核心是信号产生模块,通过Verilog生成BPSK调制信号,为解调端提供输入信号,并制作了操作讲解视频,演示了信号参数配置与波形输出方法。

解调端是Costas环的核心,包含五大子模块。

第一,下变频模块,将输入的中频信号与VCO输出的正交载波进行乘法运算,实现正交解调,该模块的关键是保证乘法器的运算精度,避免引入非线性失真。

第二,低通滤波器模块,采用FIR滤波器结构,滤除正交解调后的高频分量,保留基带信号。

第三,鉴相器模块,根据鉴相算法完成I、Q路基带信号的运算,输出相位误差电压。

第四,环路滤波器模块,实现比例-积分滤波功能,将鉴相器输出的误差电压转换为控制VCO的电压信号。

第五,VCO模块,根据输入的控制电压调整输出载波的相位与频率,完成环路的闭环控制。

对应课程内容:

6.基于FPGA的costas环开发1------发射端信号产生模块

7.基于FPGA的costas环开发2------解调端下变频模块

8.基于FPGA的costas环开发3------解调端低通滤波器模块

9.基于FPGA的costas环开发4------鉴相器模块开发

10.基于FPGA的costas环开发5------环路滤波器模块开发

11.基于FPGA的costas环开发6------costas完整闭环

Costas环的核心性能分析。

第一,频偏锁定收敛曲线的稳定性分析,通过Verilog程序采集环路收敛过程中的相位误差数据,分析收敛曲线的平稳性,验证硬件环路的稳定性。

第二,频偏锁定范围测试分析,调整输入信号与VCO的初始频偏,测试硬件环路的最大锁定频偏,并制作操作讲解视频演示测试流程。

第三,分析不同信噪比下硬件环路的频偏锁定性能,对比仿真结果与硬件测试结果的差异。

第四,完成多径信道的Verilog设计,模拟无线通信中的多径衰落现象,探究多径干扰对Costas环同步性能的影响,并开展多径信道下的频偏锁定性能仿真分析。

对应课程内容:

12.基于FPGA的costas环性能测试1------频偏锁定收敛曲线的稳定性分析

13.基于FPGA的costas环性能测试2------频偏锁定范围测试分析

14.信噪比SNR对Costas环的性能影响分析1------AWGN信道模型的FPGA实现

15.信噪比SNR对Costas环的性能影响分析2------不同信噪比下costas环的频偏锁定性能仿真分析

16.多径干扰对Costas环的性能影响分析1------多径信道verilog设计

17.多径干扰对Costas环的性能影响分析2------多径信道下costas环的频偏锁定性能仿真分析

硬件片内测试。

第一、进行模块封装、接口约束与IP核配置,将各功能模块封装为可复用的IP核,设置合理的引脚约束,并配置VIO核与ILA 核,实现对内部信号的在线观测与参数配置,配套编写了完整的Verilog 程序。

第二、开展硬件测试与分析,将程序下载至FPGA开发板,通过ILA核采集I、Q路信号、相位误差信号等关键波形,分析环路的收敛过程与同步性能,并制作操作讲解视频,展示硬件测试的全流程。

第三、对Costas环FPGA工程进行了全面的时序、资源消耗与功耗分析。

对应课程内容:

18.Costas环开发板硬件片内测试1------模块封装/接口约束/vio核/ila核配置