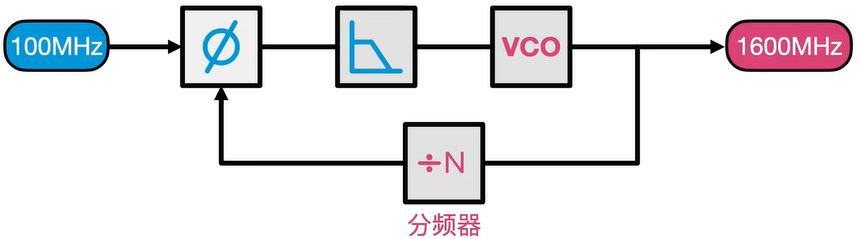

一、锁相环 (PLL) 结构概述

1.1 基本框图

在下图中,是一个锁相环示例图:

- f1:输入频率

- f2:倍频后的输出频率

- 鉴相器:比较两个相位,并输出相位误差

- 低通滤波器:让低频信号通过,抑制高频信号的滤波器

- 压控振荡器:由输入电压控制输出频率的振荡器

- 分频器:将输入的频率按除固定值再输出

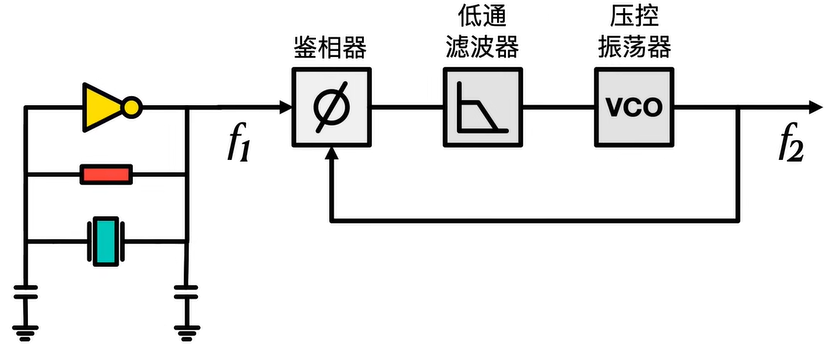

1.2 输入频率

输入频率 f1 是一个稳定的频率源,比如他可能是一个晶振电路:

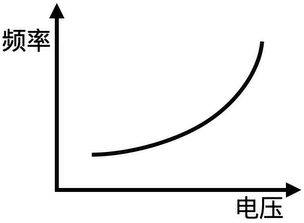

1.3 压控振荡器

压控振荡器 (VCO,Voltage-Controlled Oscillator):输出频率 (或角速度) 由输入电压控制的振荡器。

输入电压,输出频率。

输入电压越高,输出频率越高。但是因为我们的输出电压有微小的波动,就对输出的频率有影响,所以需要其他的元件做频率的闭环控制。

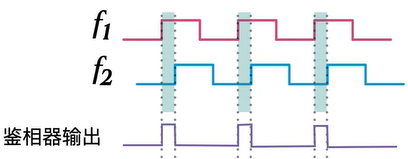

1.4 鉴相器

鉴相器 (Phase Detector,PD):用来比较两个相位,并输出相位误差的模块。

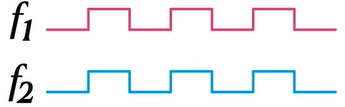

在下图中,鉴相器将目标频率和反馈频率作比较:

鉴相器输出根据相位的相位差做出输出,相位差越大,输出越大:

1.5 低通偏滤器

由于鉴相器输出的波形是方波,通过低通滤波器即可过滤成平滑的电压供压控振荡器使用。

至此,这个系统便可以让压控振荡器输出 f2 跟随 我们输入的频率 f1。

1.6 分频器

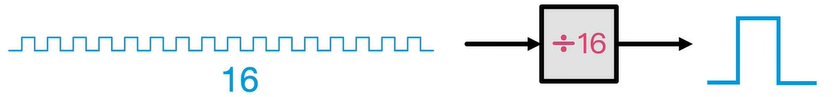

分频器 (Frequency Divider) ,顾名思义,就是把输入信号的频率按一定比例分掉,输出更低频率信号的电路或算法。

分频器:输出频率 = 输入频率 ÷ N

其中 N 称为分频比 (可以是 2、4、8 等,也可以是任意整数,某些情况下还能是小数)。

使用 N = 16 的分频器后,输入 16 个方波,分频器输出 1 个方波。

最后,我们将传给鉴相器的频率进行分频,即可得到倍频后的频率了,其倍频的后的 f2 频率就是 f1 频率乘分频器的分频值。