多路选择器与三态门:数字电路中的"守门员"机制详解

在数字电路的世界里,数据的流动并非杂乱无章,而是受到精密控制的。就像城市交通需要红绿灯、高速公路需要收费站一样,数字信号在传输过程中也需要"守门员"来决定哪些数据可以通过,哪些必须被拦截 。今天我们要深入讲解的两个核心组件------多路选择器(Multiplexer) 和 三态门(Tri-state Buffer),正是扮演着这样的角色。

很多初学者,尤其是跨考计算机或电子工程的同学,常常对这两个器件感到困惑:它们看起来功能相似,图形符号又容易混淆,到底该如何区分?它们在实际电路中又起到什么作用?本文将从基本结构、工作原理、图形表示、控制逻辑到实际应用,一层层剥开它们的神秘面纱,让你彻底掌握这两个数字电路中的"守门员"。

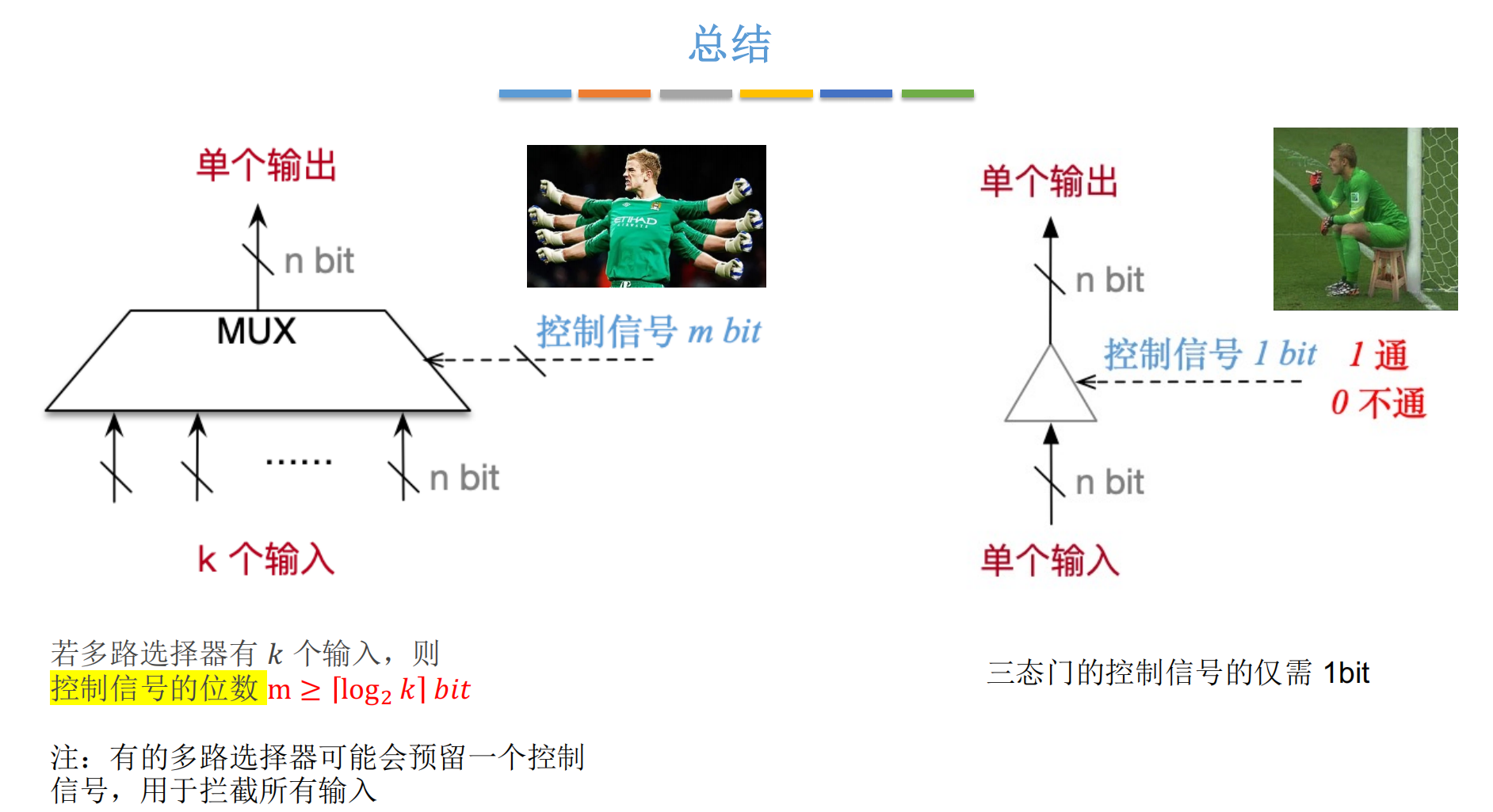

一、多路选择器(Multiplexer):拥有"三头六臂"的智能守门员

1.1 什么是多路选择器?

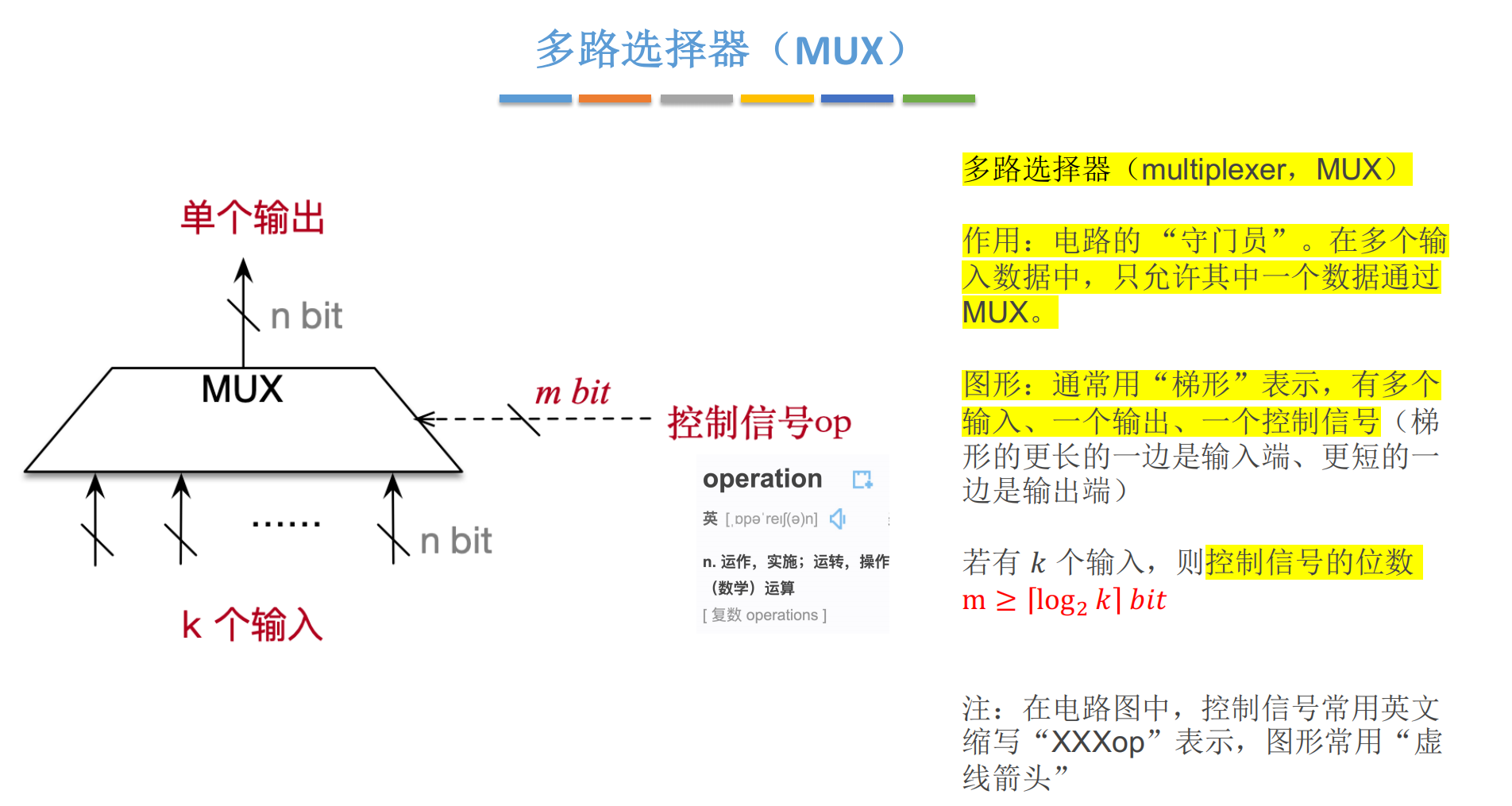

多路选择器,英文名为 Multiplexer ,通常缩写为 MUX 。它的核心功能非常直观:从多个输入信号中,根据控制信号的选择,只让其中一个通过并输出,其余全部阻断。

你可以把它想象成一个拥有三头六臂的超级守门员 。面前有 kkk 条数据通道(输入),但他只能打开其中一条,让对应的数据流出去,其他通道则被牢牢封锁。

1.2 基本结构与工作原理

一个多路选择器包含三个关键部分:

- 多个输入端(Inputs) :通常标记为 I0,I1,I2,...,Ik−1I_0, I_1, I_2, \dots, I_{k-1}I0,I1,I2,...,Ik−1,共 kkk 个。

- 一个输出端(Output) :标记为 YYY。

- 控制信号(Control Signal) :也称为选择信号(Select Lines) ,用 S0,S1,...,Sm−1S_0, S_1, \dots, S_{m-1}S0,S1,...,Sm−1 表示,共 mmm 位。

工作过程如下:

- 控制信号给出一个 mmm 位的二进制值;

- 该值被解释为一个索引(例如

01表示索引 1); - 多路选择器将对应索引的输入信号(如 I1I_1I1)连接到输出端;

- 其他所有输入信号被断开,无法影响输出。

✅ 关键点 :任何时候,只有一个输入能"说话",其他都保持沉默。

1.3 控制信号位数的计算逻辑

这里有一个非常重要的数学关系:当输入数量为 kkk 时,控制信号的位数 mmm 必须满足:

m≥⌈log2k⌉ m \geq \lceil \log_2 k \rceil m≥⌈log2k⌉

为什么?因为 mmm 位二进制数最多能表示 2m2^m2m 个不同的状态。要覆盖 kkk 个输入,就必须有 2m≥k2^m \geq k2m≥k,即 m≥log2km \geq \log_2 km≥log2k。由于位数必须是整数,所以向上取整。

举个例子:

- 2 输入 MUX :k=2k = 2k=2,log22=1\log_2 2 = 1log22=1,所以 m=1m = 1m=1 位控制信号(0 或 1)。

- 4 输入 MUX :k=4k = 4k=4,log24=2\log_2 4 = 2log24=2,所以 m=2m = 2m=2 位(

00,01,10,11)。 - 8 输入 MUX :k=8k = 8k=8,log28=3\log_2 8 = 3log28=3,所以 m=3m = 3m=3 位。

📌 注意 :控制信号的每一位通常用 S0S_0S0(最低位)、S1S_1S1、S2S_2S2......表示,组合起来形成一个二进制地址。

1.4 电路图表示规范

在数字电路图中,多路选择器通常用梯形符号表示:

- 宽边(底部) :代表多个输入端;

- 窄边(顶部) :代表单一输出端;

- 腰部虚线箭头 :代表控制信号,指向梯形内部。

此外,控制信号常被标注为 OP(Operation 的缩写),意为"操作选择"。在绘图规范中:

- 实线 :通常表示数据信号(携带实际信息);

- 虚线 :通常表示控制信号(不携带数据,只起选择作用)。

⚠️ 虽然这不是绝对规则(有些教材用实线画控制信号),但理解"控制 vs 数据"的区分非常重要。

1.5 实际例子解析

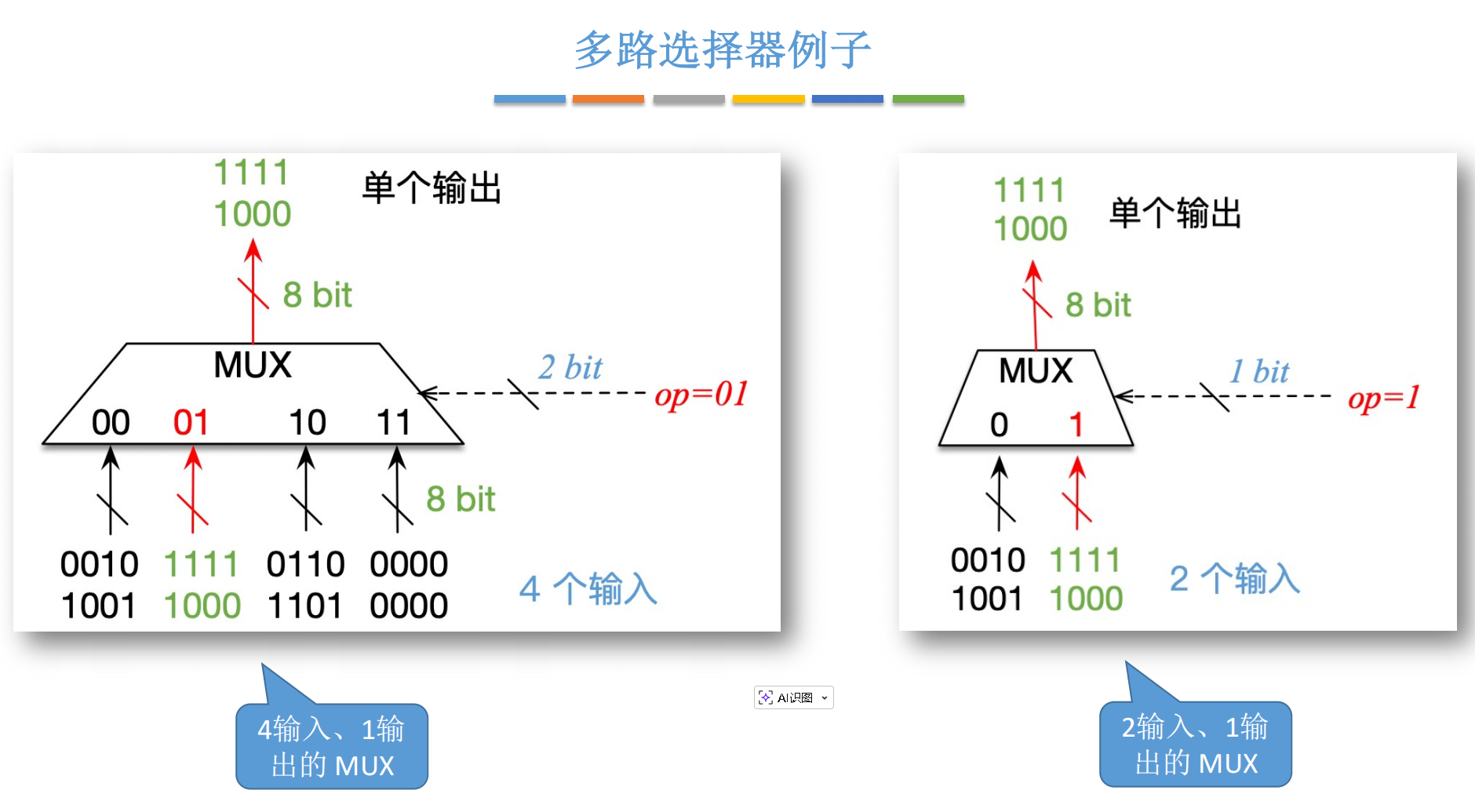

例1:4 输入多路选择器

- 输入:I0,I1,I2,I3I_0, I_1, I_2, I_3I0,I1,I2,I3

- 控制信号:2 位,记为 S1S0S_1S_0S1S0

- 真值表如下:

| S1S_1S1 | S0S_0S0 | 输出 YYY |

|---|---|---|

| 0 | 0 | I0I_0I0 |

| 0 | 1 | I1I_1I1 |

| 1 | 0 | I2I_2I2 |

| 1 | 1 | I3I_3I3 |

当控制信号为 01 时,S1=0,S0=1S_1=0, S_0=1S1=0,S0=1,对应十进制 1,因此输出 I1I_1I1,其他输入被阻断。

例2:2 输入多路选择器(最简形式)

- 输入:A,BA, BA,B

- 控制信号:1 位,记为 SSS

- 功能:

- 若 S=0S = 0S=0,输出 AAA

- 若 S=1S = 1S=1,输出 BBB

这其实就是一个二选一开关,在 CPU 的 ALU(算术逻辑单元)中极为常见,用于选择加法还是减法结果。

1.6 特殊情况:支持"全关闭"状态的多路选择器

前面我们假设:kkk 个输入中,总有一个会被选中输出 。但在某些高级设计中,可能需要一种状态:所有输入都不输出,即输出处于"无效"或"高阻"状态。

这时,控制信号的状态数就需要覆盖 k+1k + 1k+1 种情况(kkk 个输入 + 1 个"全关"状态)。因此,控制信号位数变为:

m≥⌈log2(k+1)⌉ m \geq \lceil \log_2 (k + 1) \rceil m≥⌈log2(k+1)⌉

例如:

- 4 输入 MUX 若需支持"全关",则需 ⌈log25⌉=3\lceil \log_2 5 \rceil = 3⌈log25⌉=3 位控制信号(8 种状态,用 5 种,3 种冗余)。

这种设计在总线系统中很有用,可以避免多个设备同时驱动总线导致冲突。

二、三态门(Tri-state Buffer):单通道的"通断开关"

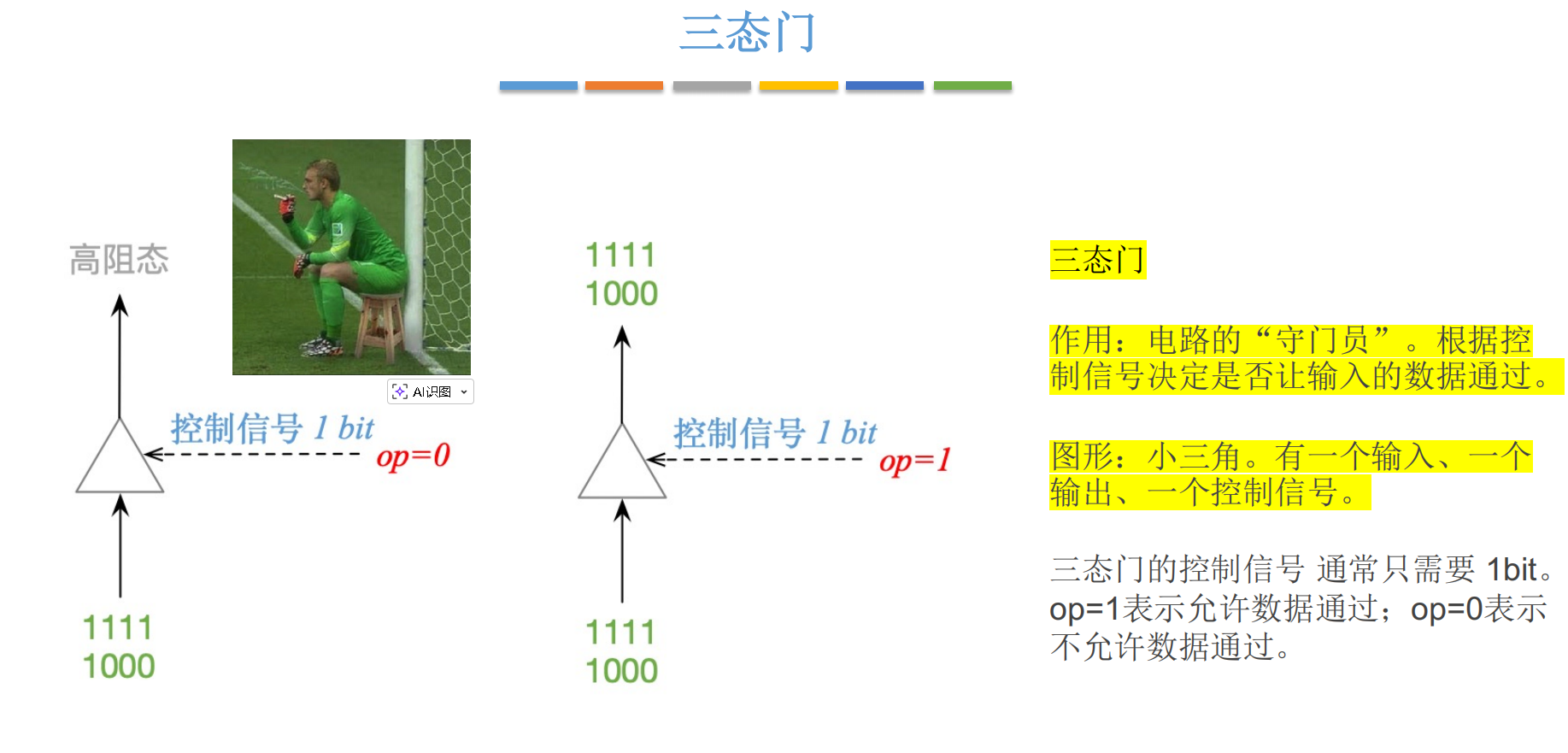

如果说多路选择器是"多通道守门员",那么三态门就是只负责一条线路的普通守门员。

2.1 基本功能与结构

三态门的核心功能极其简单:

- 当控制信号为 1 时 :输入信号直接通过,输出 = 输入;

- 当控制信号为 0 时 :输出进入高阻态(High-Impedance State) ,相当于断开电路。

它只有:

- 一个输入端

- 一个输出端

- 一个控制端(Enable)

2.2 什么是高阻态(High-Z)?

这是理解三态门的关键!

在数字电路中,我们通常用两种电压表示逻辑值:

- 高电平(High):如 +5V,代表逻辑 1;

- 低电平(Low):如 0V 或 +1V,代表逻辑 0。

但高阻态(记作 Z) 是第三种状态:

- 输出端呈现极高电阻,几乎不输出电流;

- 电压不确定,由外部电路决定;

- 物理上等效于"断开导线"。

💡 想象一下:你把一根电线剪断了,两端悬空------这就是高阻态。它既不是 0,也不是 1,而是"无连接"。

2.3 电路图表示

三态门在电路图中用小三角形表示:

- 底边:输入端;

- 顶点:输出端;

- 腰部:控制信号输入端。

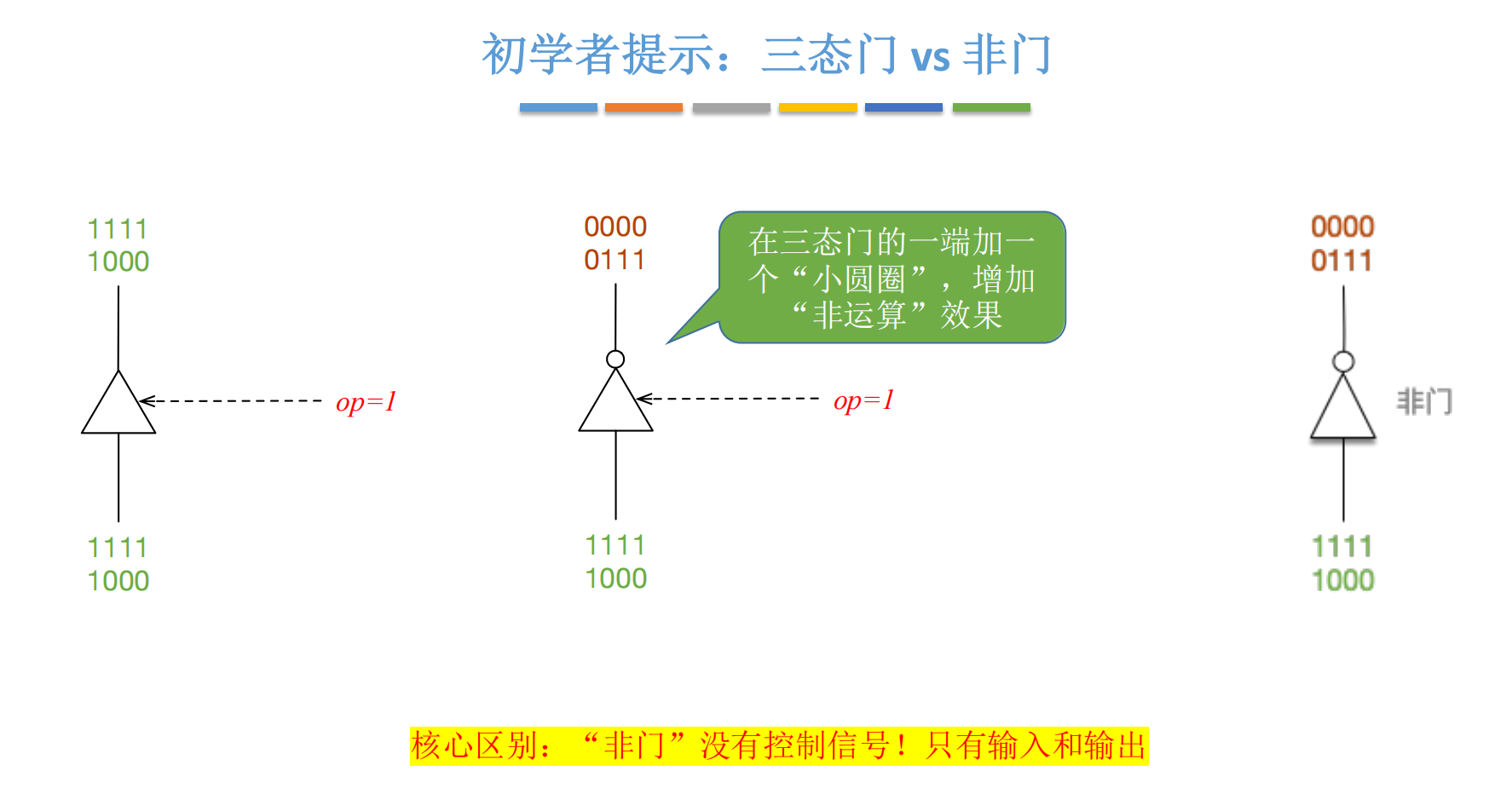

带取反功能的三态门

有时你会看到三角形输出端带一个小圆圈。这表示:

- 当控制信号有效(通常为 1)时,输出 = 输入的反相(NOT);

- 当控制信号无效(0)时,输出仍为高阻态。

🔍 注意 :这个小圆圈只在导通时起取反作用,不影响高阻态行为。

2.4 三态门 vs 非门:如何区分?

初学者很容易把带圆圈的三态门和非门(NOT Gate)混淆。它们的区别在于:

| 特性 | 三态门(带圆圈) | 非门(NOT Gate) |

|---|---|---|

| 控制信号 | 有(必须存在) | 无 |

| 输出状态 | 导通时取反,否则高阻 | 永远取反,无高阻态 |

| 功能本质 | 可控通断 + 可选取反 | 强制取反 |

✅ 判断技巧 :

看图形是否有第三个引脚(控制端) 。

有 → 三态门;

无 → 非门。

2.5 为什么需要三态门?------ 总线共享的关键

三态门最重要的应用场景是总线(Bus)系统。

在计算机中,多条设备(如 CPU、内存、I/O)需要共享同一组数据线 。如果多个设备同时输出信号,就会发生短路或逻辑冲突。

解决方案:每个设备的输出都经过一个三态门,由控制信号决定谁"说话":

- CPU 需要发送数据 → 使能 CPU 的三态门,其他设备的三态门关闭(高阻态);

- 内存需要响应 → 使能内存的三态门,CPU 关闭。

这样,同一时刻只有一条设备驱动总线,避免冲突。

🌟 没有三态门,就没有现代计算机的总线架构!

三、多路选择器 vs 三态门:深度对比与联系

虽然两者都起"守门"作用,但它们的设计哲学和应用场景截然不同。

| 维度 | 多路选择器(MUX) | 三态门(Tri-state) |

|---|---|---|

| 输入数量 | 多个(k≥2k \geq 2k≥2) | 仅 1 个 |

| 输出状态 | 总有确定输出(0 或 1) | 可能为高阻态(Z) |

| 控制复杂度 | 控制信号多位,编码选择 | 控制信号单 bit,通/断 |

| 核心用途 | 数据选择(从多源选一) | 总线隔离(避免多驱动冲突) |

| 能否级联实现对方? | 可用多个三态门 + 译码器模拟 MUX | MUX 无法直接实现高阻态输出 |

3.1 用三态门构建多路选择器

有趣的是,多路选择器可以用三态门 + 译码器(Decoder)来实现:

- 用译码器将 mmm 位控制信号转换为 kkk 条独热(One-hot)使能线;

- 每条使能线连接一个三态门,控制对应的输入;

- 所有三态门的输出并联到同一根总线上。

此时,总线上的输出就是被选中的那个输入,其他三态门处于高阻态,不干扰。

这正是早期 TTL 芯片(如 74LS157)的实现方式。

3.2 为什么不用三态门替代所有 MUX?

虽然可行,但有缺点:

- 速度慢:三态门切换有延迟,高阻态恢复需要时间;

- 功耗高:多个三态门同时存在,即使关闭也有漏电流;

- 噪声敏感:高阻态易受干扰,需额外上拉/下拉电阻。

而专用 MUX 电路是纯组合逻辑,无高阻态,速度更快、更稳定。

四、总结:守门员的分工与协作

-

多路选择器 是 "多选一"的决策者 ,用于在多个数据源中主动选择 一个进行处理。它永远有确定输出,是数据路径的核心开关。

-

三态门 是 "单路通断"的隔离器 ,用于在共享总线上防止冲突 。它能进入高阻态,是总线架构的基石。

🔑 记住这个比喻:

- MUX 像 KTV 包厢的点歌台 ------ 从几百首歌里选一首播放;

- 三态门像 会议室的麦克风开关 ------ 谁发言就打开谁的麦,其他人静音(高阻)。

理解这两个器件,不仅是掌握数字电路的基础,更是理解 CPU、内存、总线等复杂系统如何协同工作的关键一步。希望本文能帮你彻底扫清疑惑,为后续学习打下坚实基础。