初始化

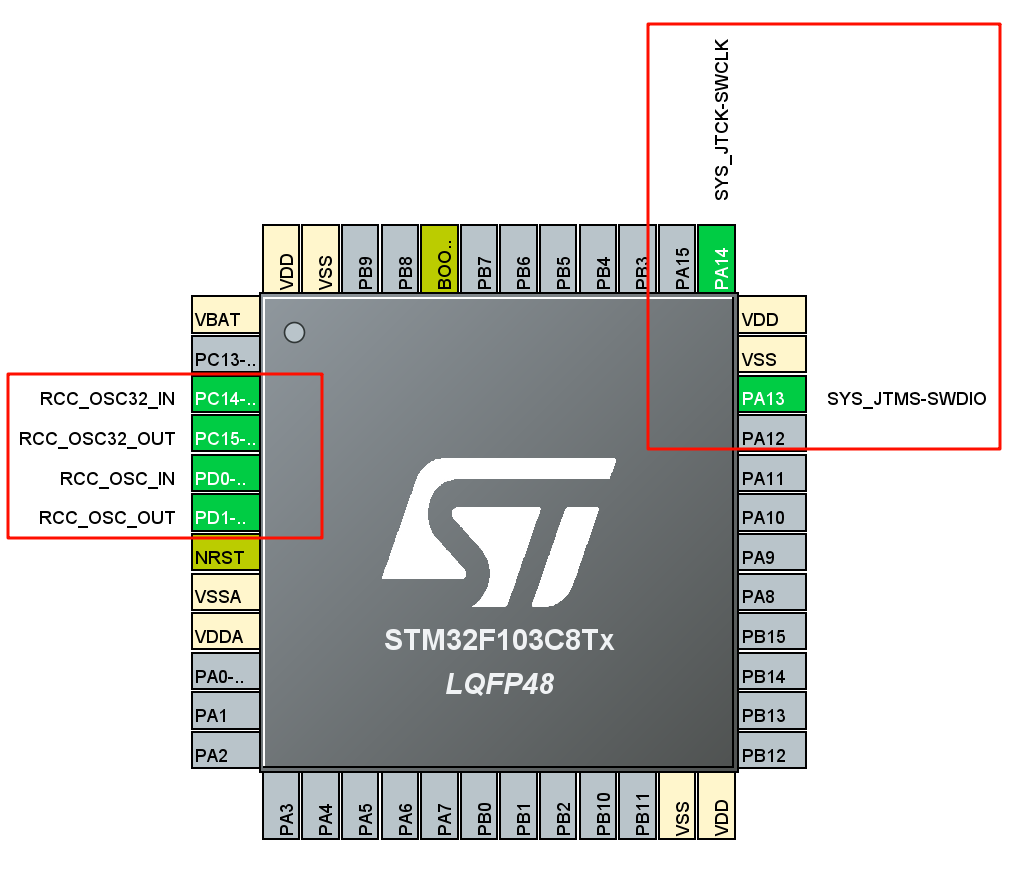

PA13和PA14

PA13(SYS_JTMS-SWDIO)和PA14(SYS_JTCK-SWCLK)是 STM32F103 的调试接口引脚 ,开启这个功能的核心作用是实现程序下载 + 在线调试。

具体作用拆解:

这两个引脚对应的是SWD 调试接口(Serial Wire Debug,串行调试),是 STM32 最常用的调试方式之一:

-

PA13(SWDIO) :是 "串行调试数据输入 / 输出引脚",负责调试器与芯片之间的双向数据传输(比如下载程序、读取寄存器、设置断点等)。

-

PA14(SWCLK) :是 "串行调试时钟引脚",负责同步调试器与芯片的通信节奏(由调试器提供时钟信号)。

开启这个功能的实际价值:

- 程序下载:通过 ST-Link 等调试器,把编译好的代码烧录到 STM32 的 Flash 中;

- 在线调试:可以实时查看变量值、单步执行代码、设置断点、观察寄存器状态,快速定位程序 BUG;

- 低引脚占用:SWD 只需要 2 个引脚(比传统 JTAG 的 5 个引脚更节省资源),是 STM32 开发中最常用的调试方式。

注意:

这两个引脚默认就是 "调试模式",如果要把它们当普通 GPIO 用,需要额外配置(但不建议,会失去调试功能)。

PD0/PD1和PC14/PC15

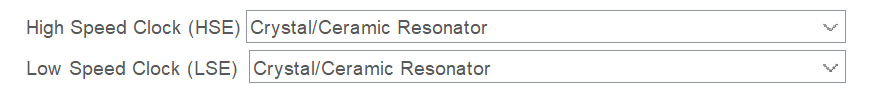

上方区域:高速外部时钟(HSE)

- 引脚对应 :

PD0(RCC_OSC_IN)和PD1(RCC_OSC_OUT)是 HSE 的硬件引脚; - 功能 :用于连接高速外部晶振 / 陶瓷谐振器(比如 8MHz、12MHz 晶振),给 STM32 提供高频时钟源(最终可通过倍频得到 72MHz 系统主频);

- 配置项 :

High Speed Clock (HSE)选择了Crystal/Ceramic Resonator,表示启用 HSE 并使用外部晶振。

下方区域:低速外部时钟(LSE)

- 引脚对应 :

PC14(RCC_OSC32_IN)和PC15(RCC_OSC32_OUT)是 LSE 的硬件引脚; - 功能 :用于连接低速外部晶振(通常是 32.768kHz 晶振),主要给实时时钟(RTC)提供精准的计时时钟;

- 配置项 :

Low Speed Clock (LSE)选择了Crystal/Ceramic Resonator,表示启用 LSE 并使用外部 32.768kHz 晶振。

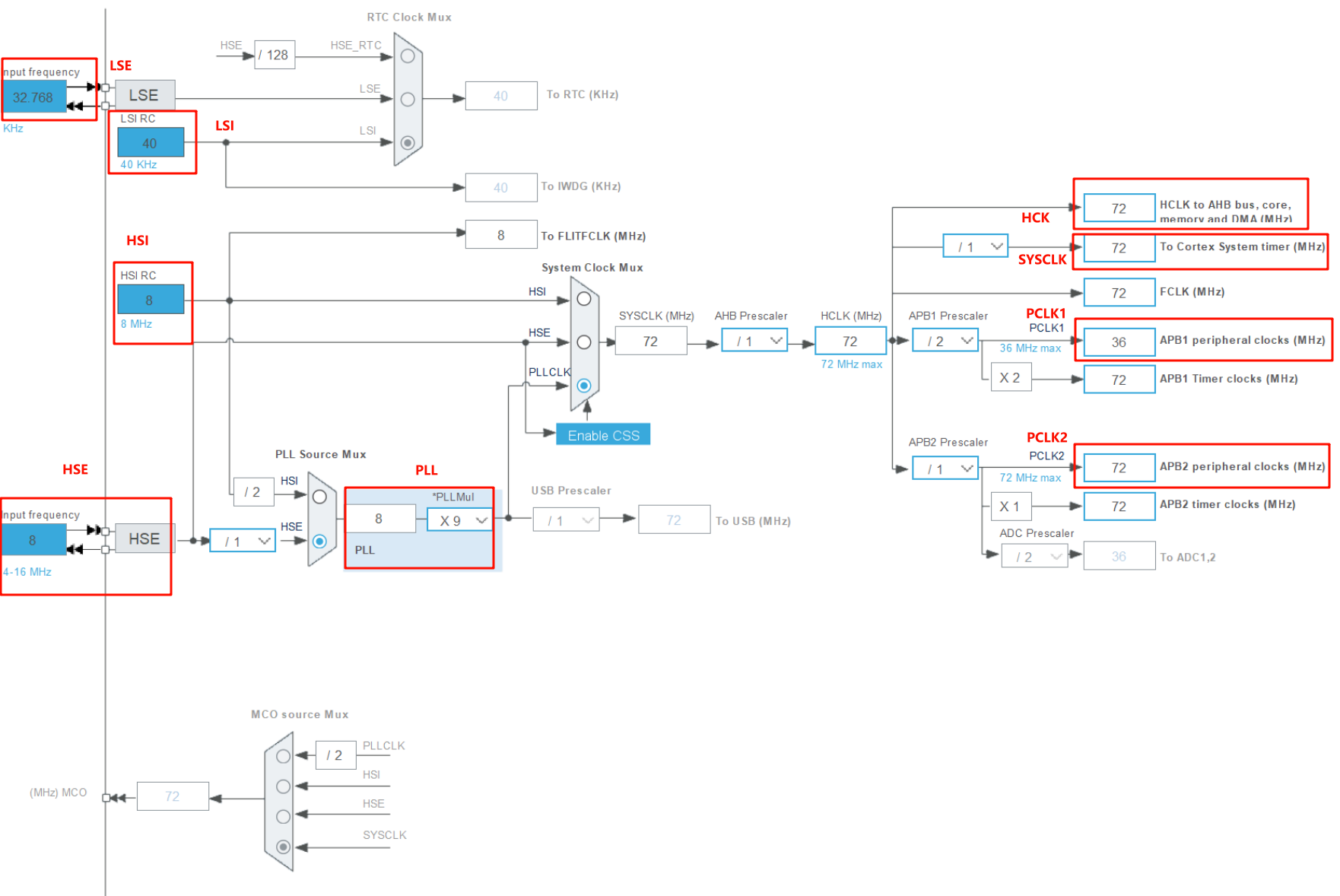

时钟树

STM32 的时钟树配置图(通过 CubeMX 等工具生成),展示了芯片内部所有时钟源、分频 / 倍频模块的连接关系,最终决定系统及外设的运行频率。核心模块拆解:

一、左侧:时钟源(3 个基础时钟)

-

LSE(低速外部时钟)

- 输入频率:32.768kHz(对应你之前图里的 PC14/PC15 外接晶振)

- 用途:给 RTC(实时时钟)提供精准计时时钟。

-

HSI(高速内部时钟)

- 频率:8MHz(芯片内置 RC 振荡器,无需外接硬件)

- 特点:启动快,但精度不如外部晶振。

-

HSE(高速外部时钟)

- 输入频率:8MHz(对应你之前图里的 PD0/PD1 外接晶振)

- 特点:精度高,是系统主时钟的常用源。

二、中间:PLL(锁相环,时钟倍频核心)

PLL 是 "倍频器",用于把低频时钟放大到高频:

- 来源:选择 HSE 作为 PLL 输入源(

PLL Source Mux选了 HSE); - 倍频配置:

PLLMUL设为x9(图中显示 "X9")→ 8MHz × 9 = 72MHz; - 输出:PLLCLK = 72MHz,最终作为系统主时钟(SYSCLK)。

三、右侧:时钟分配(系统及外设时钟)

SYSCLK(72MHz)经过分频器,分配给不同模块:

-

HCLK(AHB 总线时钟)

- 分频:AHB Prescaler 设为

/1→ HCLK = 72MHz; - 用途:给内核、内存、DMA 等核心模块提供时钟。

- 分频:AHB Prescaler 设为

-

PCLK1(APB1 总线时钟)

- 分频:APB1 Prescaler 设为

/2→ PCLK1 = 36MHz; - 用途:给低速外设(如 USART2、I2C 等)提供时钟;

- 注意:APB1 定时器时钟会 ×2 → 72MHz(保证定时器精度)。

- 分频:APB1 Prescaler 设为

-

PCLK2(APB2 总线时钟)

- 分频:APB2 Prescaler 设为

/1→ PCLK2 = 72MHz; - 用途:给高速外设(如 GPIO、USART1、SPI1 等)提供时钟;

- APB2 定时器时钟 ×1 → 72MHz。

- 分频:APB2 Prescaler 设为

总结

这个配置的最终效果是:

- 系统主频率(SYSCLK)= 72MHz(STM32F103 的常用最大主频);

- 外设时钟按需分频(PCLK1=36MHz、PCLK2=72MHz);

- 同时保留了 RTC 的精准 32.768kHz 时钟。

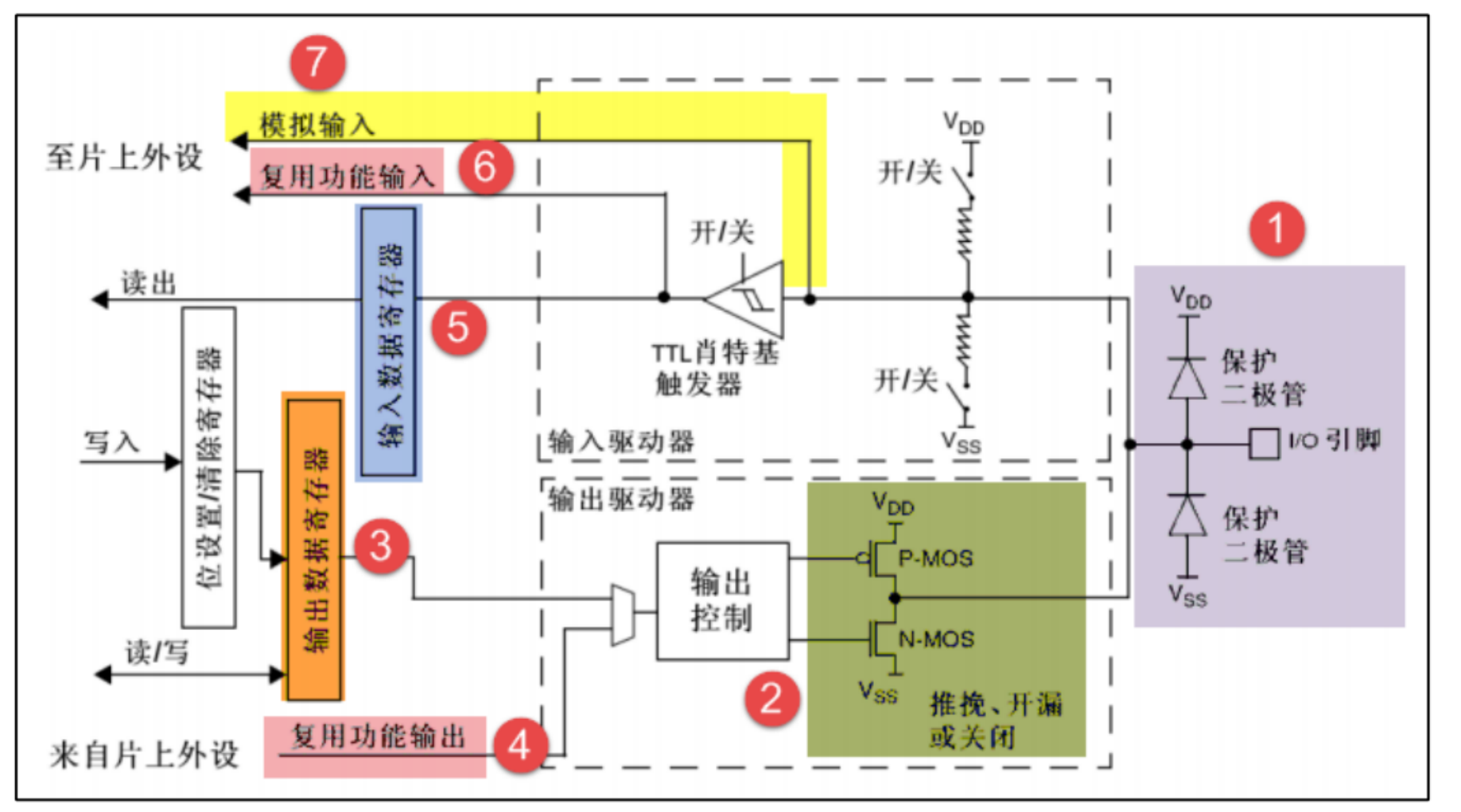

GPIO内部结构

1. 保护二极管引脚功能

保护二极管用于防止引脚外部电压异常损坏芯片。当引脚电压高于VDD时,上方的二极管导通;当电压低于VSS时,下方的二极管导通,将异常电压钳位至电源或地。

2. GPIO上拉/下拉电阻配置

上拉电阻 :在输入模式下,若引脚悬空,上拉电阻将电平拉高至VDD,避免不确定状态。外部设备连接时,上拉电阻不影响设备电平。

下拉电阻:类似上拉电阻,但将悬空引脚电平拉低至VSS。外部设备连接时,下拉电阻同样不干扰设备状态。

3. 输出驱动器结构(P-MOS与N-MOS)

推挽输出模式

- 输入高电平时:P-MOS导通,N-MOS关闭,输出高电平(VDD)。

- 输入低电平时:N-MOS导通,P-MOS关闭,输出低电平(VSS)。

适用于需高速切换0/3.3V电平的场景。

开漏输出模式

- P-MOS始终关闭,仅N-MOS受控。

- 输出0时:N-MOS导通,引脚接地。

- 输出1时:N-MOS关闭,引脚呈高阻态(需外部上拉电阻输出高电平)。

适用于需线与逻辑或兼容不同电压的场景。

4. 输出数据寄存器(GPIOx_ODR)

通过修改GPIOx_ODR的值直接控制输出驱动器的双MOS管结构,改变引脚输出电平。

5. 复用功能输出

GPIO引脚可配置为外设功能(如USART、SPI、定时器等)。例如:

- PA9可复用为USART1_TX或TIM2_CH2。

通过设置复用功能寄存器选择具体功能。

6.输入数据路径

输入数据寄存器(GPIOx_IDR)

引脚信号经上/下拉电阻和施密特触发器后,转换为数字信号并存储在GPIOx_IDR中,读取该寄存器可获取引脚电平。

复用功能输入

引脚信号直接传输至其他外设(如USART_RX),由外设读取状态。需配置为复用输入模式。

7.模拟输入(ADC通道)

信号绕过施密特触发器,直接接入ADC外设以采集原始模拟电压。适用于需高精度模拟信号检测的场景。