几对差分控多少Ω阻抗,单端又控多少,怎么计算?

在高速 PCB 设计中,差分阻抗 和单端阻抗的控制值及计算方法是保障信号完整性的核心,不同总线协议(如 USB、HDMI、以太网)对阻抗有明确规范,以下是详细解析:

一、 常见阻抗标准(行业通用值)

| 信号类型 | 差分阻抗标准 | 单端阻抗标准 | 典型应用场景 |

|---|---|---|---|

| USB 2.0/3.0 | 90Ω±10% | 45Ω±10% | 高速数据传输、外设连接 |

| HDMI 1.4/2.0 | 100Ω±10% | 50Ω±10% | 音视频高清传输 |

| Ethernet(千兆网) | 100Ω±10% | 50Ω±10% | RJ45 网口、网络通信 |

| DDR3/DDR4 | 差分:100Ω±10%;单端:50Ω±10% | --- | 内存数据 / 地址 / 控制信号 |

| LVDS(低压差分) | 100Ω±10% | 50Ω±10% | 显示屏、高速串行通信 |

| SATA | 100Ω±10% | 50Ω±10% | 硬盘数据传输 |

核心规律:

- 差分阻抗 ≈ 2× 单端阻抗(因差分线存在耦合效应,实际略小于 2 倍,如 45Ω 单端→90Ω 差分);

- 绝大多数高速信号的单端阻抗为 50Ω (射频 / 微波常用 50Ω 匹配特性阻抗),差分阻抗为 90Ω/100Ω(根据协议选择)。

二、 阻抗计算原理(影响因素)

PCB 阻抗的本质是信号路径的特性阻抗 ,由导体电阻、电感、电容及介质参数共同决定,高速信号(频率 > 100MHz)以电感和电容的分布参数 为主,计算公式基于传输线理论的微带线 / 带状线模型。

1. 关键影响参数

| 参数 | 说明 |

|---|---|

| 线宽(W) | 导线宽度越大,阻抗越低;反之越高。 |

| 线距(S) | 差分线间距越小,耦合越强,差分阻抗越低;反之越高。 |

| 介质厚度(H) | 导线到参考平面(地 / 电源层)的距离,H 越大,阻抗越高。 |

| 介质介电常数(εr) | PCB 板材的介电常数(如 FR-4 的 εr≈4.2~4.5),εr 越大,阻抗越低。 |

| 铜厚(T) | 导线铜箔厚度,T 越大,阻抗越低;反之越高。 |

| 阻焊厚度(C) | 阻焊层的介电常数(≈3.5)和厚度,会轻微降低阻抗(通常忽略,精密设计需考虑)。 |

2. 两种常见传输线模型的计算公式

高速 PCB 中,阻抗控制主要针对 微带线(表层信号) 和 带状线(内层信号) 两种结构:

(1)单端微带线(表层,有一个参考平面)

适用于表层单端信号,公式简化版(工程常用):

:单端特性阻抗(Ω)

:单端特性阻抗(Ω) :介质介电常数

:介质介电常数- H:线到参考平面的距离(mil/mm)

- W:线宽(mil/mm)

- T:铜厚(mil/mm)

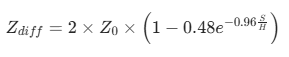

(2)差分微带线(表层,耦合型)

适用于表层差分信号,公式简化版:

:差分特性阻抗(Ω)

:差分特性阻抗(Ω) :单端微带线阻抗(无耦合时)

:单端微带线阻抗(无耦合时)- S:差分线中心间距

- H:线到参考平面的距离

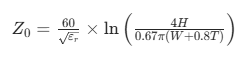

(3)带状线(内层,上下两个参考平面)

阻抗更稳定(不受外界干扰),单端带状线公式:

- H:上下参考平面的平均距离(内层介质厚度的一半)

三、 实操计算方法(不用手算!用工具)

手算公式误差大(±10% 以上),工程中100% 使用专业阻抗计算工具,推荐 3 类工具:

1. PCB 设计软件内置工具

- Altium Designer :

工具 → 阻抗计算器,输入板材参数(εr、H、T)、线宽 / 线距,自动计算阻抗,支持微带线 / 带状线 / 差分线。 - Cadence Allegro :

PCB Editor → Constraint Manager,配置阻抗规则,联动线宽设计。

2. 在线阻抗计算器(免费便捷)

- PCB Impedance Calculator (如pcbcalculator.com):输入参数直接出结果,适合快速验证。

- Saturn PCB Design Toolkit:桌面小工具,支持多种传输线模型。

3. 板材厂商提供的计算器

- 如罗杰斯(Rogers)、生益科技等板材厂商,会提供针对自家板材的阻抗计算工具(εr 参数精准,误差 < 5%)。

四、 阻抗控制的核心注意事项

- 优先内层带状线:内层信号受参考平面约束,阻抗更稳定,EMI 辐射更小;表层微带线需注意阻焊层和外界干扰的影响。

- 差分线等长等距 :差分阻抗控制的前提是线宽一致、间距一致、长度一致(误差 < 5mil),否则耦合不均导致阻抗突变。

- 参考平面连续:阻抗计算的核心是 "信号有稳定的参考平面",禁止在阻抗线下方分割地 / 电源层,否则回流路径断裂,阻抗急剧变化。

- 铜厚与线宽匹配:1oz 铜厚(≈35μm)时,50Ω 单端微带线(FR-4,H=1.0mm)的线宽约为 0.8~1.0mm;铜厚增加,线宽需减小才能保持阻抗不变。

- 公差控制:量产 PCB 的阻抗公差通常要求 ±10%,精密高速信号(如 DDR5)需 ±5%,需提前与 PCB 厂确认工艺能力。

五、 举例:50Ω 单端微带线计算(FR-4 板材)

已知参数:εr=4.3,H=0.8mm(线到地平面距离),铜厚 T=1oz(0.035mm)代入简化公式计算:

通过工具反算得:线宽 W≈0.6mm(实际生产中需 PCB 厂微调,因板材 εr 存在批次差异)。

不同总线协议对阻抗有哪些明确规范?

在高速硬件设计中,不同总线协议的阻抗规范是保障信号完整性(SI)、降低电磁干扰(EMI)的核心标准,协议制定方会明确规定单端阻抗、差分阻抗及公差范围。以下是工业界主流总线协议的阻抗规范汇总,按应用场景分类说明:

一、 高速串行总线(差分信号为主)

这类总线以差分传输为核心,阻抗规范聚焦差分阻抗,单端阻抗通常为差分的 1/2 左右(因耦合效应,实际略低)。

| 总线协议 | 差分阻抗标准 | 单端阻抗参考 | 公差要求 | 典型应用 | 核心注意事项 |

|---|---|---|---|---|---|

| USB 2.0 | 90Ω±10% | 45Ω±10% | ±10% | 外设、U 盘、键鼠 | 低速 / 全速模式可放宽,高速(480Mbps)必须严格控制 |

| USB 3.2 Gen1/Gen2 | 90Ω±10% | 45Ω±10% | ±8%(Gen2) | 高速存储、USB-C 设备 | 需等长走线(差分对内等长误差 < 5mil),参考平面连续 |

| HDMI 1.4/2.0/2.1 | 100Ω±10% | 50Ω±10% | ±10% | 高清显示、音视频传输 | TMDS 差分对阻抗一致性要求高,HDMI 2.1(48Gbps)需更低损耗板材 |

| DisplayPort (DP) | 100Ω±10% | 50Ω±10% | ±10% | 电竞显示器、笔记本投屏 | 支持多通道拼接,每对差分阻抗需匹配 |

| LVDS(低压差分信号) | 100Ω±10% | 50Ω±10% | ±10% | 工业屏、摄像头模组、高速数据采集 | 低功耗、抗干扰强,阻抗不匹配会导致拖影 |

| SATA 3.0 | 100Ω±10% | 50Ω±10% | ±10% | 固态硬盘、机械硬盘 | 需远离电源干扰,差分对长度误差 < 10mil |

| PCIe Gen1~Gen5 | 85Ω±10%(Gen1-4)80Ω±10%(Gen5) | 42Ω/40Ω | ±8%(Gen5) | 显卡、NVMe 固态硬盘、服务器扩展 | Gen5(32Gbps / 通道)需超低损耗(EL)板材,阻抗公差更严 |

二、 以太网总线(有线网络)

以太网协议分百兆、千兆、万兆,阻抗规范随速率提升而更严格,核心是差分阻抗匹配。

| 总线协议 | 差分阻抗标准 | 单端阻抗参考 | 公差要求 | 传输介质 | 核心注意事项 |

|---|---|---|---|---|---|

| 10/100Mbps 以太网(百兆) | 100Ω±15% | 50Ω±15% | ±15% | 双绞线、PCB 走线 | 速率低,阻抗要求宽松,重点控制线对串扰 |

| 1000Mbps 以太网(千兆) | 100Ω±10% | 50Ω±10% | ±10% | CAT5e/CAT6 网线、PCB 差分走线 | 4 对差分需等长(组内误差 < 20mil),参考平面完整 |

| 10Gbps 以太网(万兆) | 100Ω±8% | 50Ω±8% | ±8% | CAT6A/CAT7 网线、PCB 微带线 / 带状线 | 需低损耗板材(如罗杰斯 4350),减少高频衰减 |

| 车载以太网(100BASE-T1) | 100Ω±10% | 50Ω±10% | ±10% | 车载屏蔽双绞线 | 抗电磁干扰强,适配汽车恶劣环境 |

三、 内存总线(DDR 系列,单端 + 差分混合)

内存总线是高速并行总线,地址 / 数据信号为单端,时钟 / 差分控制信号为差分,阻抗规范极其严格。

| 总线协议 | 单端阻抗标准 | 差分阻抗标准 | 公差要求 | 核心注意事项 |

|---|---|---|---|---|

| DDR2 | 50Ω±15% | 100Ω±15% | ±15% | 单端信号需等长,差分时钟需与数据信号长度匹配 |

| DDR3/LPDDR3 | 50Ω±10% | 100Ω±10% | ±10% | 数据信号组内等长误差 < 5mil,参考平面禁止分割 |

| DDR4/LPDDR4 | 50Ω±8% | 100Ω±8% | ±8% | 支持 ODT(片上终端匹配),阻抗匹配可通过寄存器配置 |

| DDR5/LPDDR5 | 40Ω±5% | 80Ω±5% | ±5% | 速率高达 6400Mbps,需超低寄生参数,板材损耗控制在 0.5dB/inch@10GHz |

四、 射频 / 无线相关总线

射频信号以单端阻抗为主,核心是 50Ω(行业通用匹配阻抗),部分射频差分信号参考以下规范。

| 总线协议 | 单端阻抗标准 | 差分阻抗标准 | 公差要求 | 典型应用 | |

|---|---|---|---|---|---|

| WiFi 6/6E(2.4G/5G) | 50Ω±5% | --- | ±5% | 无线网卡、路由器 | 射频走线需短直,避免过孔,参考平面连续 |

| 蓝牙 5.3/5.4 | 50Ω±5% | --- | ±5% | 蓝牙模组、无线耳机 | 阻抗不匹配会导致传输距离缩短 |

| 5G 射频前端 | 50Ω±3% | --- | ±3% | 手机、基站 | 需用射频专用板材(如罗杰斯 RO4003),阻抗公差极严 |

五、 总线阻抗规范的核心设计原则

- 参考平面连续:阻抗计算的前提是信号有稳定的地 / 电源参考平面,禁止在阻抗控制走线下方分割参考层(否则阻抗会突变)。

- 公差与速率正相关:速率越高,阻抗公差要求越严(如 PCIe Gen5 公差 ±5%,DDR2 公差 ±15%)。

- 差分线等长等距:差分阻抗的稳定性依赖 "线宽一致、间距一致、长度一致",差分对内等长误差需 < 5mil(高速信号)。

- 板材影响不可忽视:高频信号(如 PCIe Gen5、DDR5)需选择低介电常数(εr)、低损耗(tanδ)的板材,否则阻抗会随频率漂移。

总结

总线协议的阻抗规范是硬性标准 ,设计时需先查阅对应协议的官方手册(如 USB-IF、HDMI Forum、JEDEC),再结合 PCB 厂的工艺能力确定线宽 / 线距。实际生产中,建议要求 PCB 厂提供阻抗测试报告(如 TDR 测试),确保批量生产的阻抗一致性。

常见的高速串行总线有哪些?

高速串行总线是现代电子系统中高速数据传输的核心 ,相比并行总线具有布线简单、抗干扰强、速率高、功耗低 等优势,广泛应用于消费电子、工业控制、通信设备等领域。以下是按应用场景分类的常见高速串行总线,包含核心参数与典型用途:

一、 板内 / 板间高速互联总线

这类总线主要用于芯片与芯片、板卡与板卡 之间的短距离高速传输,速率通常在 Gbps 级。

| 总线名称 | 核心参数 | 典型应用 | 关键特点 |

|---|---|---|---|

| PCIe(Peripheral Component Interconnect Express) | - 主流版本:Gen1~Gen6- 单通道速率:2.5Gbps(Gen1)~64Gbps(Gen6)- 差分阻抗:85Ω(Gen1-4)/80Ω(Gen5-6)- 拓扑:点对点 | 显卡、NVMe 固态硬盘、服务器扩展卡、FPGA 板卡 | 串行替代传统并行 PCI,支持热插拔、多通道绑定,是当前板卡互联的事实标准 |

| SATA(Serial ATA) | - 主流版本:SATA 3.0- 速率:6Gbps- 差分阻抗:100Ω- 拓扑:点对点 | 机械硬盘(HDD)、固态硬盘(SSD)、光驱 | 替代并行 ATA,布线简单,支持热插拔,民用级存储的主流选择 |

| SAS(Serial Attached SCSI) | - 速率:12Gbps/24Gbps- 差分阻抗:100Ω- 拓扑:点对多 | 企业级存储阵列、服务器硬盘 | 兼容 SATA,可靠性更高,支持多设备级联 |

| I2C/SMBus | - 速率:100Kbps(标准)~3.4Mbps(高速)- 拓扑:多主多从 | 芯片配置、传感器通信、电源管理 | 双线制(SDA/SCL),低速但布线极简,适合板内低速控制 |

| SPI(Serial Peripheral Interface) | - 速率:几 Mbps~ 上百 Mbps- 拓扑:一主多从 | Flash 存储、ADC/DAC、射频模组 | 四线制(CLK/MOSI/MISO/CS),全双工,时序灵活 |

二、 外部设备高速互联总线

用于主机与外部设备的高速连接,兼顾速率与兼容性,是消费电子的核心接口总线。

| 总线名称 | 核心参数 | 典型应用 | 关键特点 |

|---|---|---|---|

| USB(Universal Serial Bus) | - 主流版本:USB 2.0/3.2/4- 速率:480Mbps(2.0)~40Gbps(USB4 Gen3)- 差分阻抗:90Ω- 拓扑:主从结构 | U 盘、移动硬盘、键鼠、手机充电 / 传输、USB-C 显示器 | 即插即用,支持供电 + 数据传输,USB4 兼容雷电 3/4 |

| Thunderbolt(雷电) | - 主流版本:雷电 3/4- 速率:40Gbps- 差分阻抗:90Ω- 拓扑:点对点 | 外接显卡坞、高速存储、4K/8K 显示器 | 基于 PCIe 和 DisplayPort 协议,支持多协议复用,供电能力强(最高 100W) |

| DisplayPort(DP) | - 主流版本:DP 1.4/2.0- 速率:32.4Gbps(1.4)~80Gbps(2.0)- 差分阻抗:100Ω- 拓扑:点对点 | 电竞显示器、笔记本投屏、VR 设备 | 支持高分辨率 + 高刷新率(如 8K@60Hz),兼容 USB-C |

| HDMI(High-Definition Multimedia Interface) | - 主流版本:HDMI 2.0/2.1- 速率:18Gbps(2.0)~48Gbps(2.1)- 差分阻抗:100Ω- 拓扑:点对点 | 电视、机顶盒、游戏机、投影仪 | 音视频同步传输,支持 HDR、8K@120Hz,民用显示领域普及度最高 |

三、 通信与网络高速串行总线

用于设备间远距离高速数据传输,涵盖有线网络、光纤通信、车载通信等场景。

| 总线名称 | 核心参数 | 典型应用 | 关键特点 |

|---|---|---|---|

| 以太网(Ethernet) | - 主流版本:千兆(1G)/ 万兆(10G)/25G/100G- 差分阻抗:100Ω(双绞线)/50Ω(光纤)- 拓扑:星型 / 环型 | 局域网、互联网、工业以太网、数据中心 | 通用性最强的网络总线,支持多种传输介质(双绞线 / 光纤 / 同轴) |

| LVDS(Low-Voltage Differential Signaling) | - 速率:几百 Mbps~3Gbps- 差分阻抗:100Ω- 拓扑:点对点 | 工业显示屏、摄像头模组、高速数据采集卡 | 低电压(≤1.2V)、低功耗、抗干扰强,适合长距离板间传输 |

| 100BASE-T1/1000BASE-T1(车载以太网) | - 速率:100Mbps/1Gbps- 差分阻抗:100Ω- 拓扑:星型 | 汽车中控、ADAS 系统、车载传感器 | 专为汽车恶劣环境设计,抗电磁干扰,布线成本低 |

| 光纤通道(FC, Fibre Channel) | - 速率:8Gbps~128Gbps- 阻抗:50Ω(光模块)- 拓扑:点对点 / 环型 | 数据中心存储、服务器集群 | 低延迟、高可靠性,专为海量数据传输设计 |

四、 高速串行总线的核心优势(对比并行总线)

- 布线简化:串行仅需 1~2 对差分线,并行需数十根数据线(如 DDR5 并行总线需上百根线),大幅降低 PCB 设计难度。

- 抗干扰强:差分传输对共模噪声抑制能力强,适合高速信号长距离传输。

- 速率提升潜力大:串行总线可通过提升时钟频率、采用更高级的调制方式(如 PAM4)突破速率瓶颈,而并行总线受限于信号同步(skew)问题,速率难以大幅提升。

- 功耗更低:低电压差分信号(如 LVDS)的功耗远低于并行总线的高电平信号。

总结

高速串行总线的选择需结合传输速率、距离、成本、兼容性四大要素:

- 板内短距离高速互联:优先选 PCIe;

- 外部设备连接:优先选 USB4 / 雷电;

- 音视频传输:优先选 HDMI 2.1/DP 2.0;

- 网络通信:优先选 千兆 / 万兆以太网;

- 工业控制低速互联:优先选 I2C/SPI/LVDS。