基本信息

测试平台:PCIE406硬件平台

FPGA芯片:xcku060-ffva1516-2-i

Vivado版本:vivado2018.3

硬件平台PCIE406,如上所示。解决ADC测试中对采样信号不准的问题时,对时钟采样的延时和信号的延迟都进行了一定程度的微调,下面进行一些总结。是关于对MMCM的相位微调。

MMCM相位延迟控制

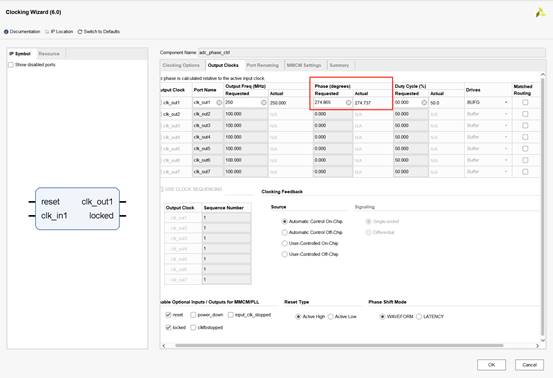

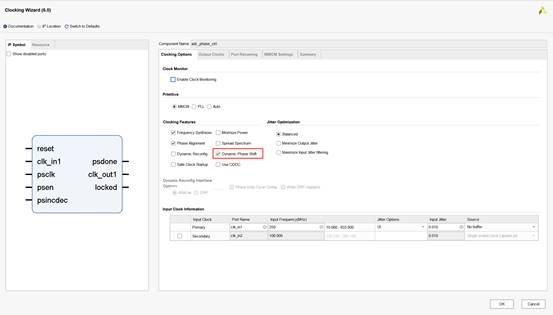

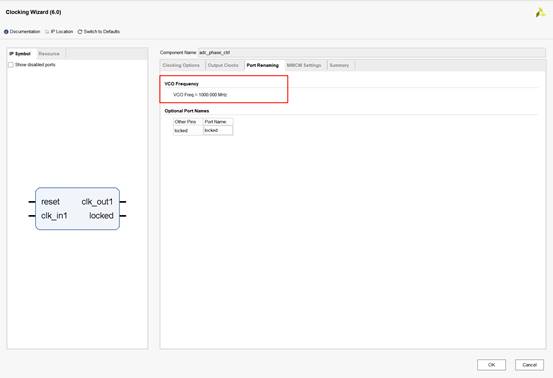

IPCORE配置

- 需要开启动态相位调整Dynamic Phase Shift

- 基础思路先手动调整相位偏移,而后,到达合适位置时,记录下当前的相位值,作为相位的初始值,重新生成IPCORE,这样就不需要每次都手动进行相位偏移了。

- 开启Use Fine Ps可以进行更细微的精度调节。

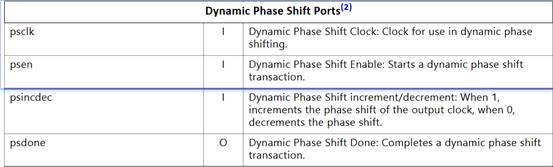

控制信号说明

| 端口名 | 功能描述 |

|---|---|

| psclk | 动态相位偏移时钟:为相位偏移操作提供时钟信号。 |

| psen | 动态相位偏移使能:启动一次相位偏移操作。 |

| psincdec | 相位偏移增减控制:- 置 1 时,增加输出时钟的相位偏移;即向正向偏移- 置0时,减少输出时钟的相位偏移。即向反向偏移 |

| psd done | 动态相位偏移完成:表示一次相位偏移操作已结束。 |

单位精度说明

在ug472之中,可以看到,精细控制微调模式下,相位的分辨率如下:

当前系统的FCO为1000MHZ,则每次时钟的偏移约为(1/(56*1000ps))=18ps下面我们通过仿真来验证下。

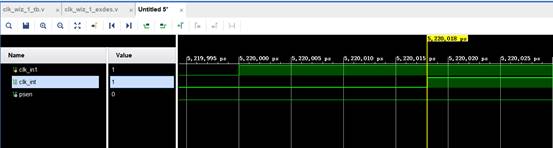

如下,延时调整之前,输入时钟上升沿和输出时钟上升沿差为0ps

进行了一次调整,可以证明相位差值为5220018-5220000 = 18ps

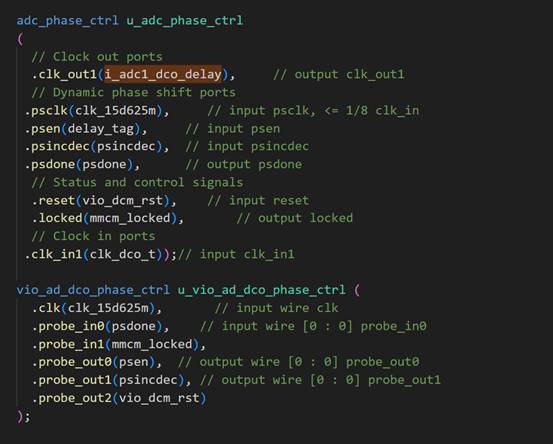

控制逻辑

测试阶段控制逻辑通过VIO进行微调。psen每变化1次,时钟偏移为18ps,相位偏移为18ps/1000ps *360 = 6.48度。所以根据psen的变化次数,确定相位偏移的角度。最后在将此角度初始化到MMCM之中,即可完成对初始化相位的调整。

在调整时,可以记录信号开始变好是的psen计数,如计数为10,而后一直增大psen,假设psen = 50时,信号变差。则我们取得psen的值为(10+50)/2 = 30。应当设置的初始化相位为30*6.48 = 194.4。

如下图,最终修改初始化相位。