前言

Xilinx 统一安装程序(Unified Installer) 是进行 FPGA 与异构计算平台开发的重要基础工具,集成了 Vivado 、Vitis 以及相关文档与设备支持组件。正确完成安装是后续进行硬件设计、软件开发与系统验证的前提。

本文以 Xilinx 统一安装程序 2020.1 为例,结合实际安装过程,对 安装步骤 进行逐步说明,并对 关键选项 的含义进行必要解释。同时,针对安装过程中可能出现的 常见错误(如归档文件无法打开、安装中断等问题),给出原因分析与解决建议,帮助用户快速定位并解决问题。

需要注意的是,安装文件的完整性 与安装环境的稳定性 对安装成功率影响较大。若安装过程中出现异常,建议优先检查 安装包是否完整 、磁盘空间是否充足 以及系统权限与安全软件设置是否合理 。希望本文能够为初次接触 Xilinx 工具 或在安装过程中遇到问题的用户提供参考和帮助。

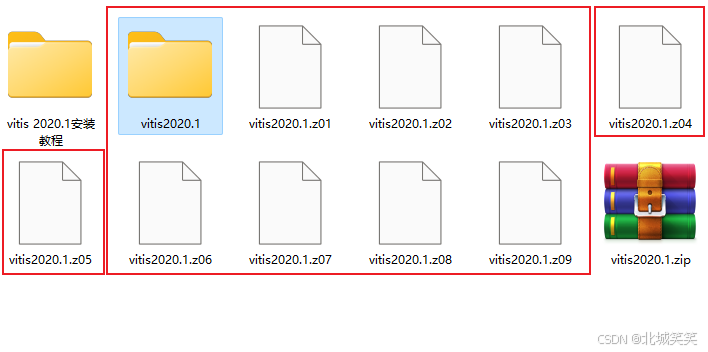

首先准备好安装文件

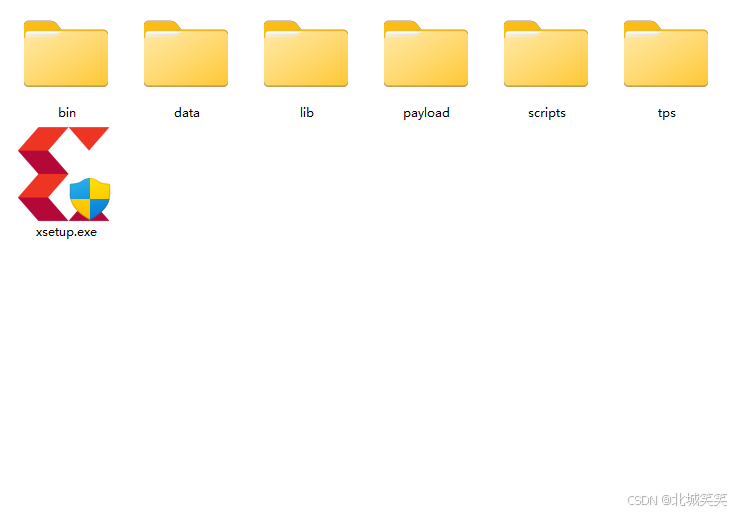

打开 vitis 2020.1

点击安装 ⬇

系统需要响应一会,稍等片刻

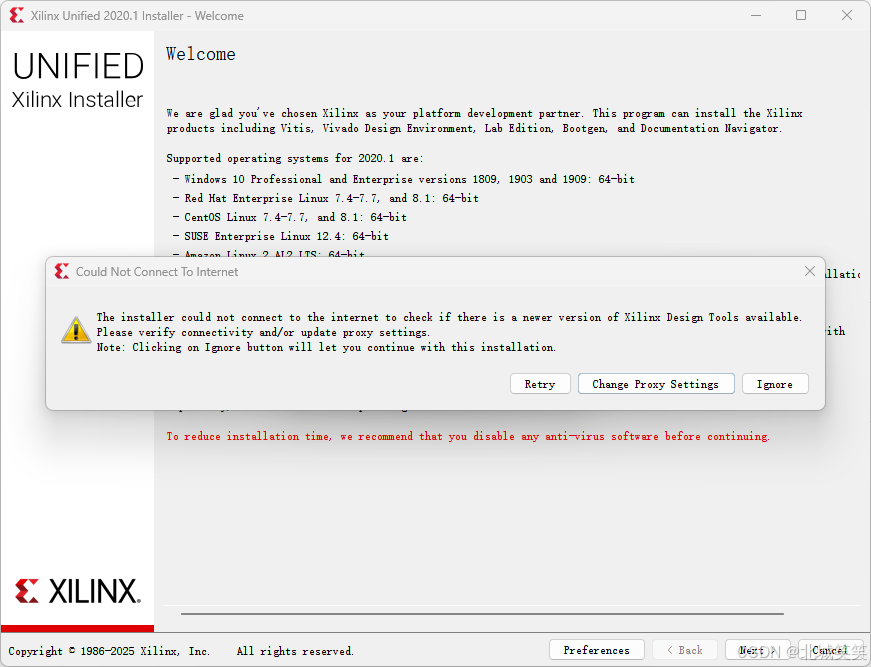

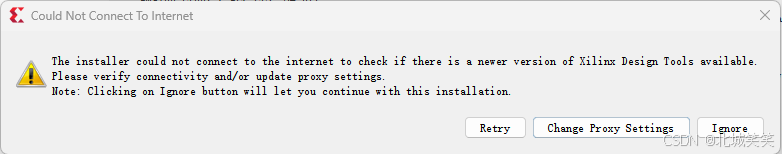

提示:

翻译:

无法连接到互联网

安装程序无法连接到互联网,以检查是否有更新版本的 Xilinx 设计工具可用。请验证网络连接性和 / 或更新代理设置。

注意:单击 "忽略" 按钮将使您可以继续此安装。

重试\] \[更改代理设置\] \[忽略

选择,Ignore(忽略)

翻译:

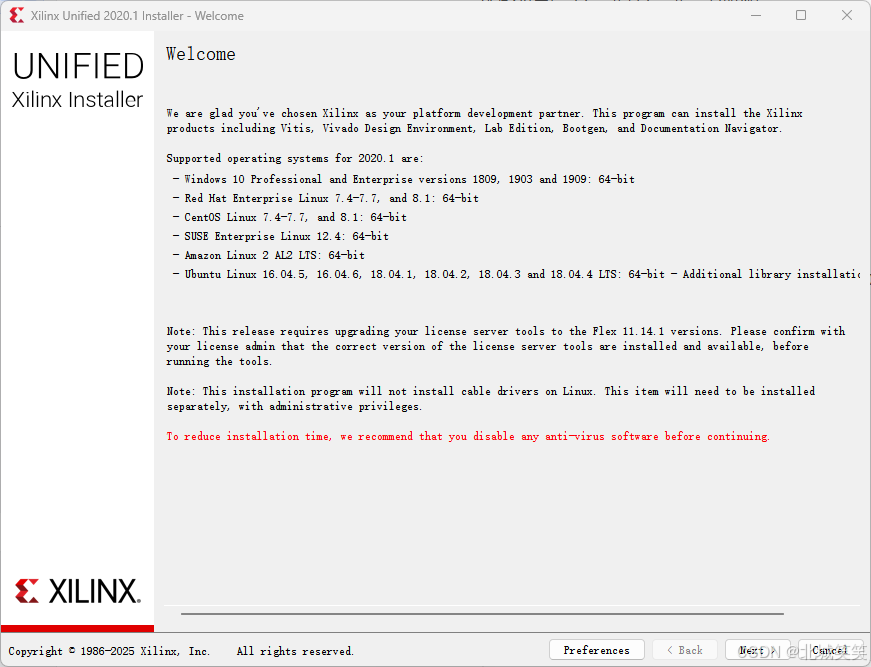

Xilinx 统一安装程序 2020.1 - 欢迎

欢迎 统一 Xilinx 安装程序我们很高兴您选择 Xilinx 作为您的平台开发合作伙伴。该程序可安装 Xilinx 产品,包括 Vitis、Vivado 设计环境、实验室版、Bootgen 和文档导航器。2020.1 支持的操作系统有:

- Windows 10 专业版和企业版 1809、1903 和 1909:64 位

- Red Hat Enterprise Linux 7.4-7.7 和 8.1:64 位

- CentOS Linux 7.4-7.7 和 8.1:64 位

- SUSE Enterprise Linux 12.4:64 位

- Amazon Linux 2 AL2 LTS:64 位

- Ubuntu Linux 16.04.5、16.04.6、18.04.1、18.04.2、18.04.3 和 18.04.4 LTS:64 位 - 需额外安装库

注意:此版本需要将您的许可证服务器工具升级到 Flex 11.14.1 版本。在运行工具之前,请与您的许可证管理员确认已安装并可使用正确版本的许可证服务器工具。注意:此安装程序不会在 Linux 上安装线缆驱动程序。此项需要单独安装,并具备管理员权限。

为减少安装时间,我们建议您在继续之前禁用任何防病毒软件。

© 1986-2025 Xilinx, Inc. 保留所有权利。[偏好设置] < [上一步] [下一步 > ] [取消]

选择,Next(下一步)

翻译:

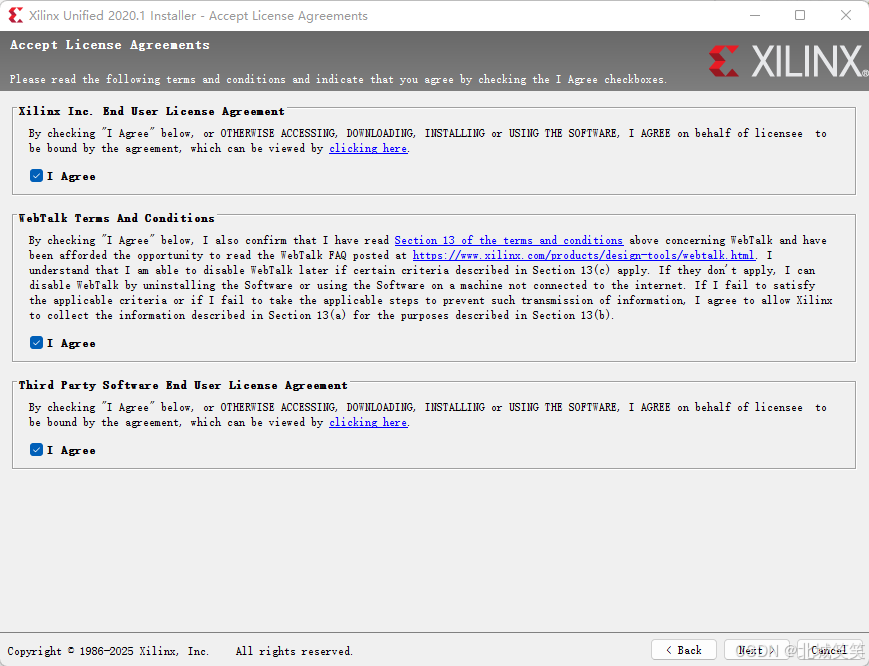

Xilinx 统一安装程序 2020.1 - 接受许可协议

接受许可协议请阅读以下条款和条件,并通过勾选 "I Agree" 复选框来表明您同意。

Xilinx 公司 最终用户许可协议

通过勾选下方的 "I Agree",或通过其他方式访问、下载、安装或使用本软件,我代表被许可方同意受本协议约束,您可以通过点击此处查看本协议。

☑ 我同意

WebTalk 条款和条件

通过勾选下方的 "I Agree",我同时确认我已阅读上述条款和条件中关于 WebTalk 的第 13 节,并且有机会阅读发布在https://www.xilinx.com/products/design-tools/webtalk.html的 WebTalk 常见问题。我理解,如果第 13 (c) 节中描述的某些条件适用,我之后可以禁用 WebTalk;如果不适用,我可以通过卸载软件或将软件用于未连接互联网的机器来禁用 WebTalk。如果我未能满足适用条件,或未能采取适当步骤防止此类信息传输,我同意允许 Xilinx 收集第 13 (a) 节中描述的信息,用于第 13 (b) 节中描述的目的。

☑ 我同意

第三方软件最终用户许可协议

通过勾选下方的 "I Agree",或通过其他方式访问、下载、安装或使用本软件,我代表被许可方同意受本协议约束,您可以通过点击此处查看本协议。

☑ 我同意

© 1986-2025 Xilinx, Inc. 保留所有权利。<上一步 下一步> 取消

全部选择同意,Next(下一步)

翻译:

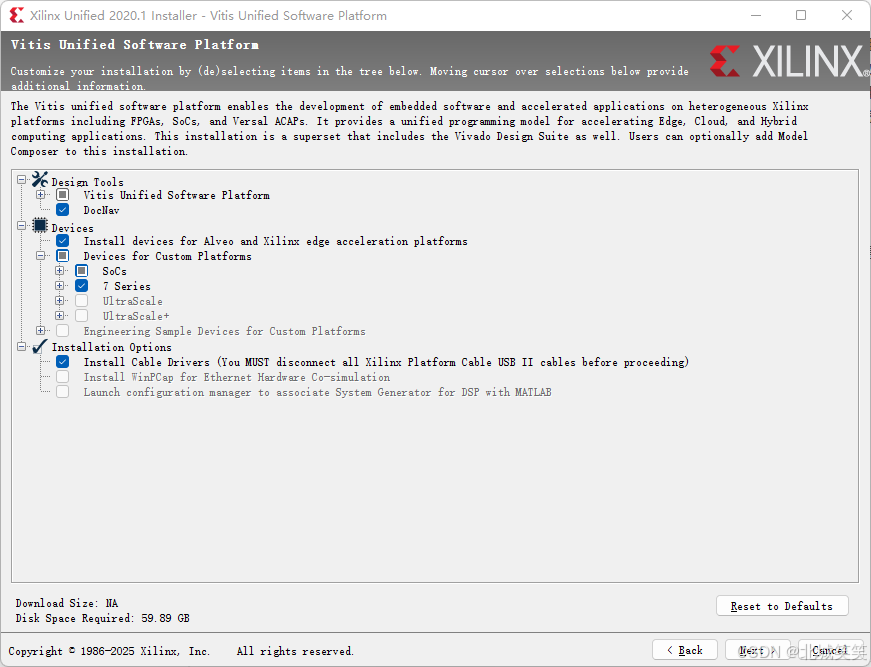

Xilinx 统一安装程序 2020.1 - Vitis 统一软件平台

Vitis 统一软件平台通过选择下方树状结构中的项目来自定义您的安装。将光标移到下方选项上可查看更多信息。Vitis 统一软件平台支持在异构 Xilinx 平台(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件与加速应用,为边缘、云及混合计算场景提供统一编程模型。此安装包是包含 Vivado 设计套件的超集,用户还可选择向本次安装中添加 Model Composer。

设计工具

- ☑ Vitis 统一软件平台

- ☑ DocNav

设备

(为 Alveo 和 Xilinx 边缘加速平台安装设备)

- ☑ 自定义平台设备

- □ SoC

- ☑ 7 系列

- □ UltraScale

- □ UltraScale+

- □ 自定义平台的工程样例设备

安装选项

- ☑ 安装线缆驱动程序(继续操作前必须断开所有 Xilinx Platform Cable USB II 线缆)

- ☑ 安装用于以太网硬件协同仿真的 WinCap

- □ 启动配置管理器,将 DSP 系统生成器与 MATLAB 关联

其他信息

- 下载大小:无可用信息(NA)

- 所需磁盘空间:59.89 GB

© 1986-2025 Xilinx, Inc. 保留所有权利。<上一步 下一步> 取消

默认,Next(下一步)

翻译:

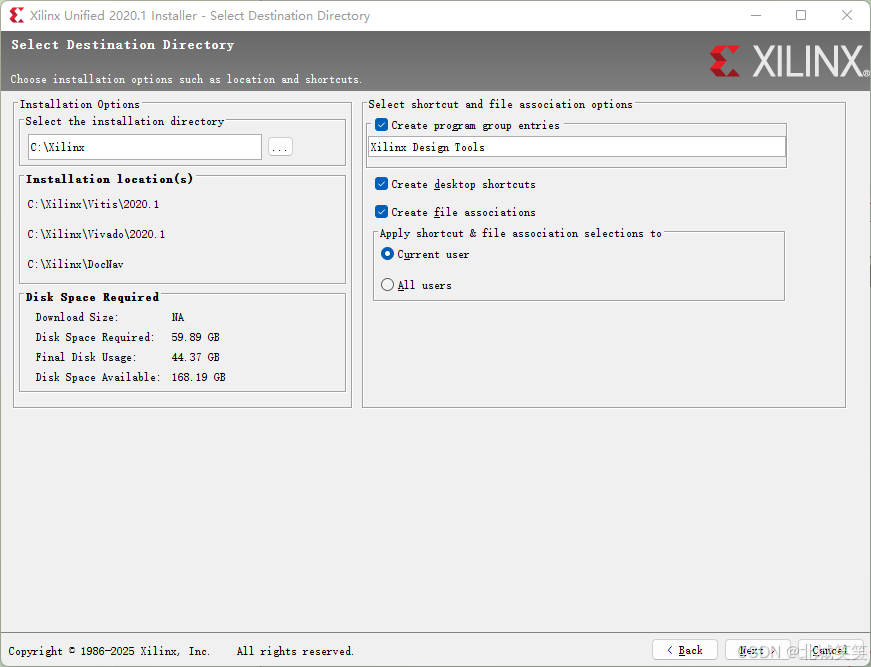

Xilinx 统一安装程序 2020.1 - 选择目标目录

选择安装选项(如位置和快捷方式)。

安装选项

- 选择安装目录C:\Xilinx

安装位置

- C:\Xilinx\Vitis\2020.1

- C:\Xilinx\Vivado\2020.1

- C:\Xilinx\DocNav

所需磁盘空间

- 下载大小:无可用信息(NA)

- 所需磁盘空间:59.89 GB

- 最终磁盘占用:44.37 GB

- 可用磁盘空间:168.19 GB

选择快捷方式和文件关联选项

- ☑ 创建程序组条目名称:Xilinx 设计工具

- ☑ 创建桌面快捷方式

- ☑ 创建文件关联

快捷方式与文件关联的应用范围:

- ◉ 当前用户

- ○ 所有用户

© 1986-2025 Xilinx, Inc. 保留所有权利。<上一步 下一步> 取消

选择安装磁盘位置,Next(下一步)

翻译:

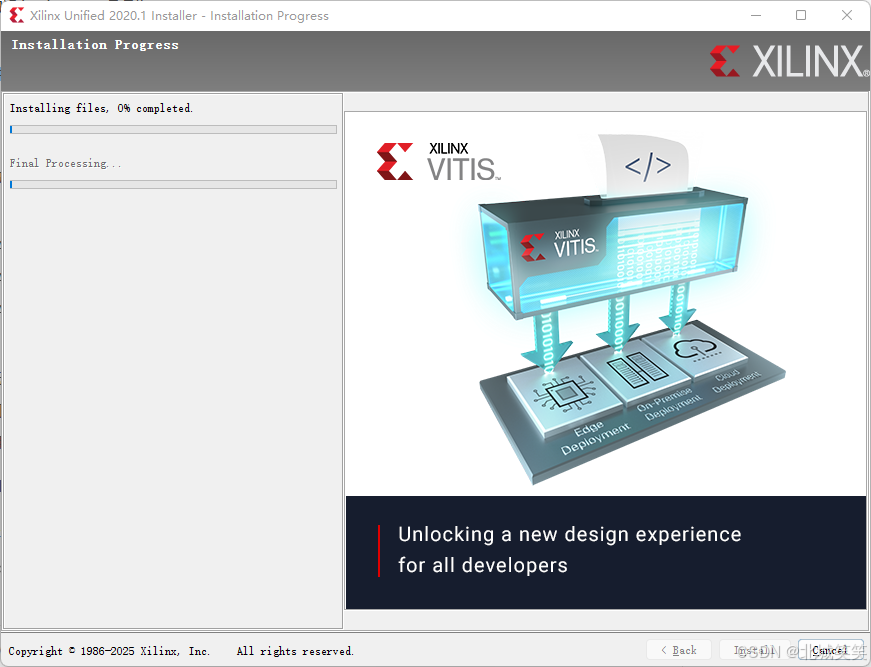

Xilinx 统一安装程序 2020.1 - 安装进度

安装进度

左侧进度区域:

- 正在安装文件,完成度 0%

- 最终处理中...

右侧展示区域:(包含 Xilinx Vitis 标识,以及边缘部署、本地部署、云部署的场景图示)宣传语:为所有开发者解锁全新的设计体验

© 1986-2025 Xilinx, Inc. 保留所有权利。<[上一步] [安装] [取消]

正在安装中......

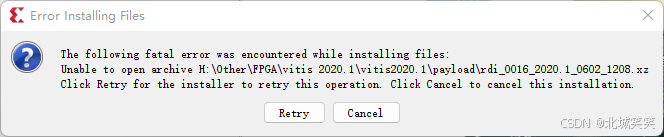

翻译:

文件安装错误

在安装文件时遇到以下致命错误:无法打开归档文件 R:\other\FPGA\vitis 2020.1\vitis2020.1\payload\vrdi_0016_2020.1_0602_1208.xz。

点击 "重试" 让安装程序重新尝试此操作。点击 "取消" 以取消本次安装。

重试\] \[取消

错误分析与解决建议

该错误是 Xilinx 工具安装过程中常见的 "归档文件无法打开" 问题,可能的原因及对应解决办法:

- 安装包文件损坏 :若安装包下载不完整或存在损坏,需重新下载官方完整的安装包;

- 磁盘问题 :检查 R 盘是否有足够剩余空间、磁盘是否存在坏道,可尝试更换安装路径到其他磁盘;

- 权限 / 路径问题 :确认当前用户对 R 盘目标路径有读写权限,且路径中避免包含中文和特殊字符(如空格外的符号);

- 软件拦截 :临时关闭杀毒软件或防火墙,避免其拦截安装程序对归档文件的访问。

我这里是安装文件的问题,有的文件会在迁移位置时损坏。请重新下载准备好安装文件,按照流程,重新安装操作,安装完成后,桌面会出现4个应用程序,表示安装成功。

更多操作

完整 FPGA 系列,请看

FPGA 专栏![]() https://blog.csdn.net/weixin_65793170/category_12665249.html

https://blog.csdn.net/weixin_65793170/category_12665249.html

文章目录,请看

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502

https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502