ARM Cortex-M 存储器映射

本文来自于我关于ARM Cortex-M 的存储器系统的系列文章。欢迎阅读、点评与交流~

1、ARM Cortex-M 的存储器系统特性

2、ARM Cortex-M 存储器映射

文章目录

- [ARM Cortex-M 存储器映射](#ARM Cortex-M 存储器映射)

-

- 一、概述

- 二、存储器映射整体布局

- 三、主要存储器区域详解

-

- [1. 代码区域 (0x0000 0000 - 0x1FFF FFFF) - 512MB](#1. 代码区域 (0x0000 0000 - 0x1FFF FFFF) - 512MB)

- [2. 片上SRAM区域 (0x2000 0000 - 0x3FFF FFFF) - 512MB](#2. 片上SRAM区域 (0x2000 0000 - 0x3FFF FFFF) - 512MB)

- [3. 片上外设区域 (0x4000 0000 - 0x5FFF FFFF) - 512MB](#3. 片上外设区域 (0x4000 0000 - 0x5FFF FFFF) - 512MB)

- [4. 外部RAM区域 (0x6000 0000 - 0x9FFF FFFF) - 1GB](#4. 外部RAM区域 (0x6000 0000 - 0x9FFF FFFF) - 1GB)

- [5. 外部设备区域 (0xA000 0000 - 0xDFFF FFFF) - 1GB](#5. 外部设备区域 (0xA000 0000 - 0xDFFF FFFF) - 1GB)

- [6. 私有外设总线 (0xE000 0000 - 0xE00F FFFF) - 1MB](#6. 私有外设总线 (0xE000 0000 - 0xE00F FFFF) - 1MB)

- 四、关键技术特性

-

- [1. 位带操作](#1. 位带操作)

- [2. 向量表重定位](#2. 向量表重定位)

- [3. 内存属性与访问权限](#3. 内存属性与访问权限)

- 五、Cortex-M系列差异

- 六、实际芯片实现示例(以STM32F4为例)

- 七、开发中的注意事项

- 八、总结

一、概述

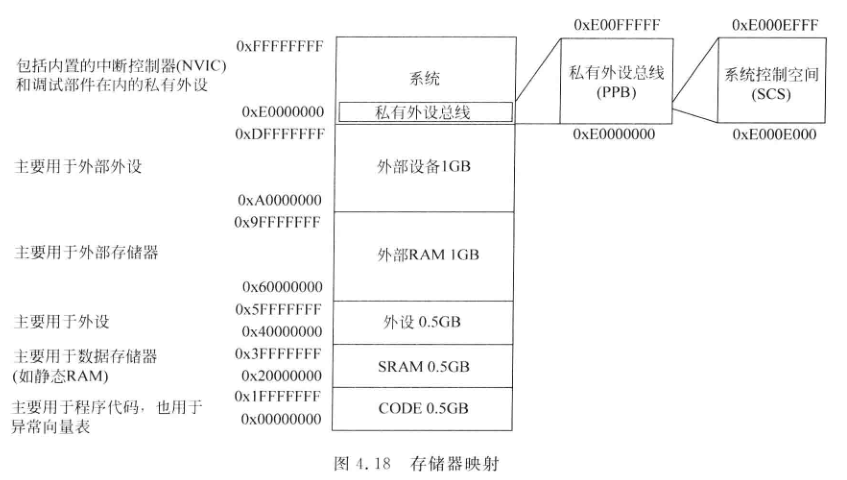

ARM Cortex-M处理器的存储器映射是一个统一编址的32位地址空间(4GB),这个空间被预定义为不同的功能区域,每个区域有特定的用途和访问特性。

二、存储器映射整体布局

0xFFFFFFFF ┌──────────────────────┐

│ 私有外设总线(PPB) │

0xE0100000 └──────────────────────┘

│ 保留区域 │

0xE0000000 └──────────────────────┘

│ 外部设备区域 │

0xA0000000 └──────────────────────┘

│ 外部RAM区域 │

0x60000000 └──────────────────────┘

│ 外部ROM/Flash区域 │

0x40000000 └──────────────────────┘

│ 片上外设区域 │

0x20000000 └──────────────────────┘

│ 片上SRAM区域 │

0x00000000 └──────────────────────┘

三、主要存储器区域详解

1. 代码区域 (0x0000 0000 - 0x1FFF FFFF) - 512MB

- 用途:存储程序代码、常量数据和中断向量表

- 访问:通过ICode和DCode总线访问,支持字节、半字、字访问

- 典型包含 :

- Flash存储器

- ROM

- 部分片上RAM(用于代码执行)

2. 片上SRAM区域 (0x2000 0000 - 0x3FFF FFFF) - 512MB

- 用途:数据存储(变量、堆栈、堆)

- 访问:通过系统总线访问

- 特点 :

- 支持位带操作(Bit-band)

- 通常分为多个SRAM块

3. 片上外设区域 (0x4000 0000 - 0x5FFF FFFF) - 512MB

- 用途:连接芯片上的所有外设

- 包含 :

- GPIO端口

- 定时器、串口、SPI、I2C等外设寄存器

- 也支持位带操作

4. 外部RAM区域 (0x6000 0000 - 0x9FFF FFFF) - 1GB

- 用途:连接片外SRAM、DRAM等

- 访问:通过FSMC(Flexible Static Memory Controller,灵活静态存储器控制器)或外部总线接口

5. 外部设备区域 (0xA000 0000 - 0xDFFF FFFF) - 1GB

- 用途:连接片外设备

- 特点:通常用于外部FPGA、CPLD或特殊外设

6. 私有外设总线 (0xE000 0000 - 0xE00F FFFF) - 1MB

-

核心重要性:包含Cortex-M内核的系统控制功能

PPB详细布局:

0xE00F FFFF ┌──────────────────────┐

│ ROM表 │

0xE00F F000 └──────────────────────┘

│ 保留 │

0xE004 2000 └──────────────────────┘

│ TPIU (跟踪单元) │

0xE004 0000 └──────────────────────┘

│ ETM (嵌入式跟踪) │

0xE004 1000 └──────────────────────┘

│ DWT (数据观察点) │

0xE000 1000 └──────────────────────┘

│ FPB (Flash补丁) │

0xE000 2000 └──────────────────────┘

│ NVIC (中断控制器) │

0xE000 E000 └──────────────────────┘

│ SCB (系统控制块) │

0xE000 E000 └──────────────────────┘

│ SysTick定时器 │

0xE000 E010 └──────────────────────┘

│ MPU (内存保护单元) │

0xE000 ED90 └──────────────────────┘

四、关键技术特性

1. 位带操作

-

目的:实现单个位的原子操作

-

地址映射:

- SRAM位带别名区:0x2200 0000 - 0x23FF FFFF

- 外设位带别名区:0x4200 0000 - 0x43FF FFFF

-

计算公式:

别名区地址 = 位带基址 + (字节偏移×32) + (位号×4)

2. 向量表重定位

- 初始位置:0x0000 0000(从Flash启动)

- 可重定位到 :

- 0x0000 0000(Flash)

- 0x2000 0000(RAM)

- 0x8000 0000(外部Flash)

- 通过VTOR寄存器(Vector Table Offset Register)设置

3. 内存属性与访问权限

- 不同区域有不同的访问属性:

- 可执行(X)、可读®、可写(W)

- 缓存(Cache)和缓冲(Buffer)属性

- 特权/非特权访问控制

五、Cortex-M系列差异

| 特性 | Cortex-M0/M0+ | Cortex-M3 | Cortex-M4/M7 |

|---|---|---|---|

| 位带操作 | 可选 | 支持 | 支持 |

| MPU | 可选 | 可选 | 标准(M7)或可选 |

| 地址空间 | 4GB | 4GB | 4GB(+可选40位) |

| 向量表重定位 | 支持 | 支持 | 支持 |

六、实际芯片实现示例(以STM32F4为例)

STM32F407 (Cortex-M4) 存储器映射:

0xFFFFFFFF ┌───────────────┐

│ PPB │

0xE0000000 └───────────────┘

│ 保留 │

0x50000000 └───────────────┘

│ FMC/FSMC │

0xA0000000 └───────────────┘

│ AHB1/2/3总线 │

0x40000000 └───────────────┘

│ CCM RAM │

0x10000000 └───────────────┘

│ SRAM2 │

0x2001C000 └───────────────┘

│ SRAM1 │

0x20000000 └───────────────┘

│ Flash │

0x08000000 └───────────────┘

│ 系统存储器 │

0x1FFF0000 └───────────────┘

│ 引导程序区 │

0x00000000 └───────────────┘七、开发中的注意事项

- 启动配置:通过BOOT引脚或选项字节选择启动区域

- 链接脚本:正确配置代码、数据、堆栈的内存区域

- 外设访问:使用CMSIS定义的外设寄存器结构体

- 对齐访问:确保数据按正确对齐方式访问

- 内存保护:合理配置MPU保护关键区域

八、总结

Cortex-M的存储器映射设计提供了:

- 统一的地址空间,简化编程模型

- 固定的区域划分,确保代码可移植性

- 灵活的重定位能力,适应不同应用需求

- 硬件加速特性(如位带),提高实时性

理解存储器映射对于:

- 优化内存使用

- 调试内存相关问题

- 设计高效的嵌入式系统

- 实现可靠的安全机制

都具有重要意义。在实际开发中,建议结合具体芯片的参考手册和CMSIS库来准确理解和使用存储器映射。