今天正式上板,成功点灯嘻嘻~

1.设计规划及波形绘制

1.1触摸按键原理

机械按键VS触摸按键:

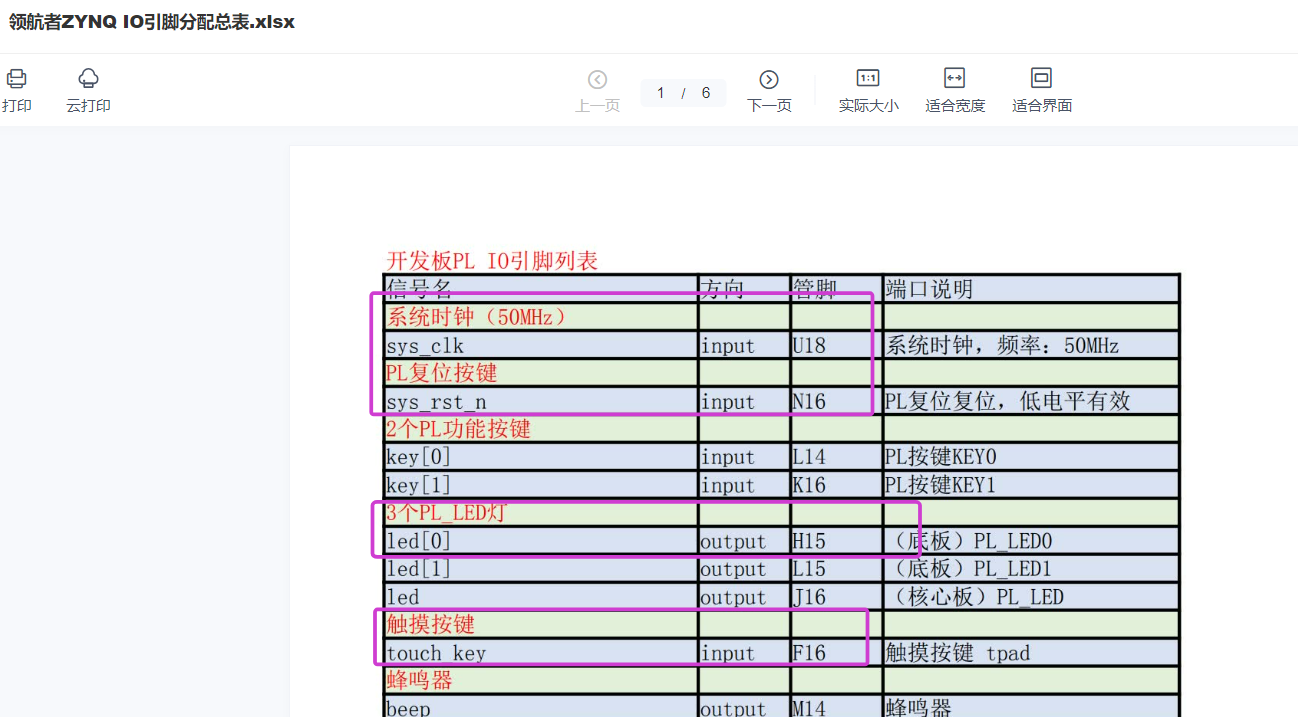

先从正点原子FPGA开发板来对比一下两种按键,粉色框是我们常使用的机械按键,而红色框就是触摸按键。

其实生活中触摸按键也很常见,以下几种都是触摸按键。

写verilog时,机械按键才需要消抖,触摸按键不需要消抖!

1.2波形绘制及实验目标

实验目标:按下触摸按键一次,LED灯点亮,再按下触摸按键,LED熄灭。

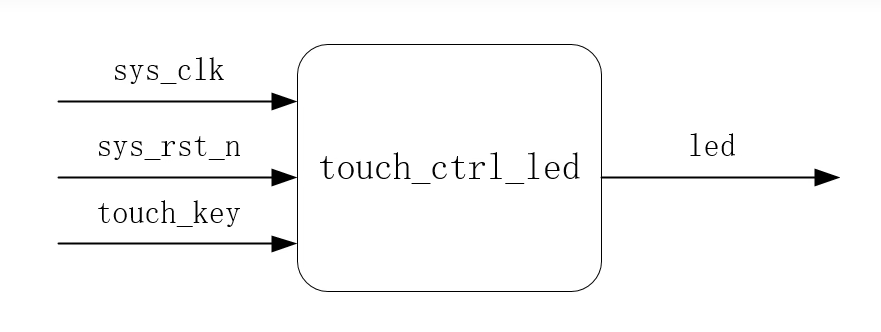

**模块框图:**三输入一输出。

波形绘制:

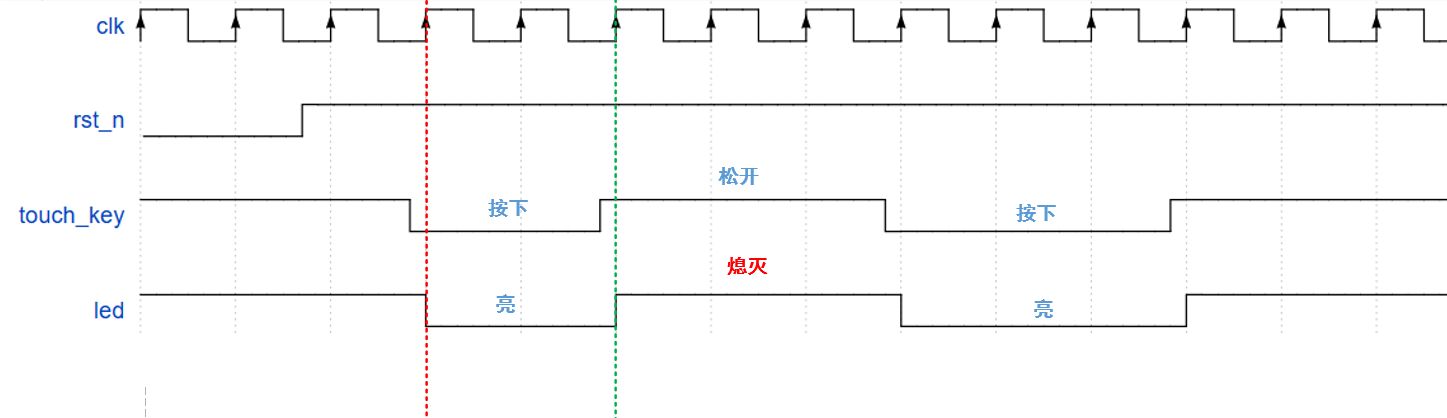

首先:按下触摸按键(touch_key信号)为低电平,LED灯低电平亮。

(1)如果直接只有三个输入,一个输出。

当检测到touch_key为低电平且时钟上升沿时LED点亮(红色线),当检测到touch_key为低电平且时钟上升沿时LED熄灭(绿色线)。

此时的led输出波形如下图所示,这种情况下led:亮------熄灭------亮。换言之,这种设计需要一直按下才能使得led一直亮。

与我们的目标不符合。

(错误波形)

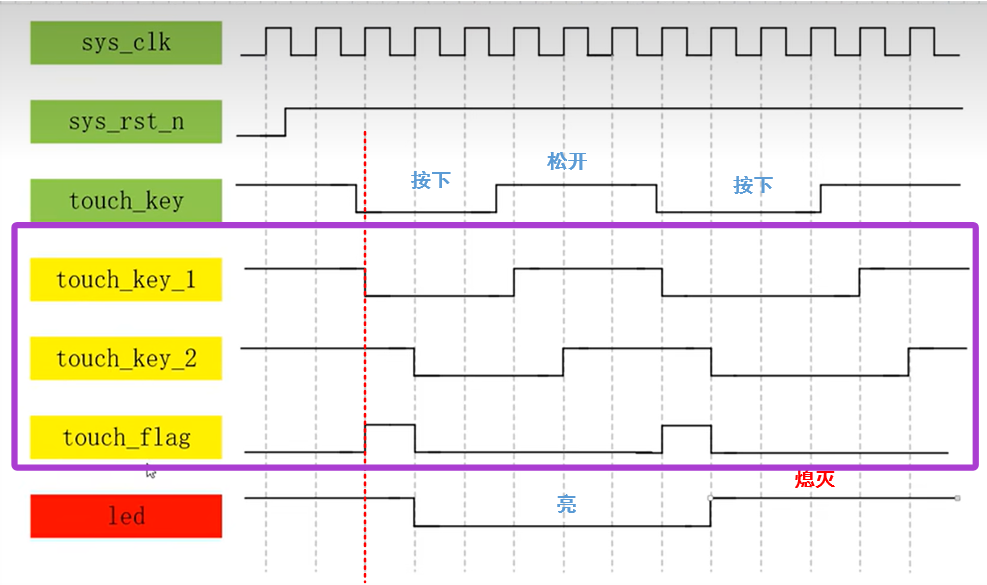

(2)使用两级寄存器同步和标志信号实现下降沿检测。

为了实现目标,可以当检测到touch_key的下降沿时led点亮,下一次检测到touch_key的下降沿时在熄灭(即取反操作)。

那么如何检测下降沿?(注意always块中一般写clk和rst信号的沿检测,最好不写其他信号)

使用两级寄存器同步:

touch_key_1实现第一级同步,使得touch_key下降沿与时钟对齐。

touch_key_2实现touch_key_1慢一拍的效果。

使用组合逻辑:当touch_key_1为低电平且touch_key_2为高电平时flag信号拉高

(看红色线,flag马上跳变了,而不是等下一个时钟上升沿才跳变,所以是组合逻辑。)

通过两级寄存器得到了一个单周期脉冲的flag信号,那么,时钟上升沿且检测到flag为1时,led取反即可,就可以实现目标了。

2.代码编写

module capacity_key

(

input sys_clk ,

input rst_n ,

input touch_key ,

output reg[0:0] led

);

reg [0:0] touch_key1;

reg [0:0] touch_key2;

wire [0:0] touch_flag;

//============================================两级寄存器提取按键下降沿(也可以消除亚稳态)==================================

//按键低电平按下

always @(posedge sys_clk or negedge rst_n) begin

if(!rst_n)begin

touch_key1 <= 1'b1;

touch_key2 <= 1'b1;

end

else begin

touch_key1 <= touch_key;

touch_key2 <= touch_key1;

end

end

assign touch_flag = touch_key1 == 1'b0 && touch_key2 == 1'b1;

//=======================================================================================================================

//led灯低电平点亮

always @(posedge sys_clk or negedge rst_n) begin

if(!rst_n)

led <= 1'b1;

else if (touch_flag == 1'b1)

led <= ~led;

else

led <= led;

end

endmodule记录错误点:

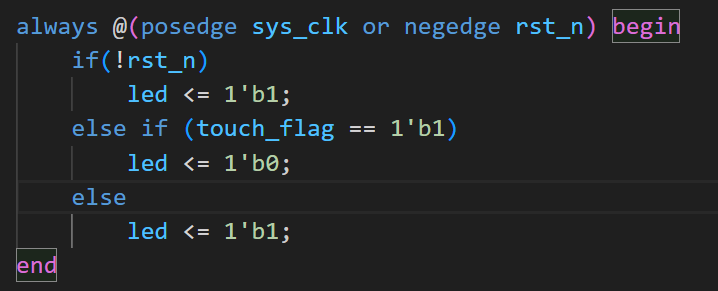

直接根据波形图给led赋值0和1会有问题,应该是flag高取反led,否则保持

(有误代码)

3 逻辑仿真及波形验证

这里不放波形图了,仿真出来的与原理的波形图一致。

4上板流程

这是第一次上板,记录一下流程吧~

(1)vivado中创建project

跟着网上FPGA视频即可。

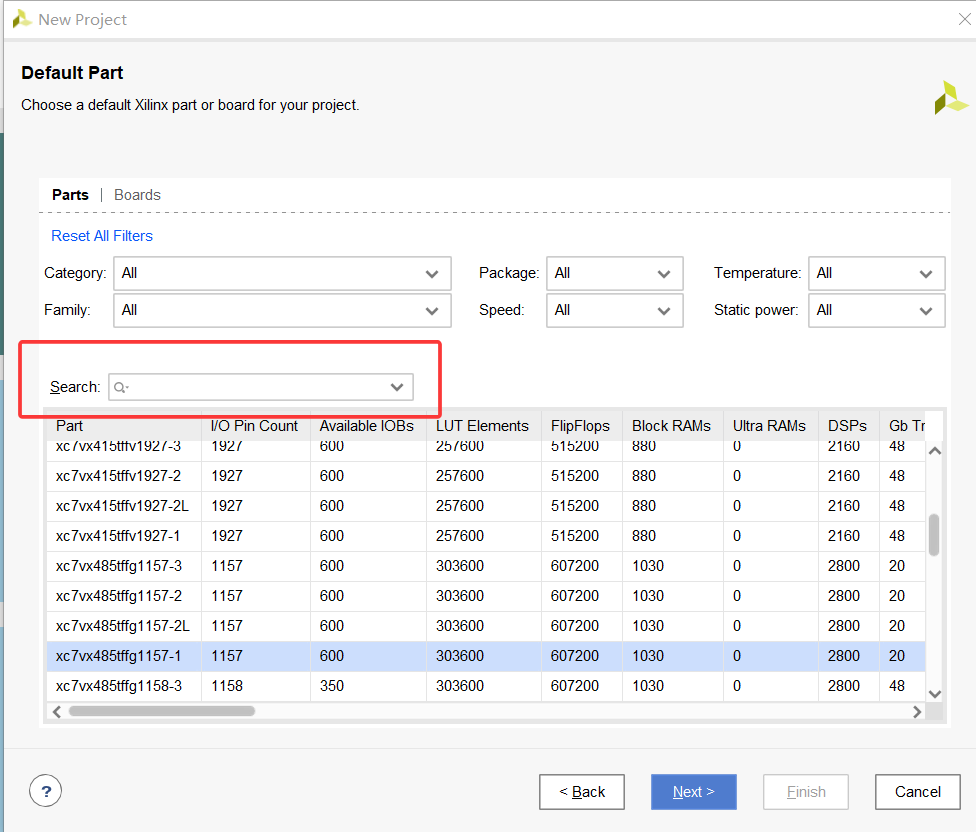

这里选芯片型号,看你用的是什么板子,一般在开发手册中找。

然后在vivado中搜索该型号。

(2)添加好设计文件和仿真文件(依旧网上FPGA视频)

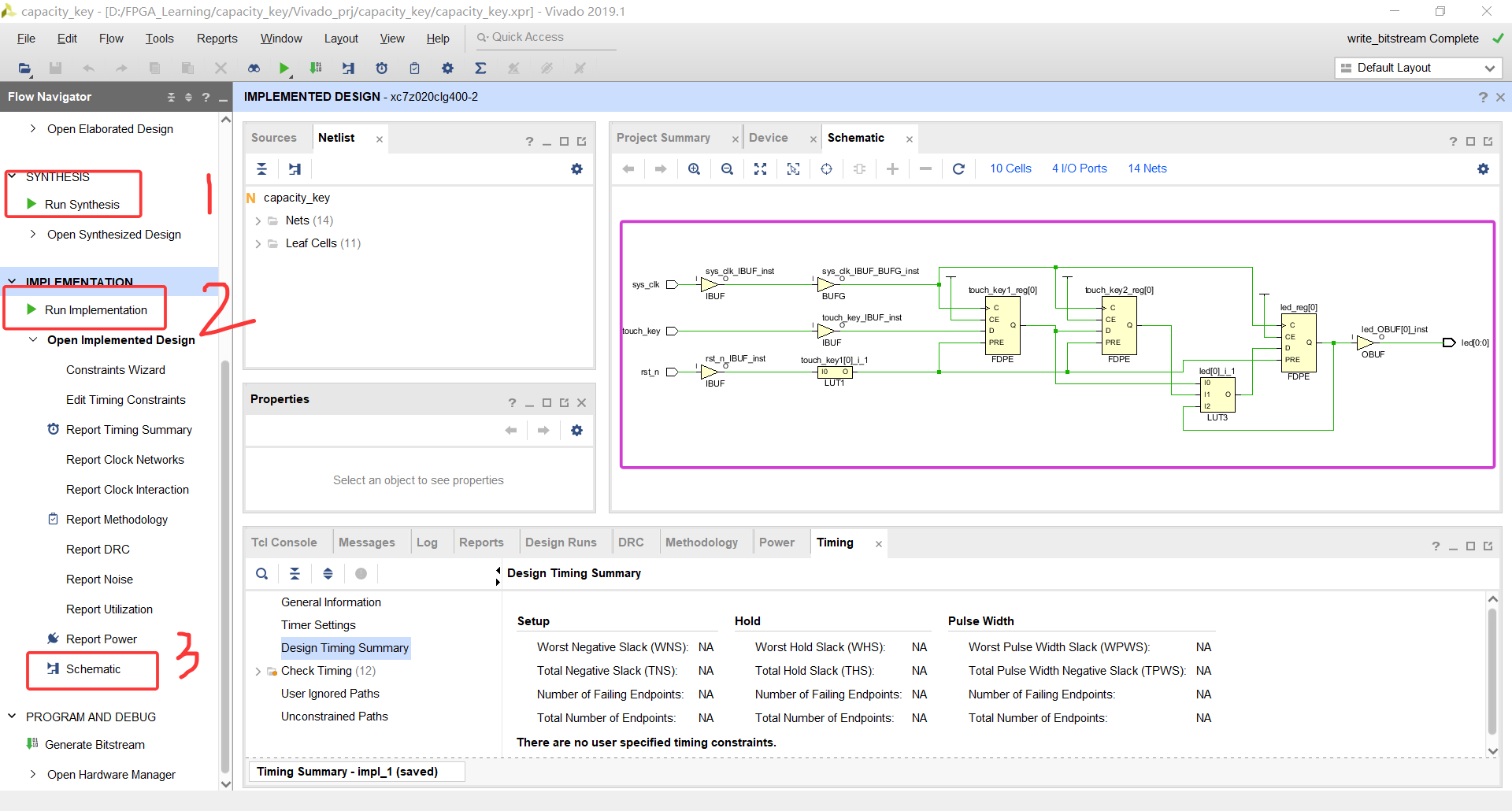

(3)综合

点击"schematic"可以看到代码综合后的电路。注意这一步一定要做!!!,才有后面"IO planning"那个选项。

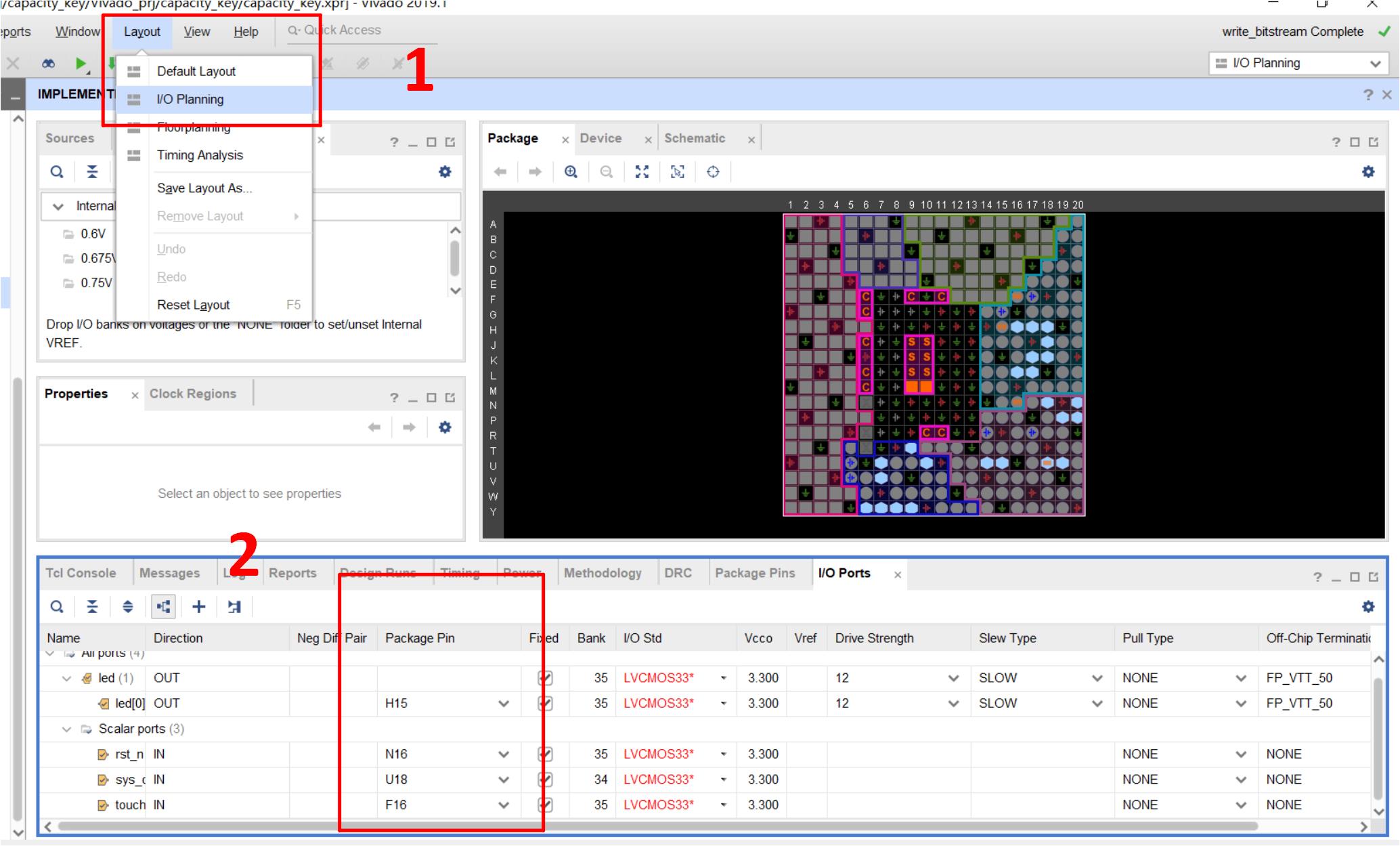

(4)绑定管脚

第二步也是要看手册,看对应你要使用的板上的资源对应什么管脚。

注意,当管脚名字看不见时,是界面缩小了,把鼠标放在红色框线上,显示出双向箭头,往右边拉就可以看到了。

从引脚分配表看是和上面第二步选的引脚是一致的。

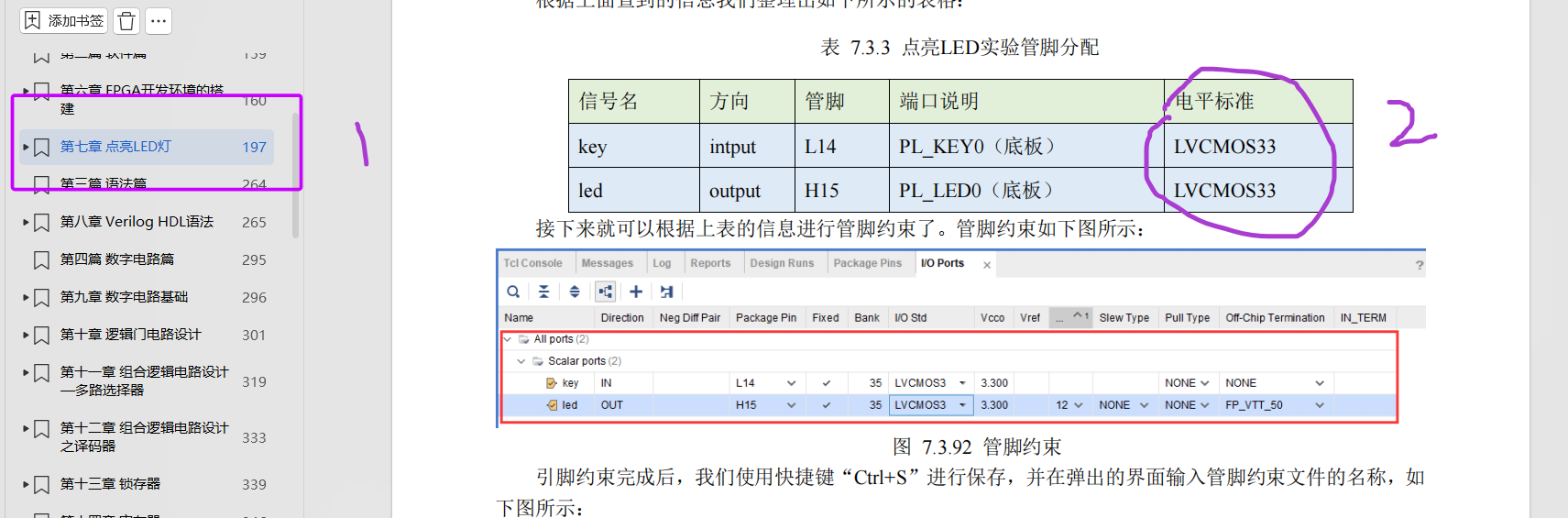

还有一个,端口电压,也是看手册,可以找类似的实验,里面一般会写清楚实验步骤。比如我这里找了个点亮led灯实验。

一般是33或者18,一开始我用了默认的18报错了,改成了33

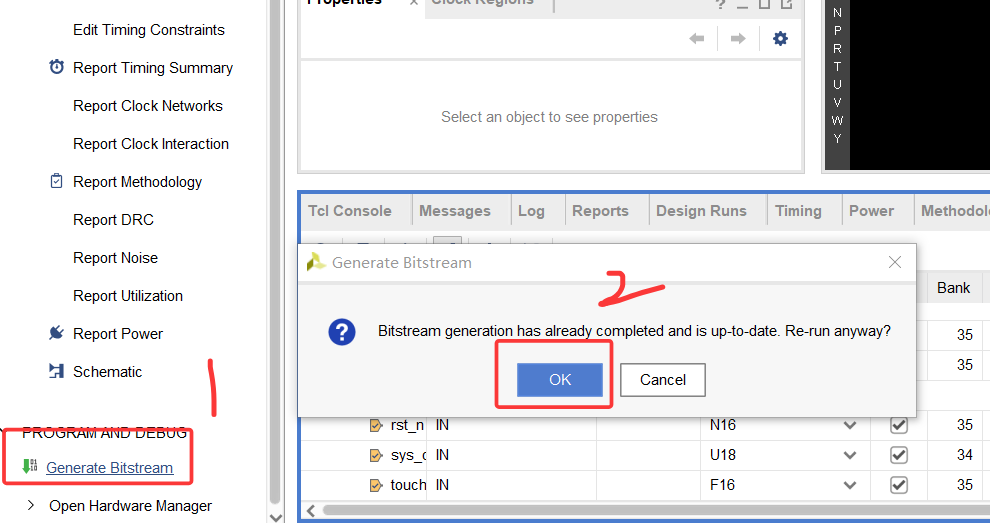

(5)生成比特流:

(本贴仅是个人经验,如有侵权请联系我~)