SPI总线

SPI(串行外设接口) (Serial Peripheral Interface) 是摩托罗拉开发的同步串行通信总线 ,主打高速、全双工数据传输,是微控制器与外设间的主流通信方案。

适用于高速、双向外设通信,如Flash 存储、SD 卡、LCD 显示屏、ADC/DAC、无线模块(蓝牙 / WiFi)、传感器等。

核心特点

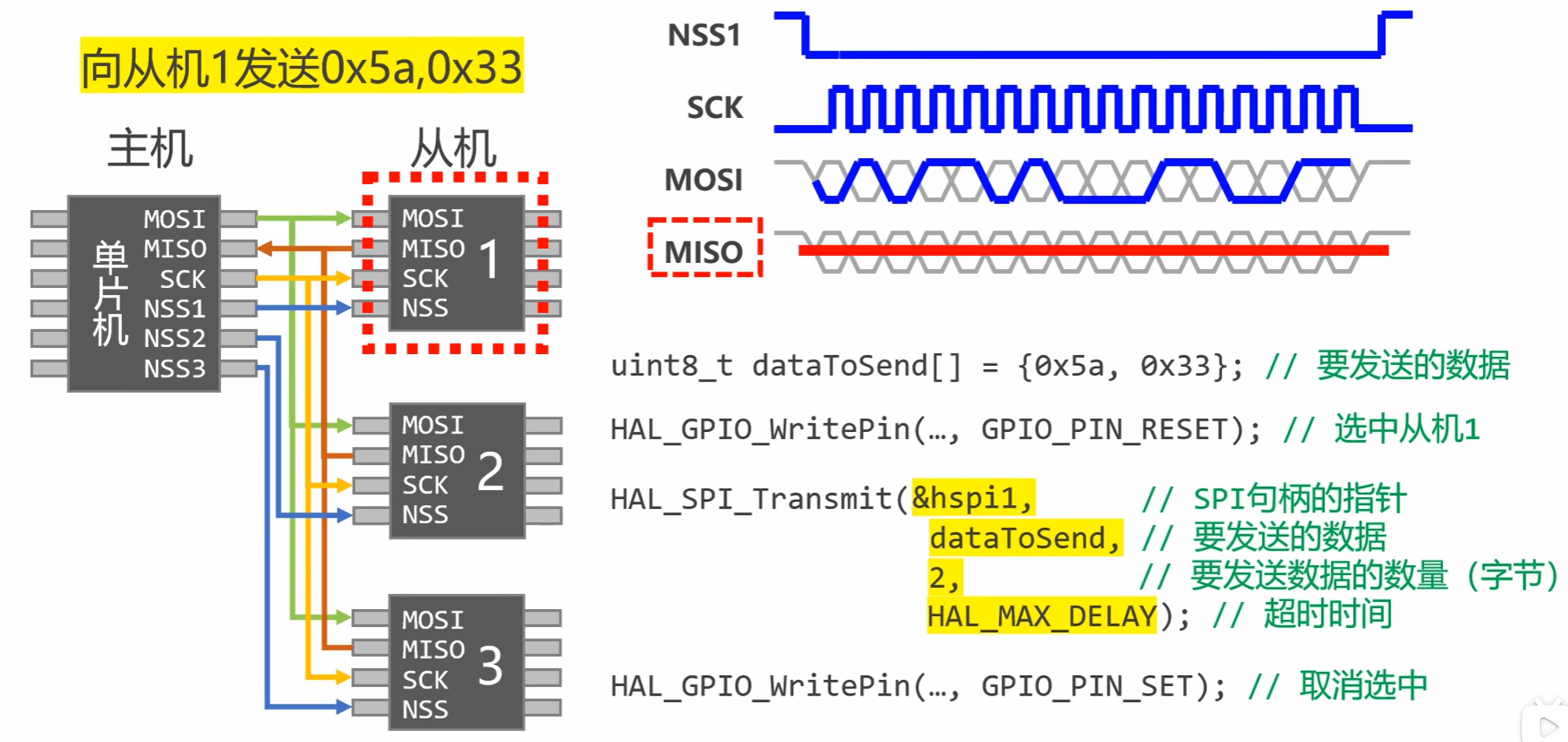

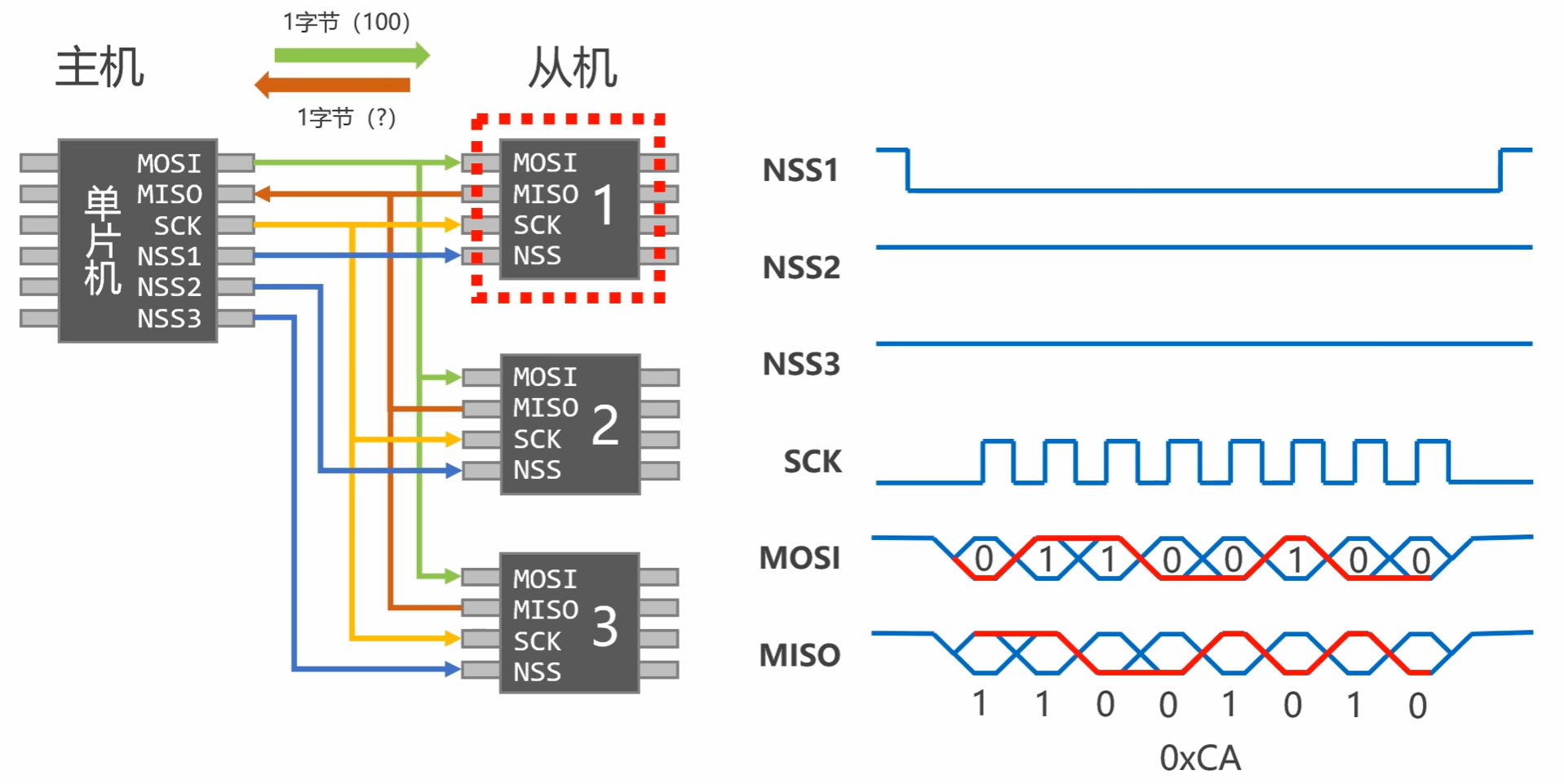

- 主从架构:1 个主设备(如 MCU)+ 多个从设备(如传感器、存储芯片),主设备控制时钟与通信时序。

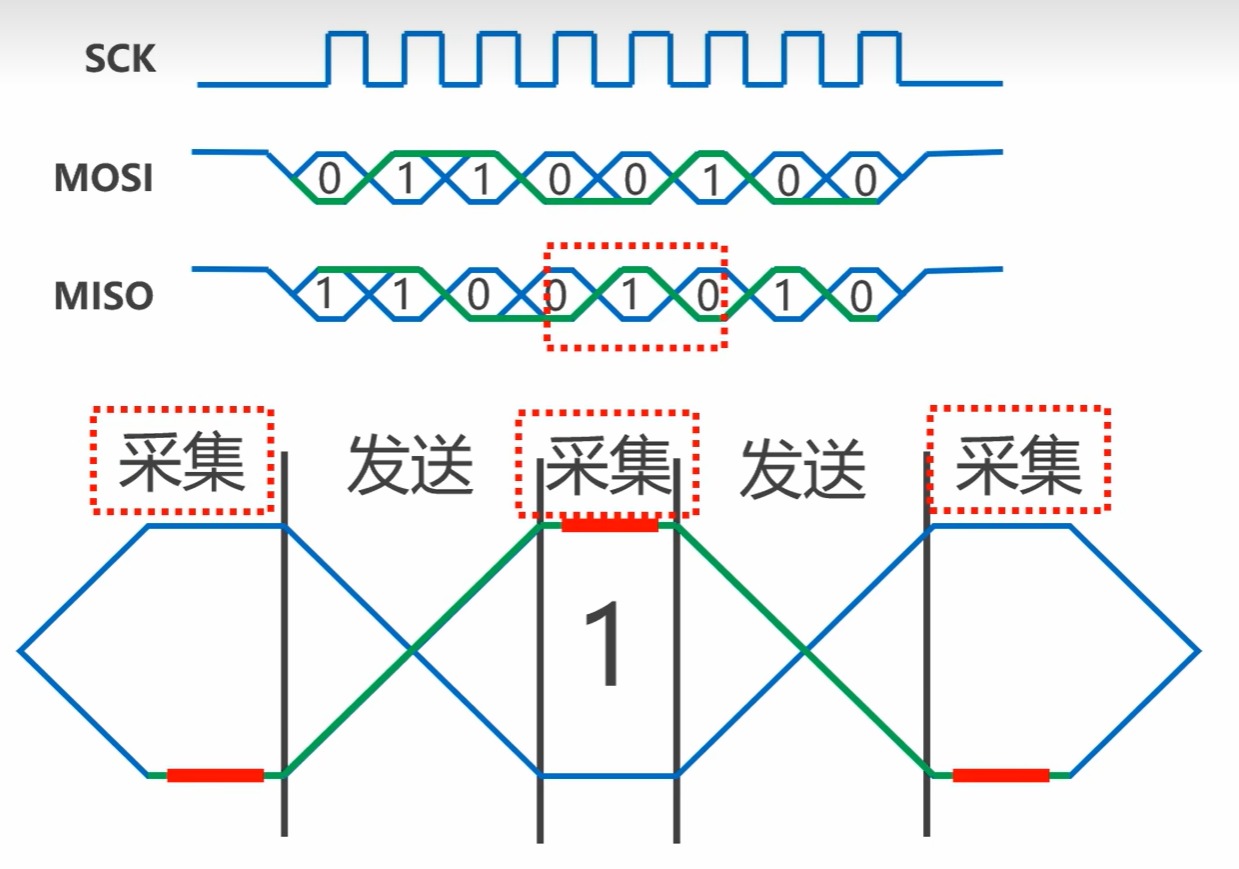

- 全双工通信:主、从设备可同时收发数据,传输效率高。

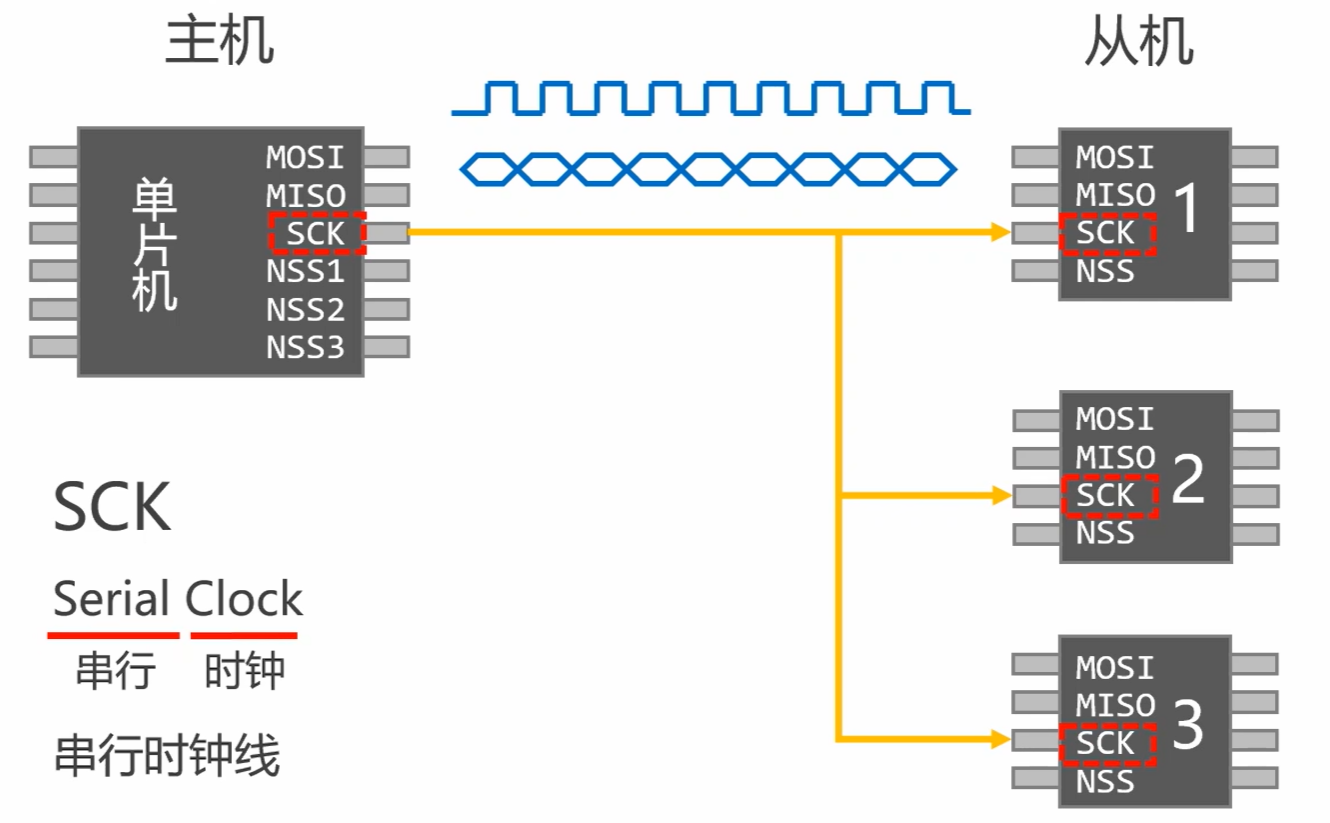

- 同步传输 :由主设备提供SCLK 时钟信号,数据收发与时钟沿同步。

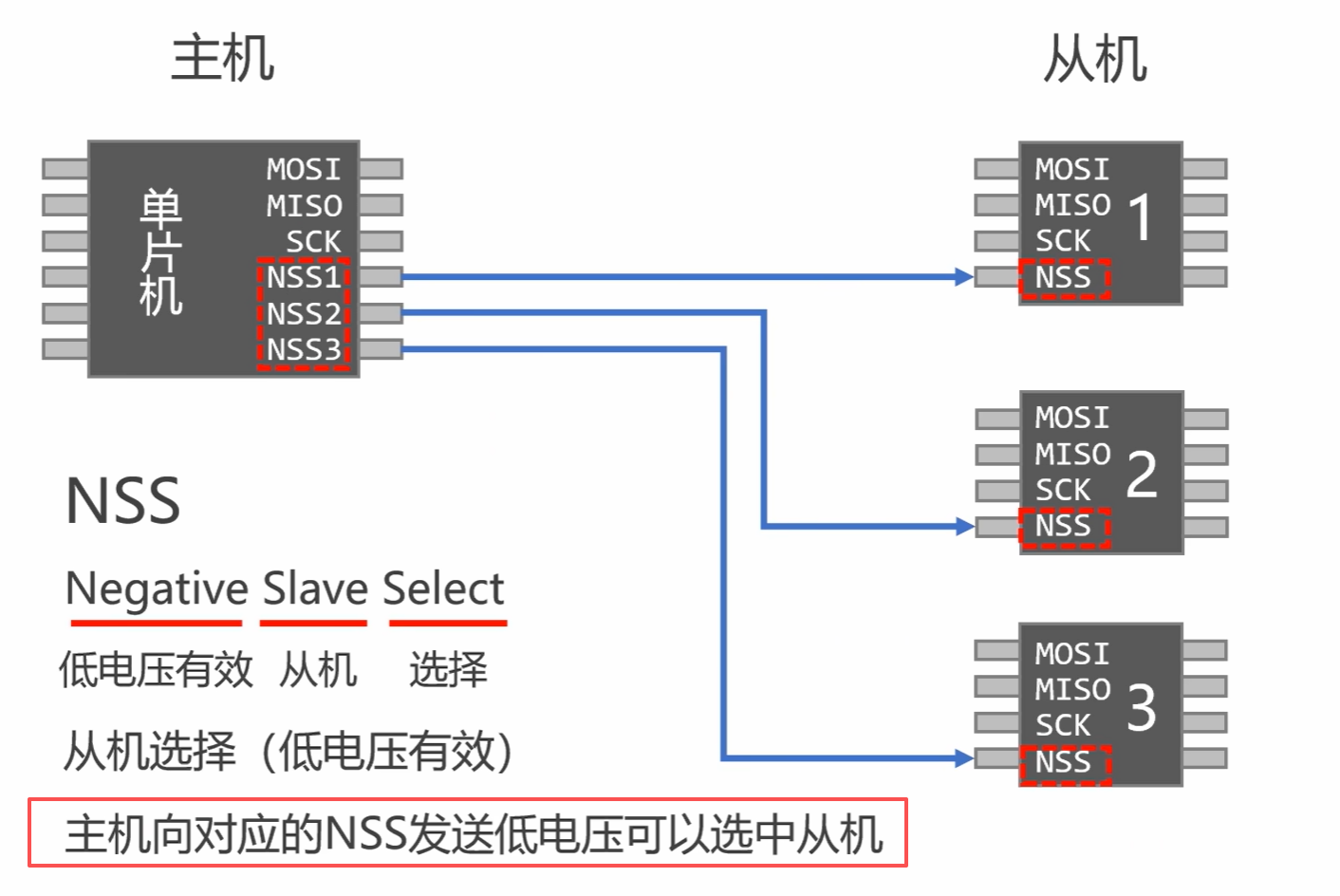

- 无固定地址 :通过CS/SS 片选信号(低电平有效)区分从设备,无应答与校验机制。

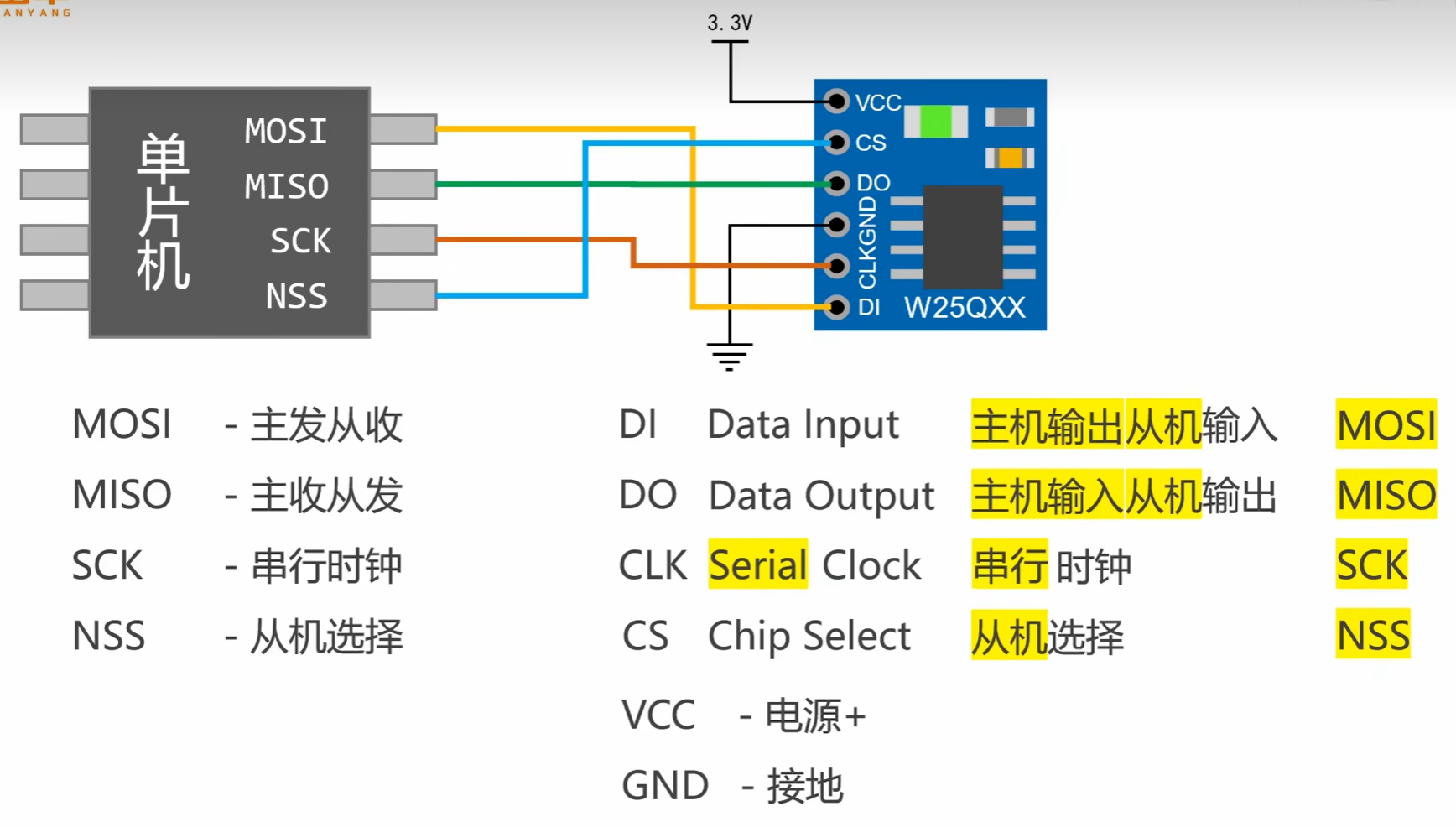

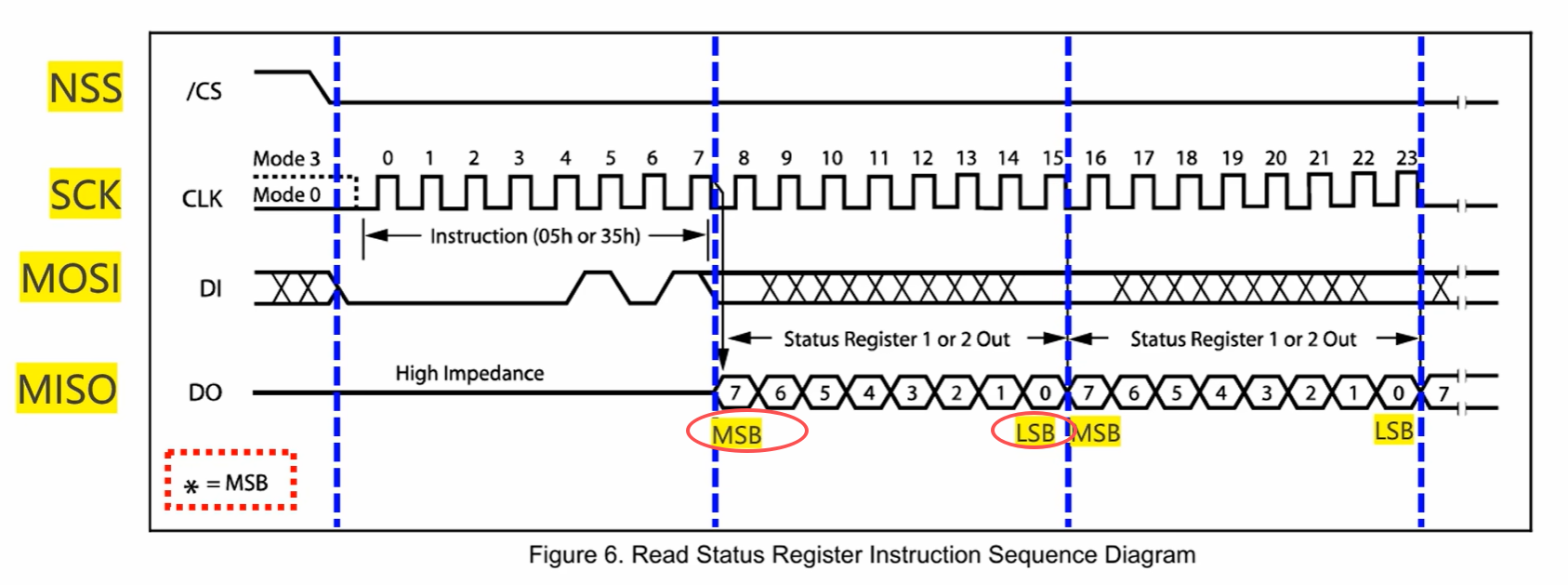

标准 4 线信号线

- SCLK:串行时钟(主设备输出)

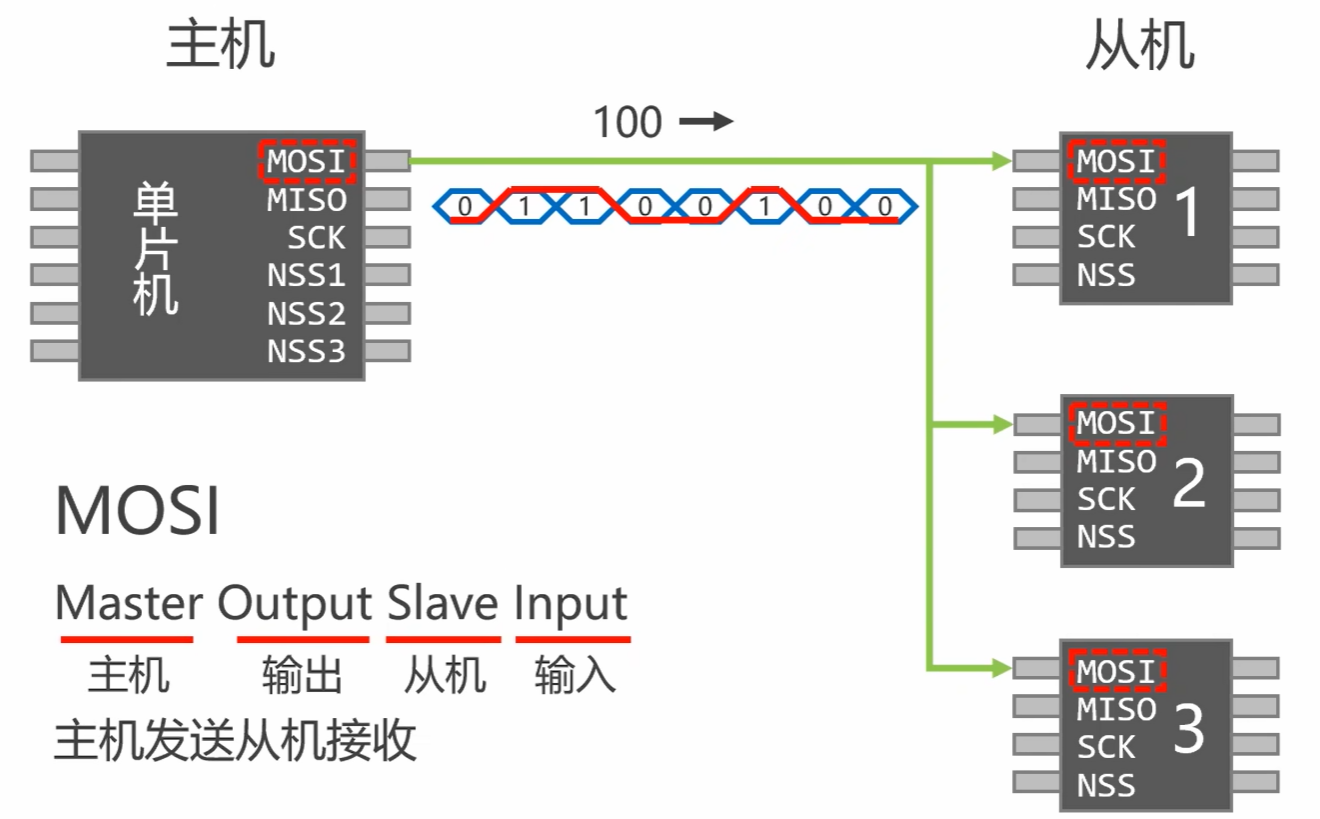

- MOSI:主发从收(Master Out Slave In)

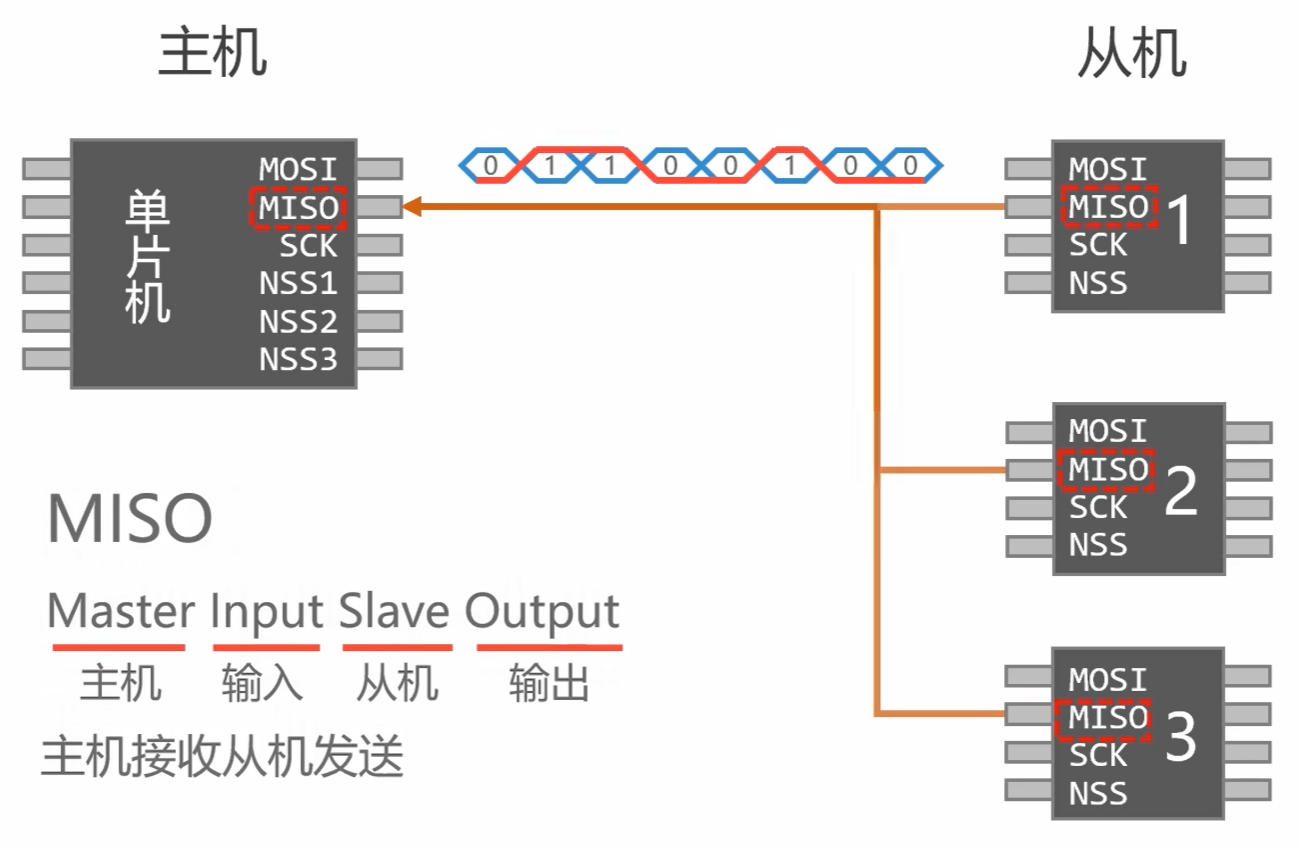

- MISO:主收从发(Master In Slave Out)

- CS/SS:片选信号(主设备输出,选中对应从设备)

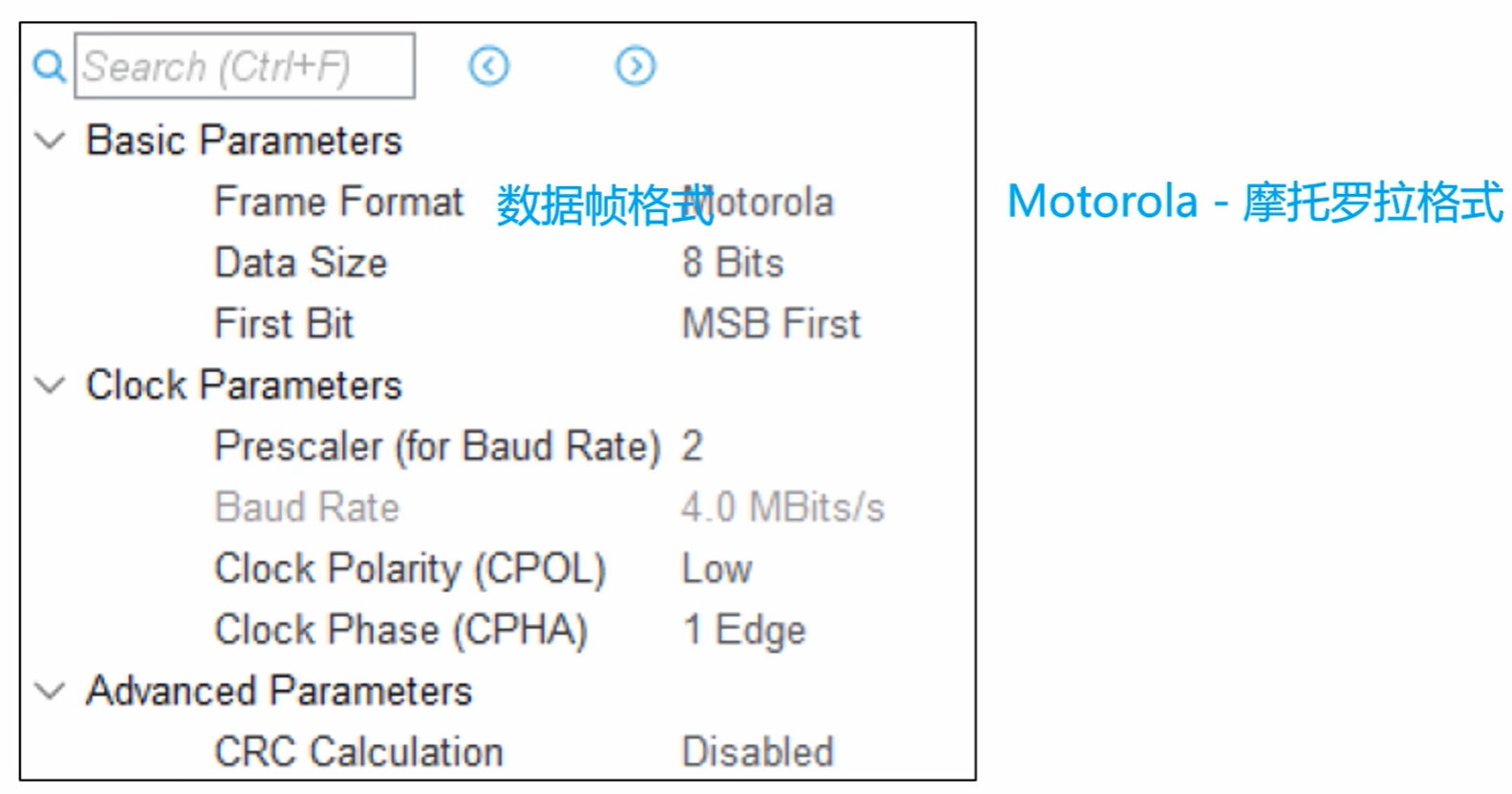

5个参数:

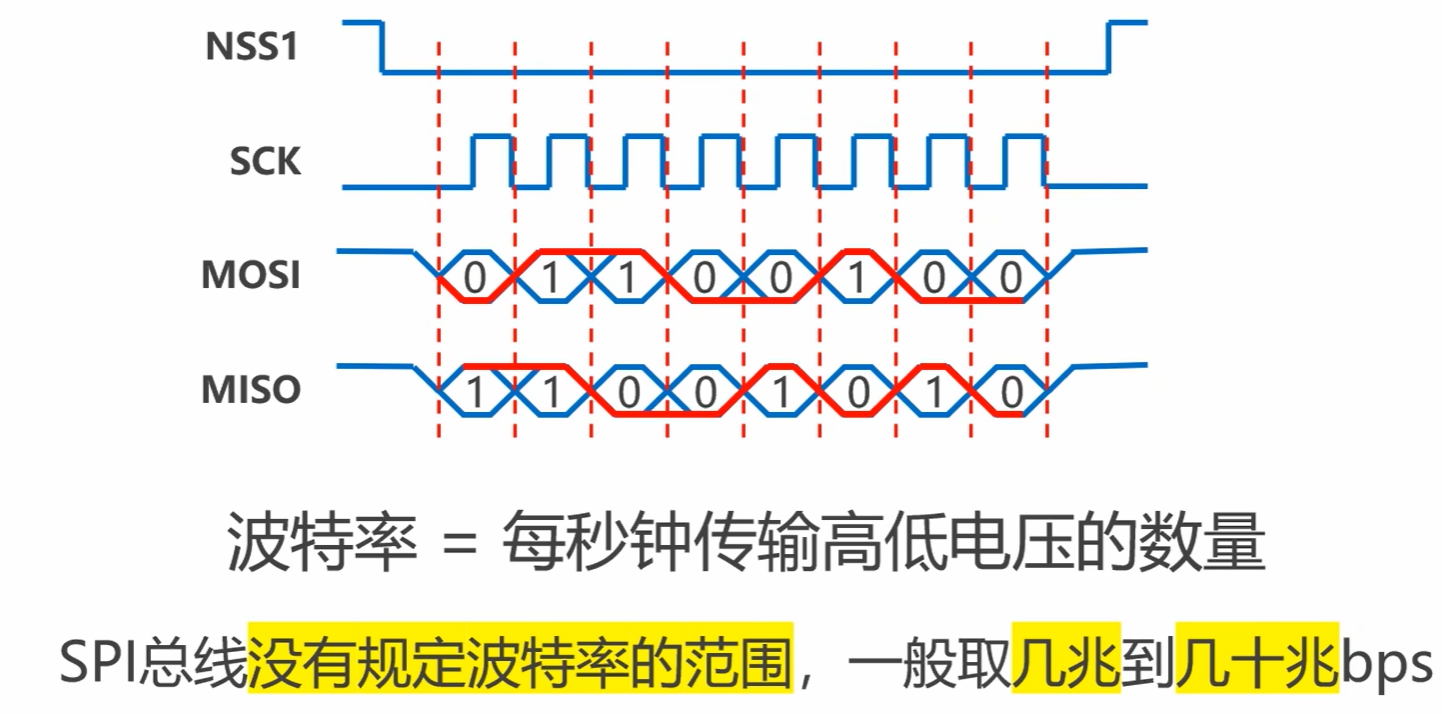

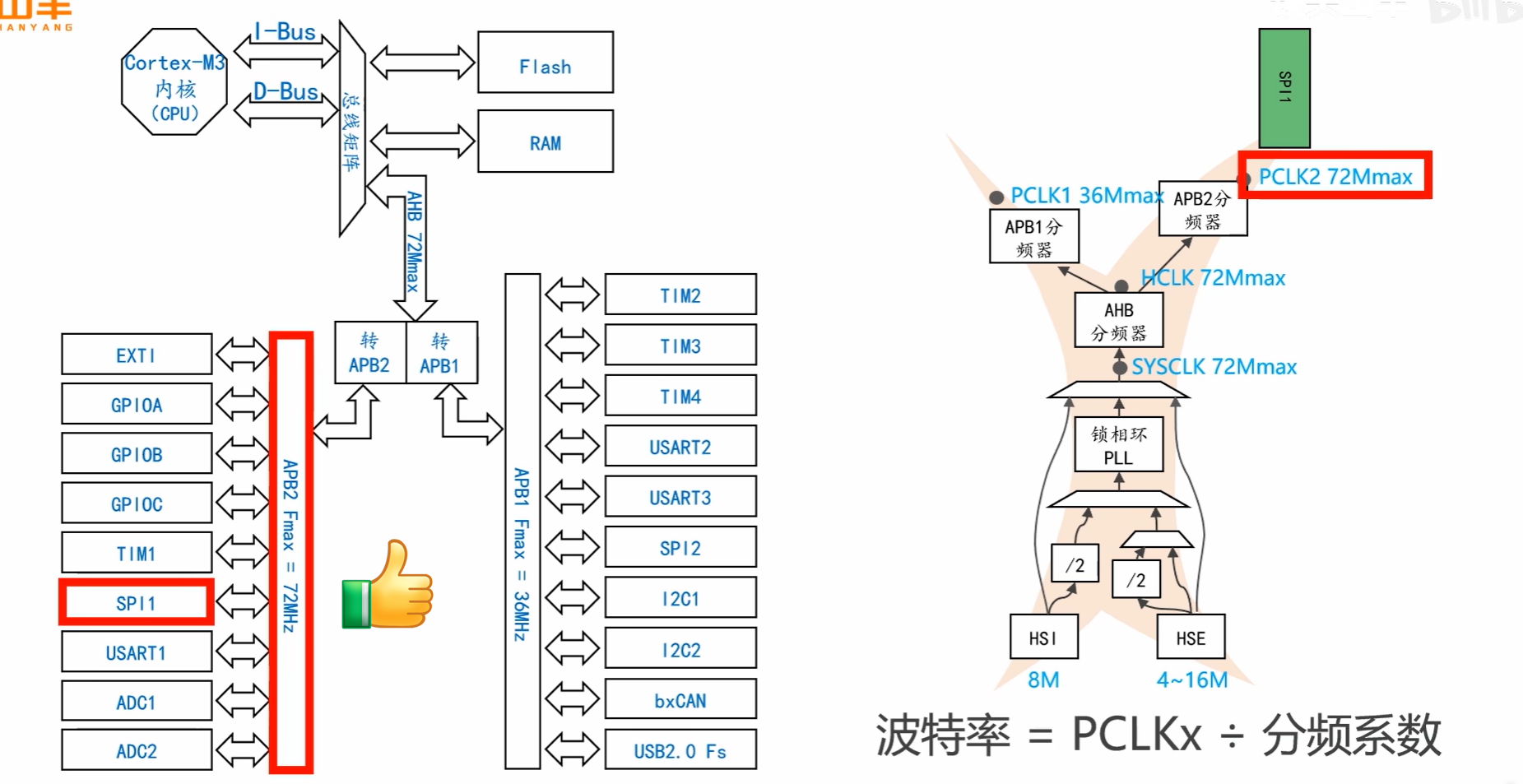

- 波特率

-

定义 :SPI 的数据传输速率 (单位:bps),由主设备的SCLK 时钟频率决定。

-

要点:主设备控制时钟,从设备需支持该速率;常见速率几十 MHz,高速 SPI 可达百 MHz 级。

-

-

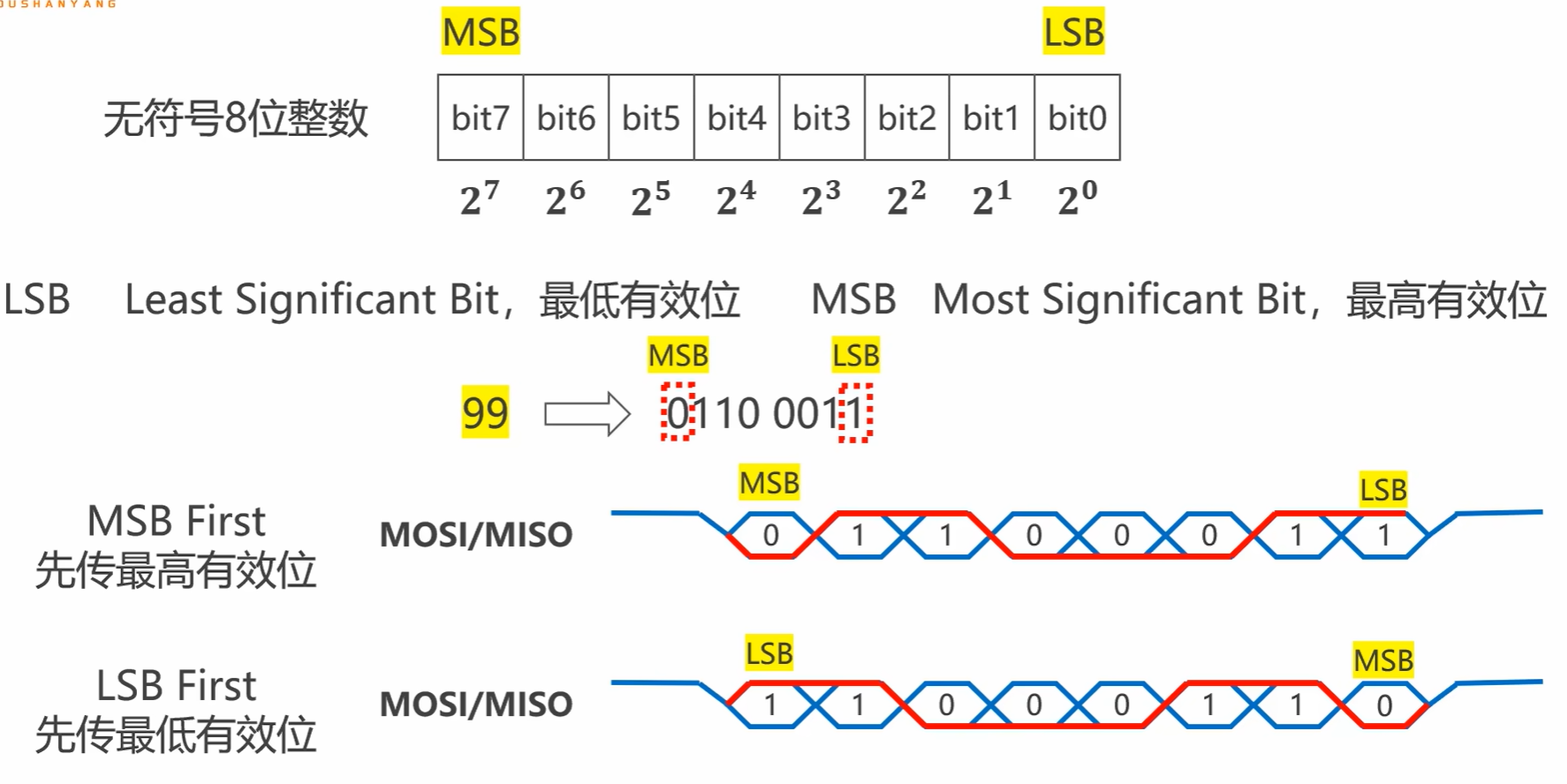

- 比特位传输顺序(MSB First / LSB First)

-

MSB First :最高位优先传输(SPI 默认模式,如 0x12 先传 0001,再传 0010)。

-

LSB First :最低位优先传输(仅少数外设支持,如部分传感器)。

-

关键 :主、从设备必须配置为相同顺序,否则数据解析错误。

-

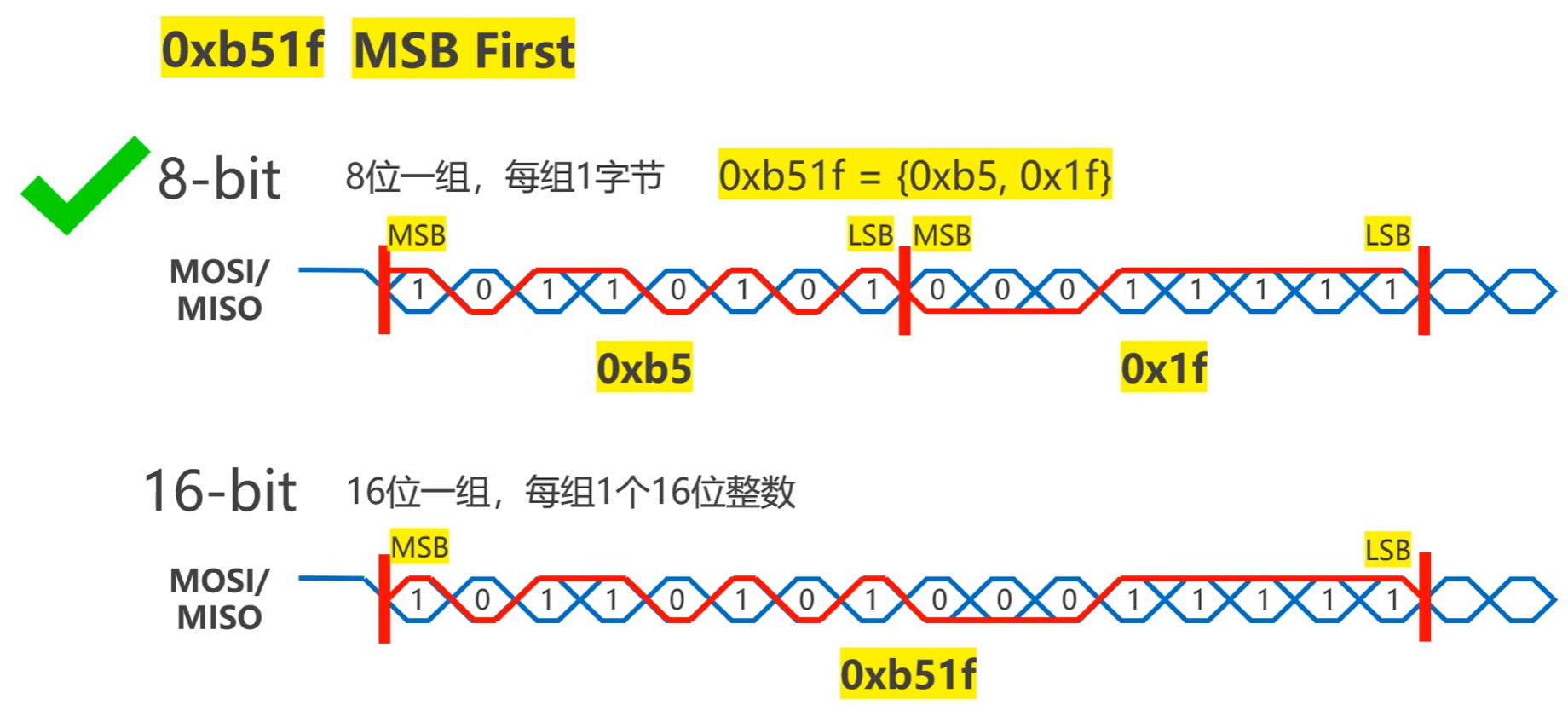

- 数据位长度(8 位 / 16 位)

-

8 位 :最常用,适配绝大多数 SPI 外设(Flash、传感器、LCD 等)。

-

16 位 :用于需要更大数据单元的场景(如部分音频 DAC、16 位 ADC)。

-

要点 :主从设备需配置为相同长度,否则数据帧错位。

-

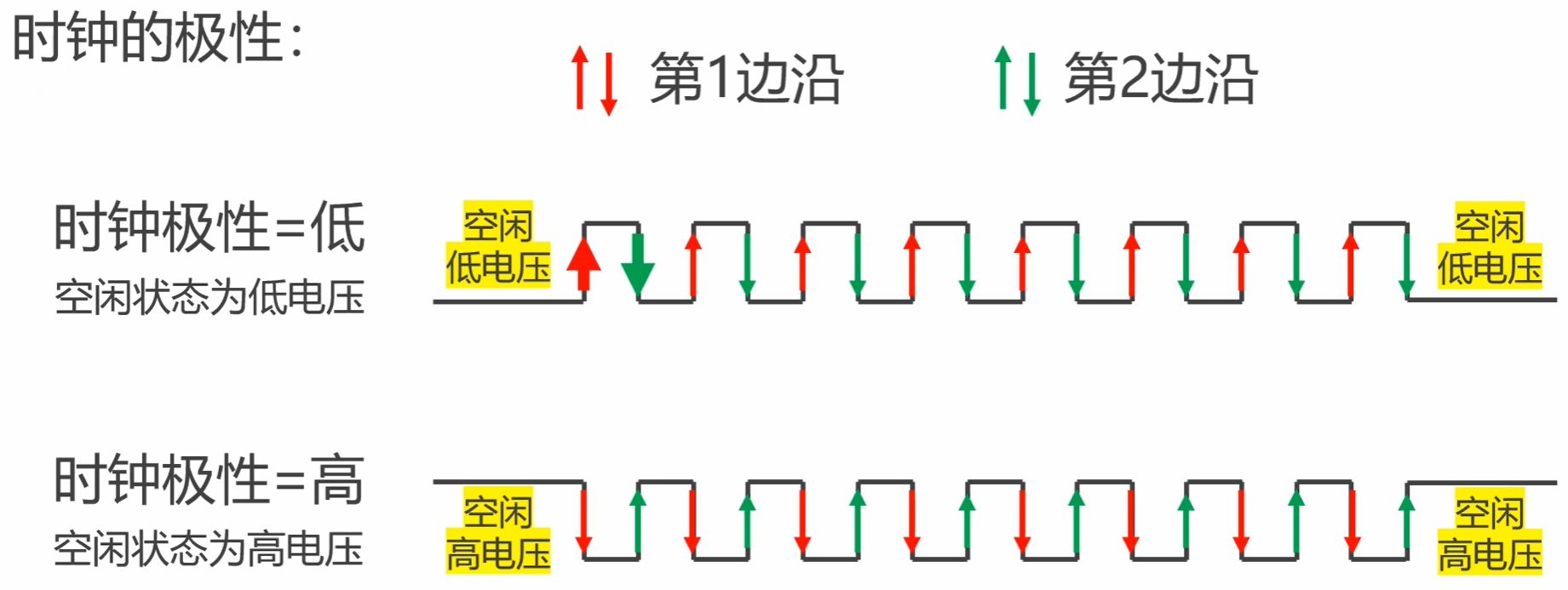

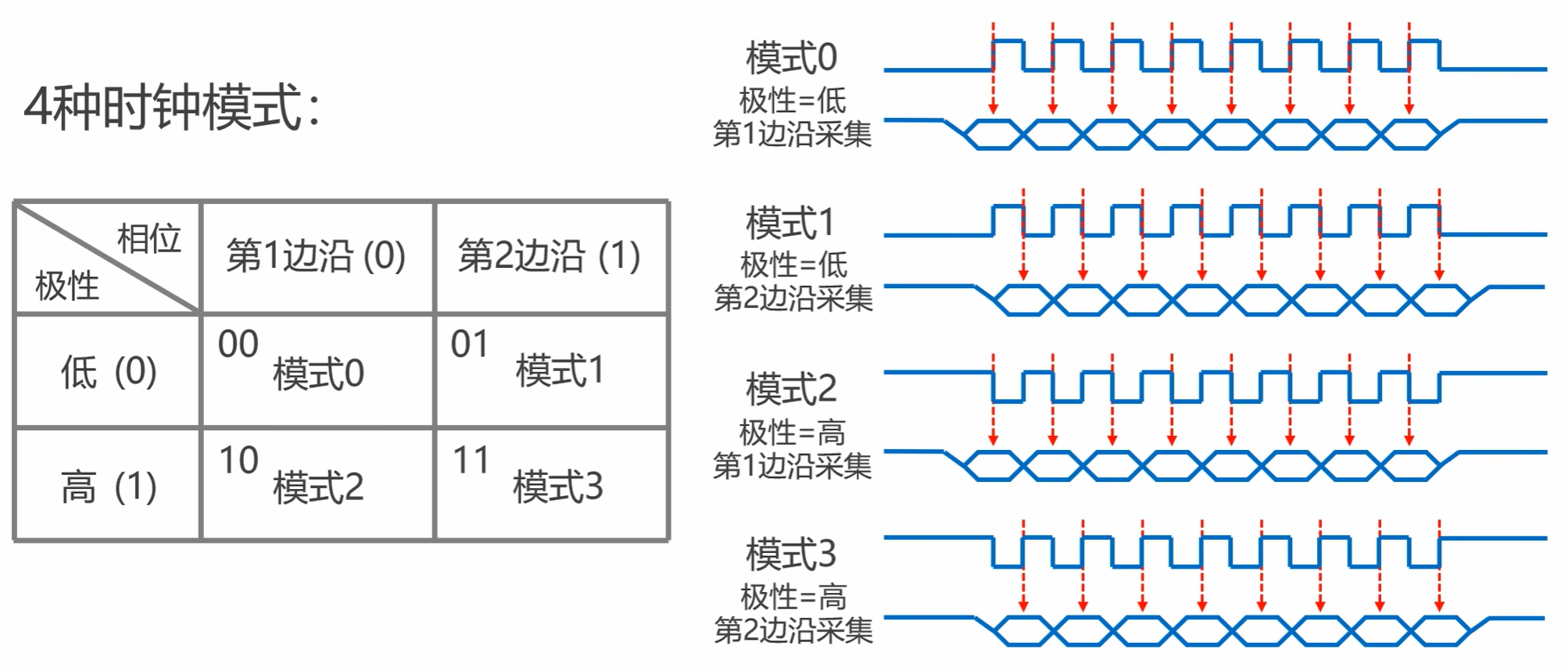

- 时钟的极性(CPOL)

-

CPOL=0 :SCLK空闲时为低电平,数据传输时产生高脉冲。

-

CPOL=1 :SCLK空闲时为高电平,数据传输时产生低脉冲。

-

关键:主、从设备 CPOL 必须一致,否则时钟时序不匹配。

-

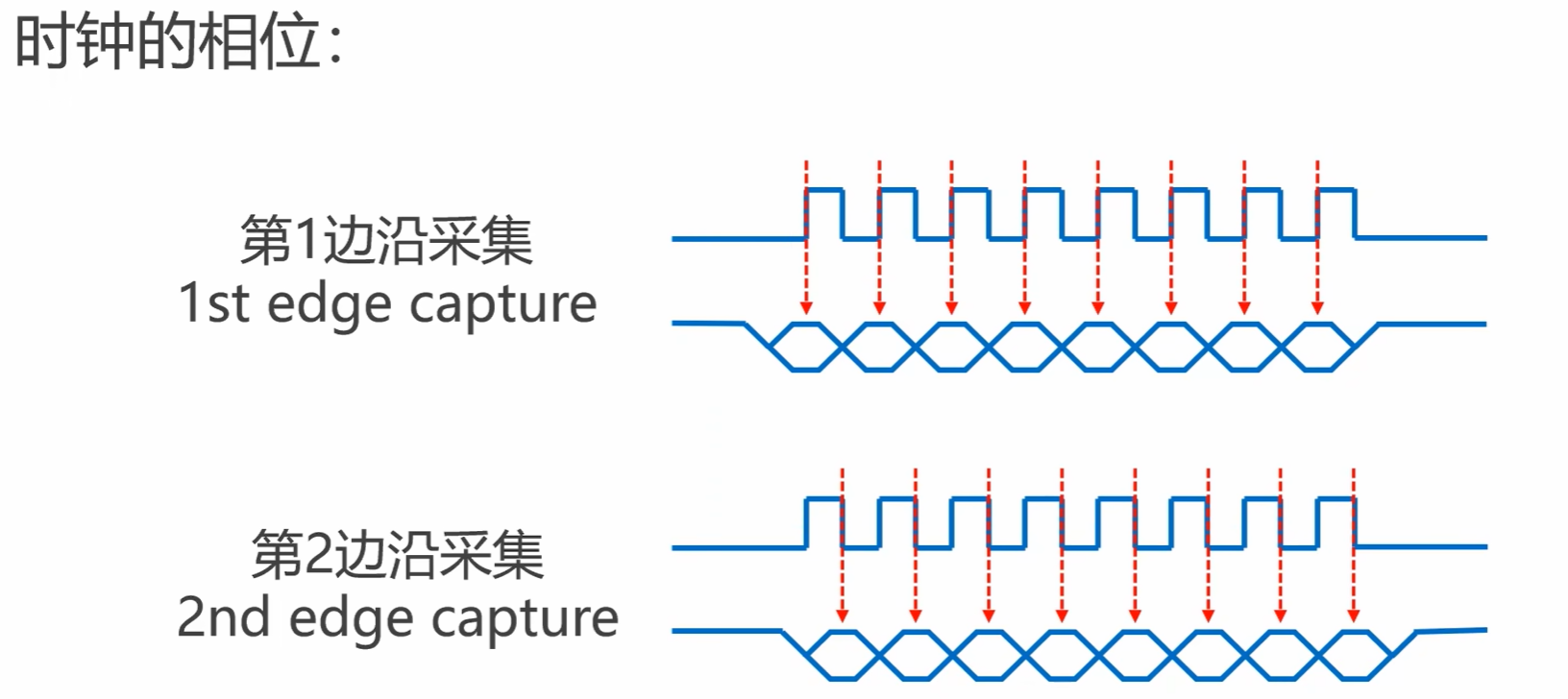

- 时钟的相位(CPHA)

-

CPHA=0 :在SCLK 的第一个跳变沿 (上升 / 下降沿,由 CPOL 决定)采样数据。

-

CPHA=1 :在SCLK 的第二个跳变沿采样数据。

-

关键 :与 CPOL 组合形成4 种 SPI 工作模式 (Mode 0~3),主从必须配置为同一模式。

-

-

-

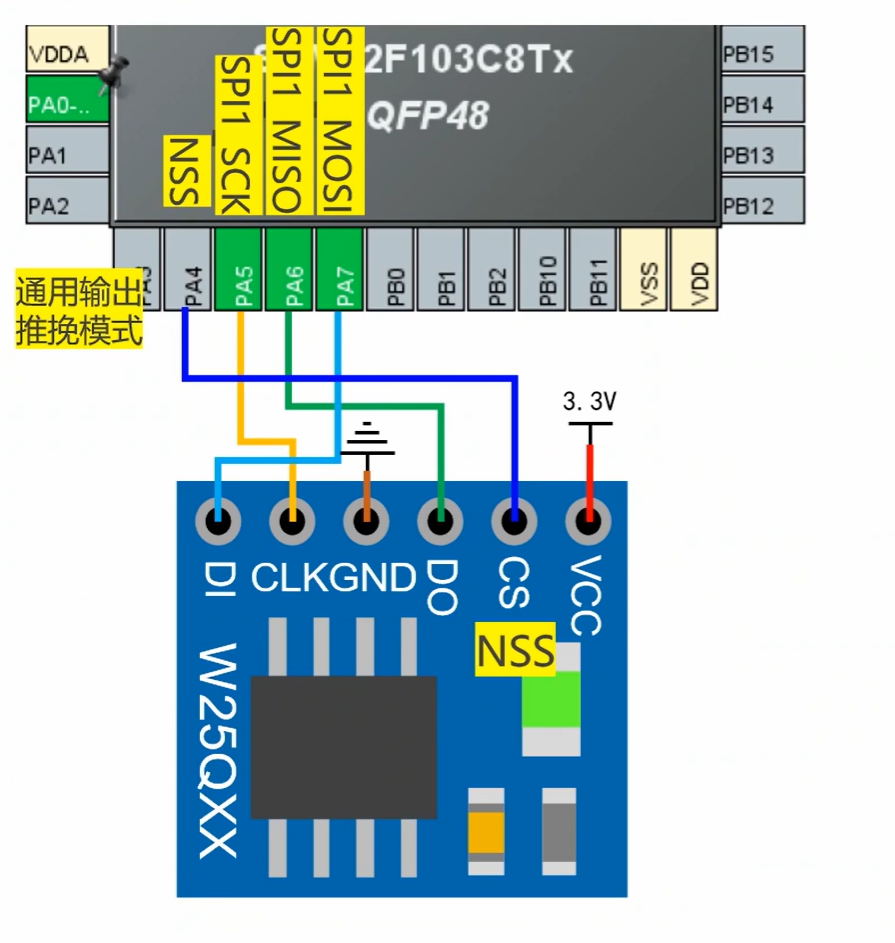

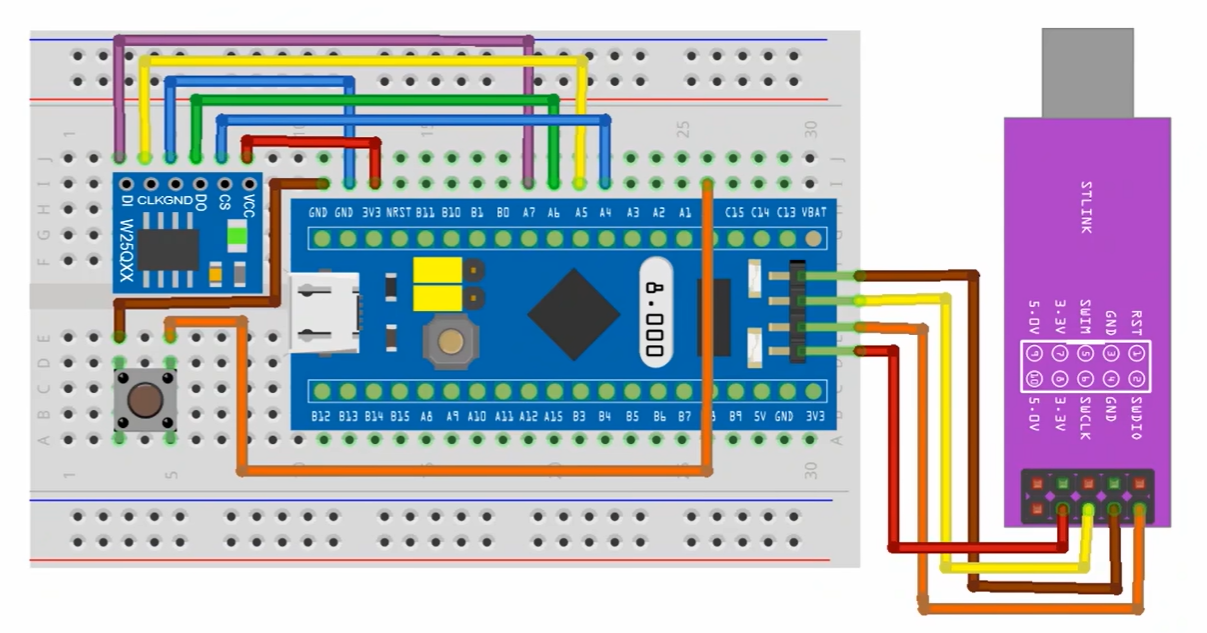

SPI 外部Flash实验

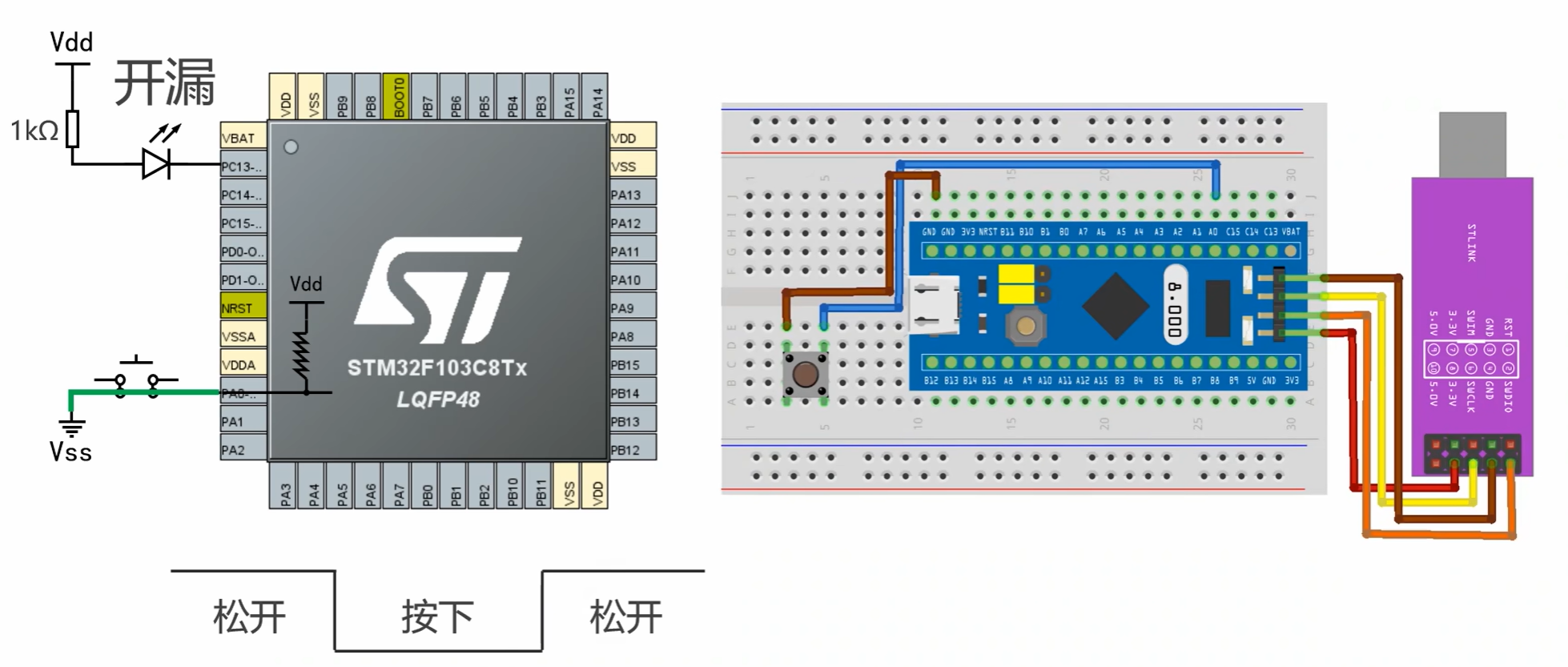

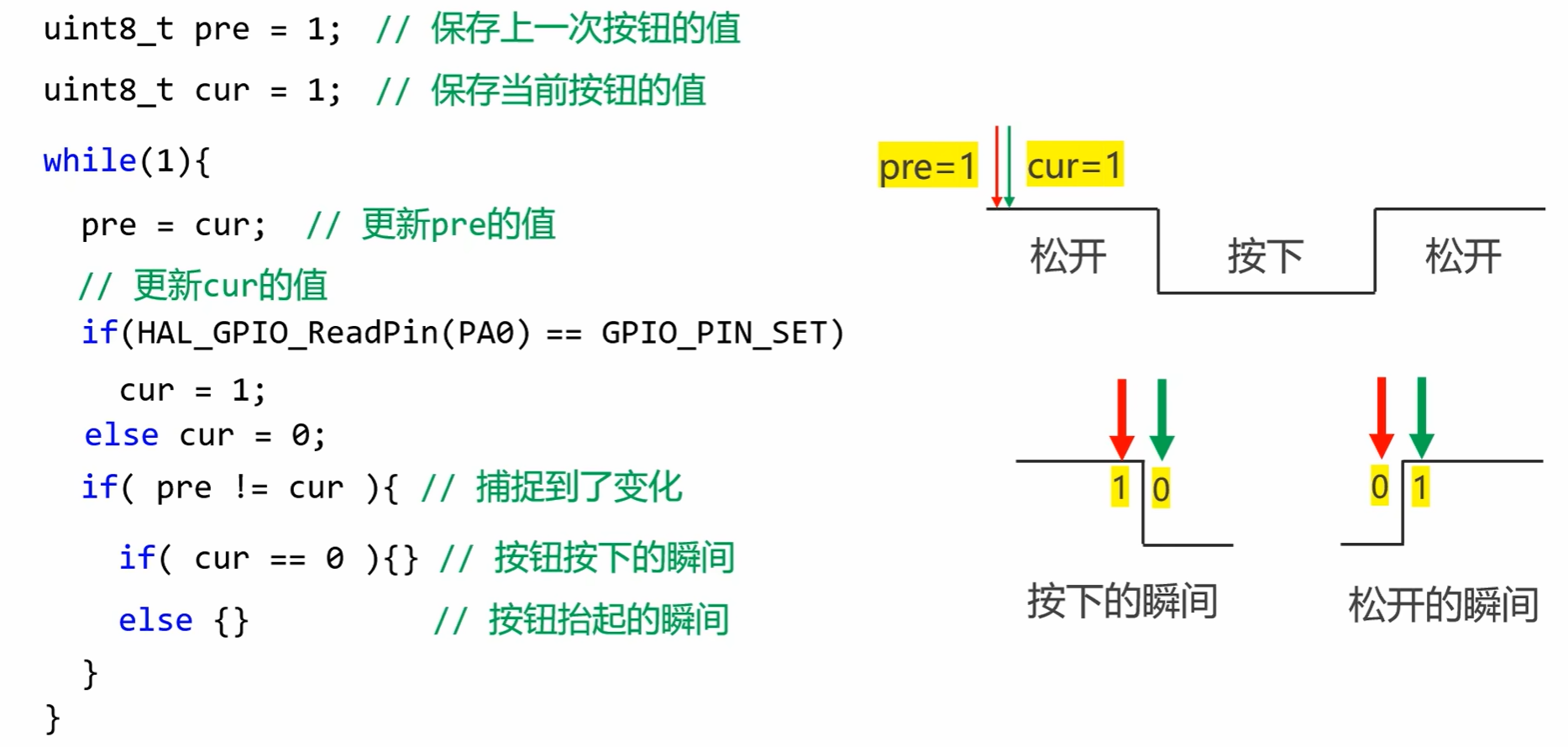

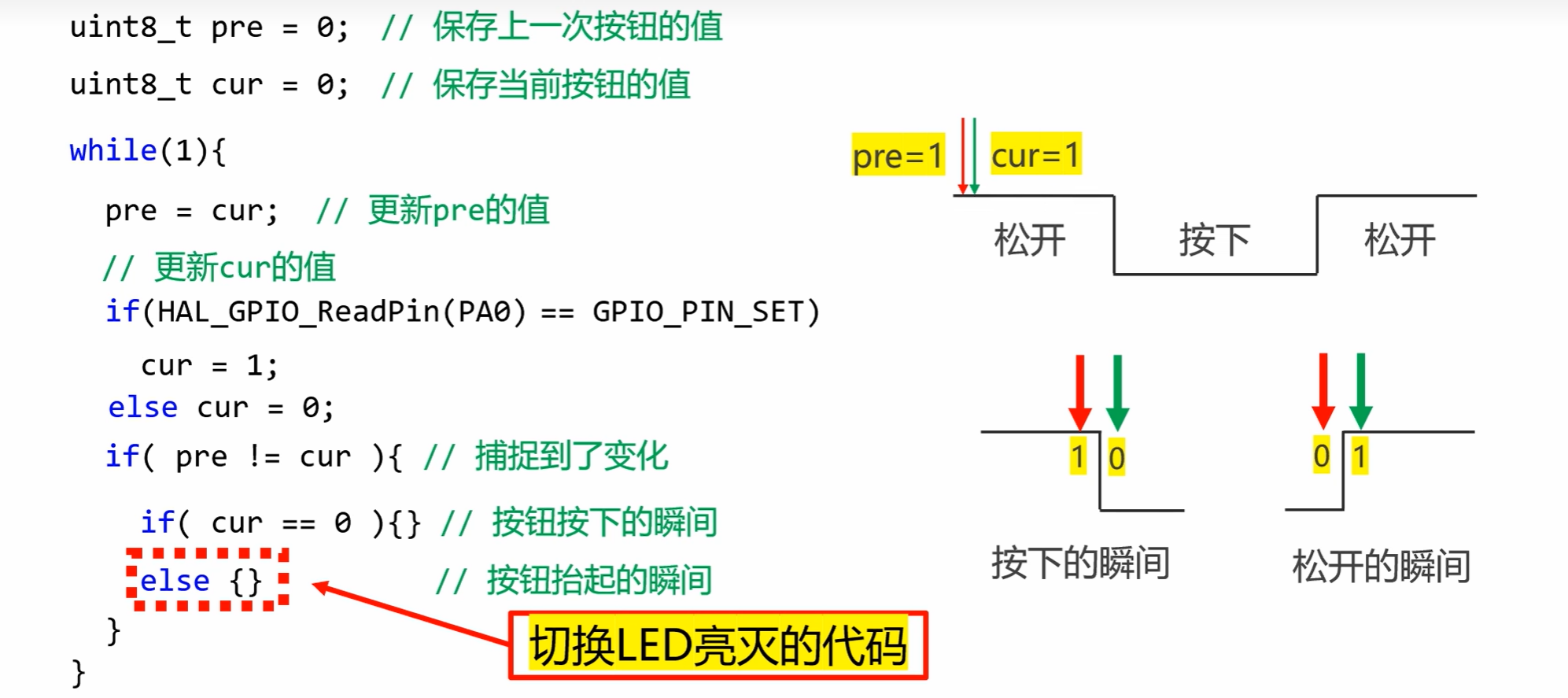

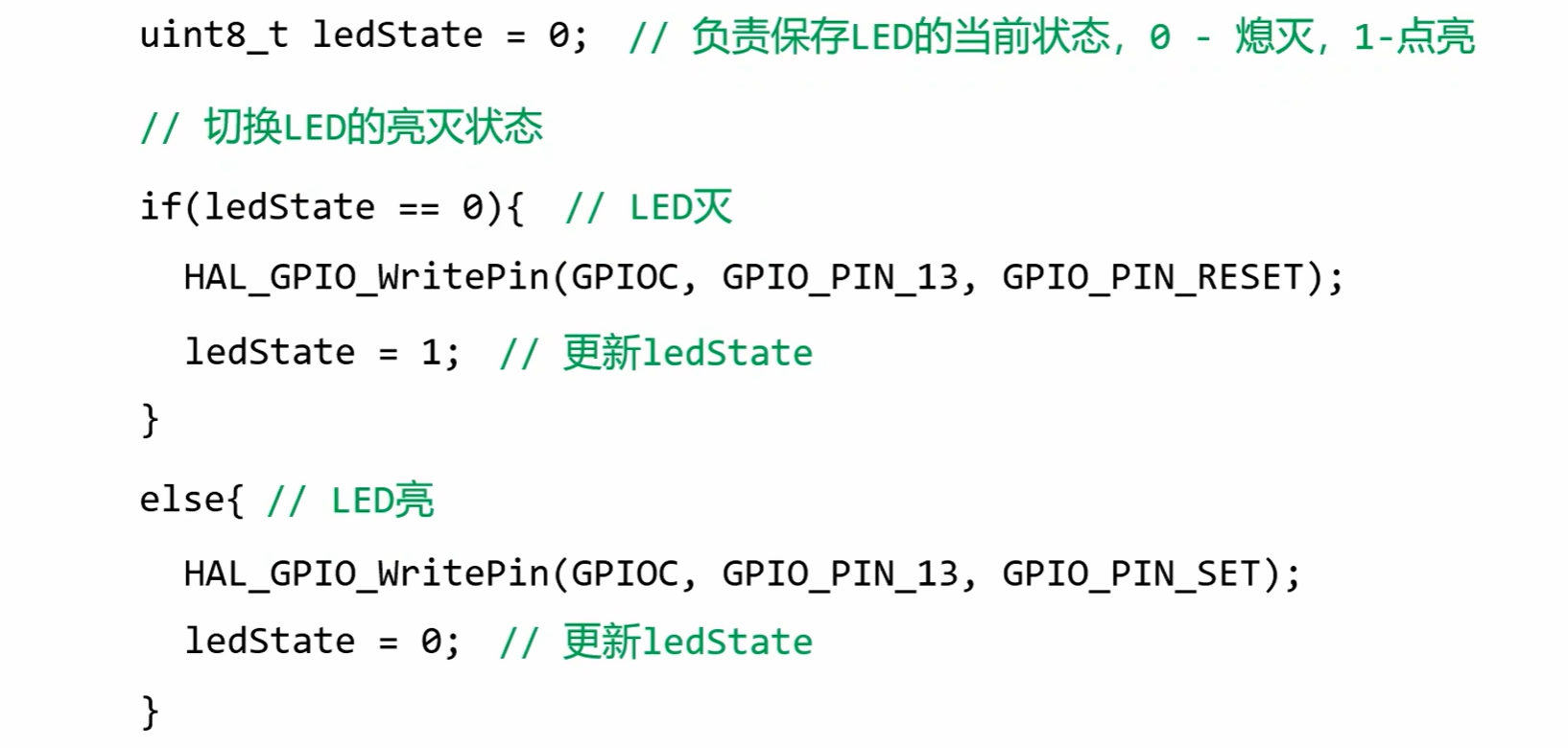

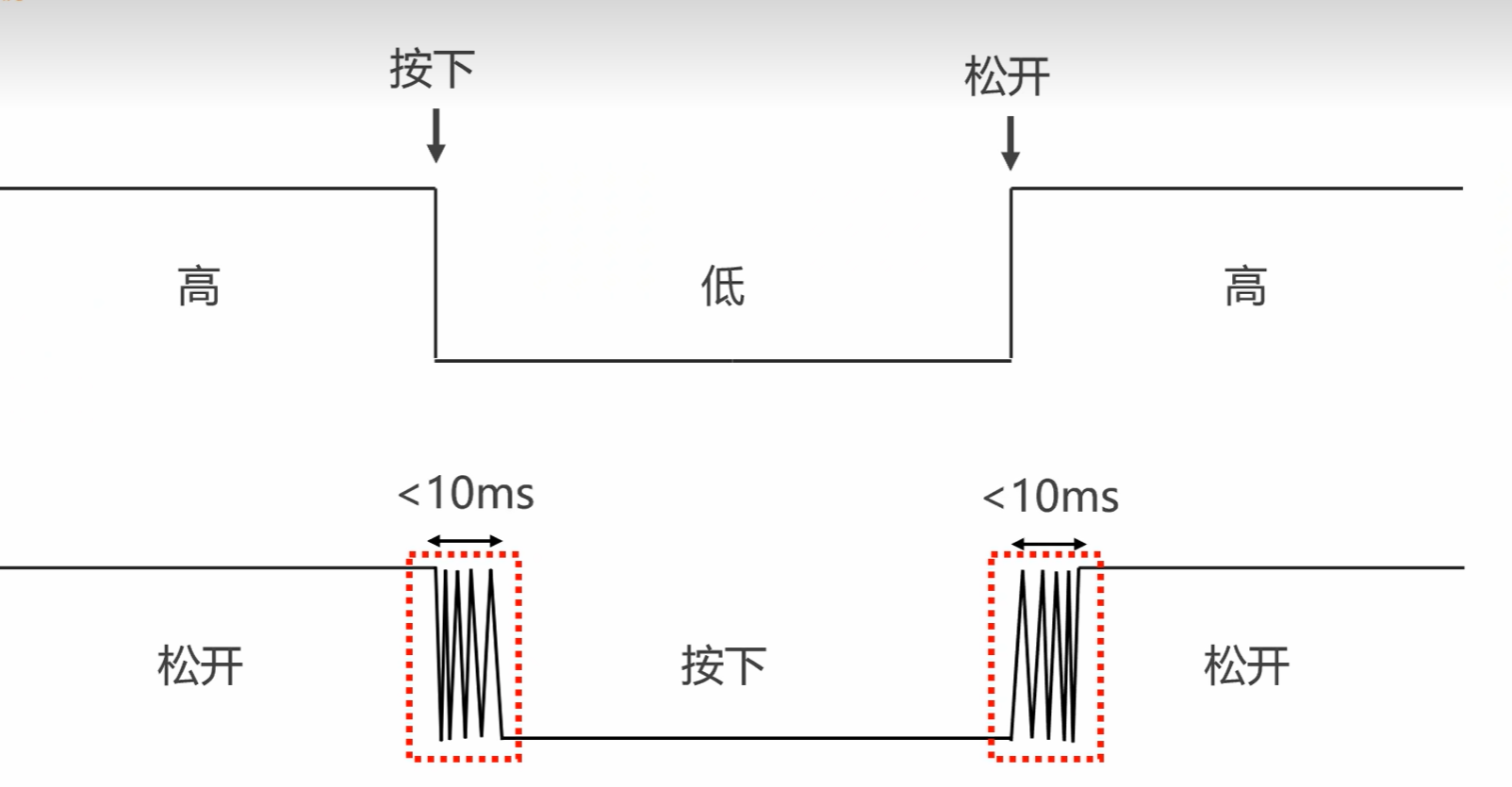

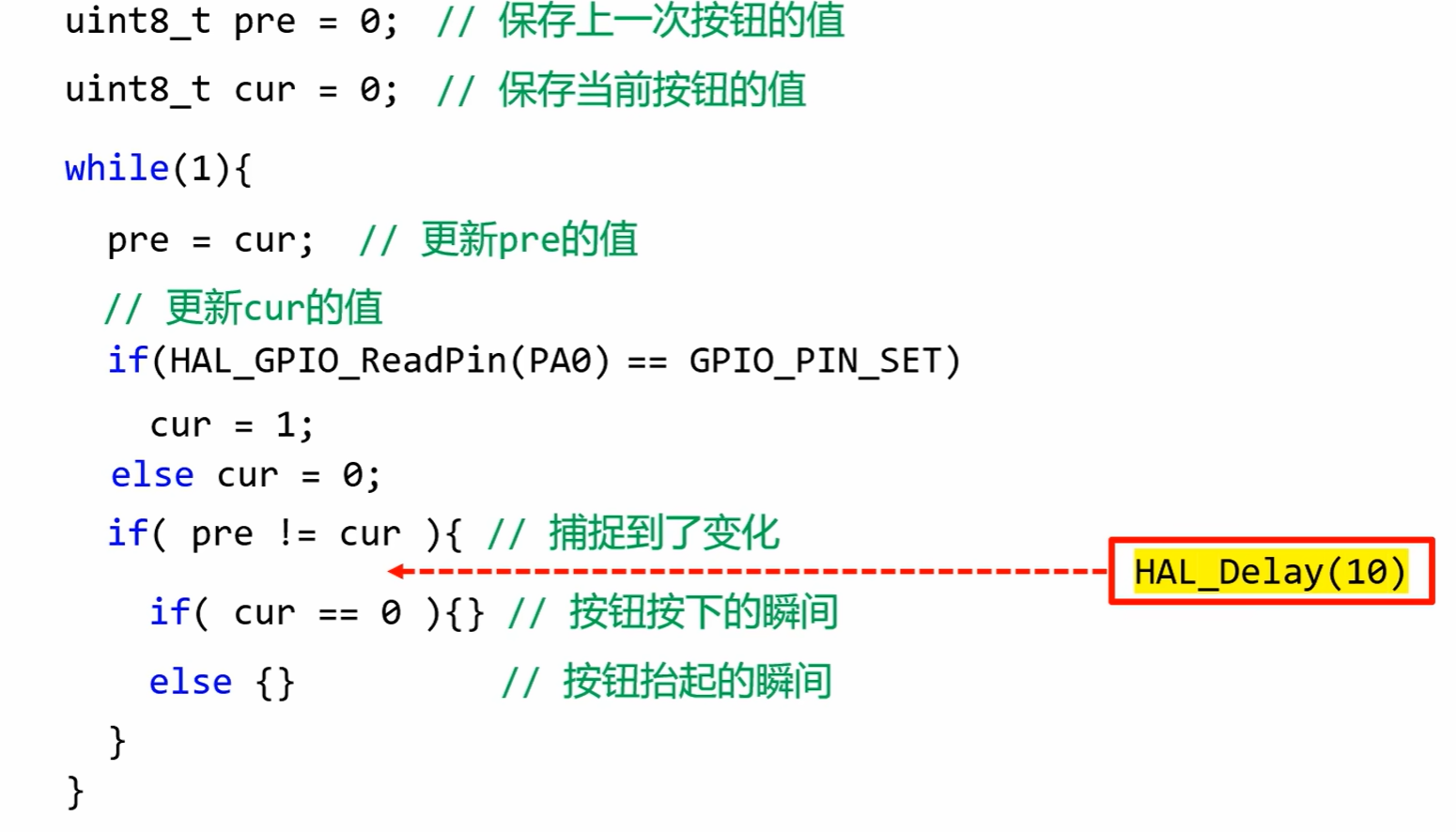

消抖处理

flash

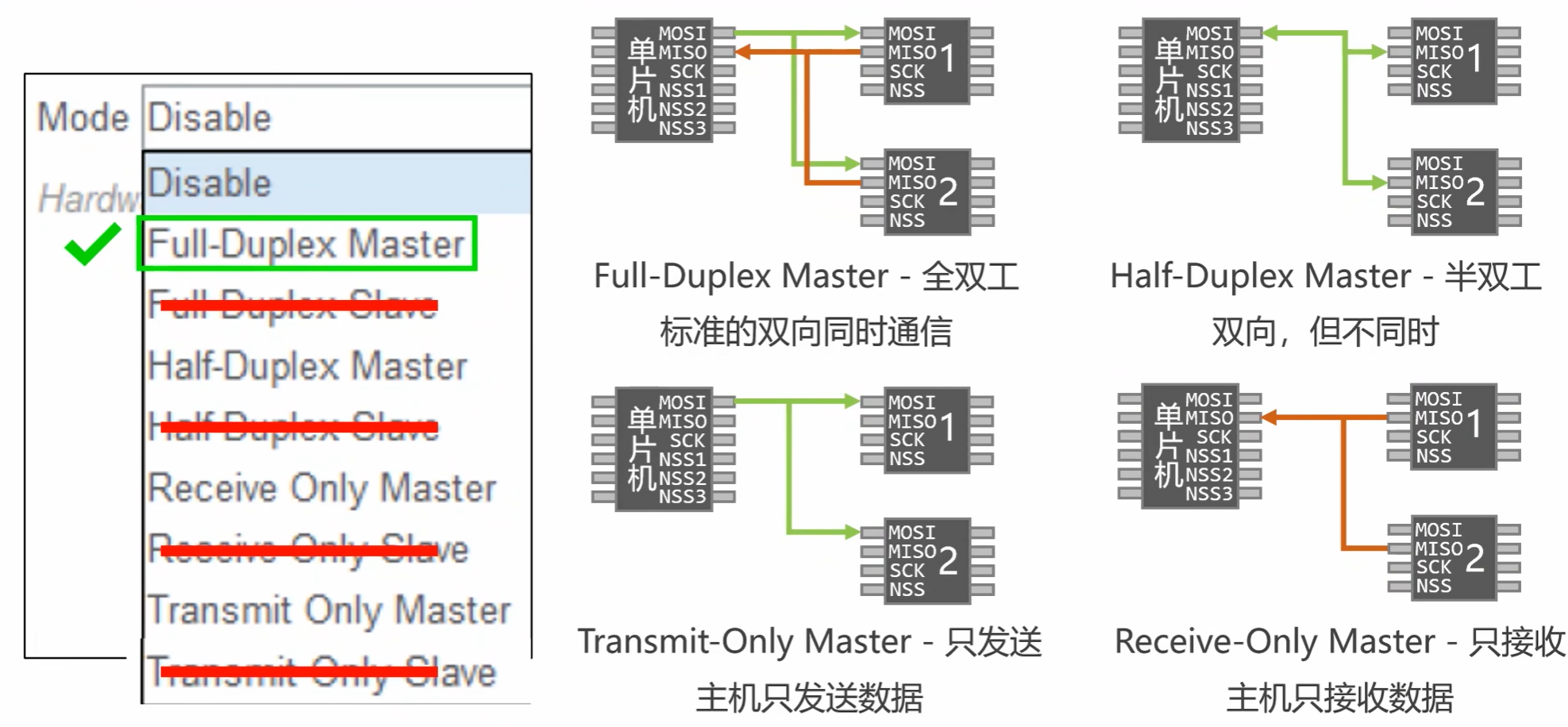

SPI模式,大部分情况选第一种模式,也就是全双工。

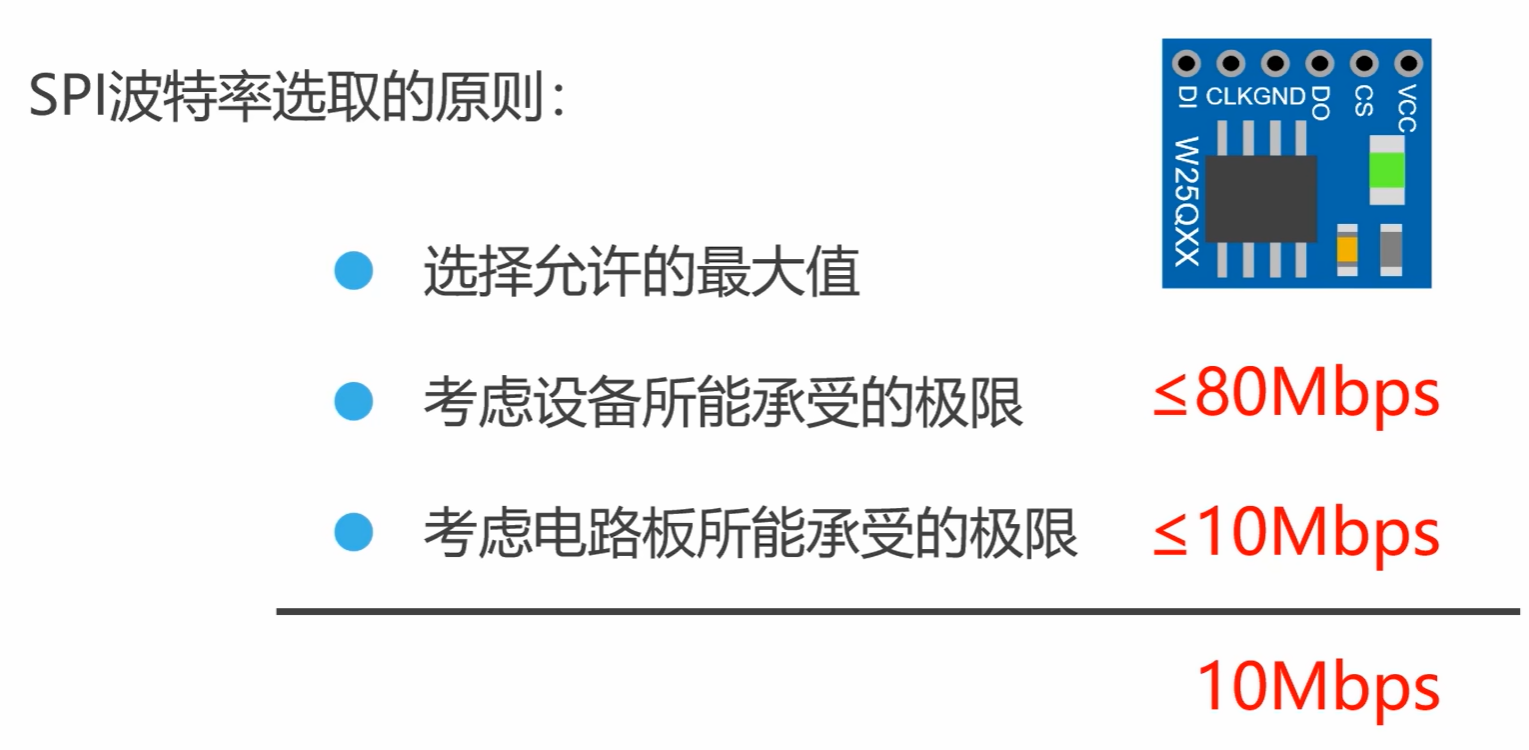

baud rate设置

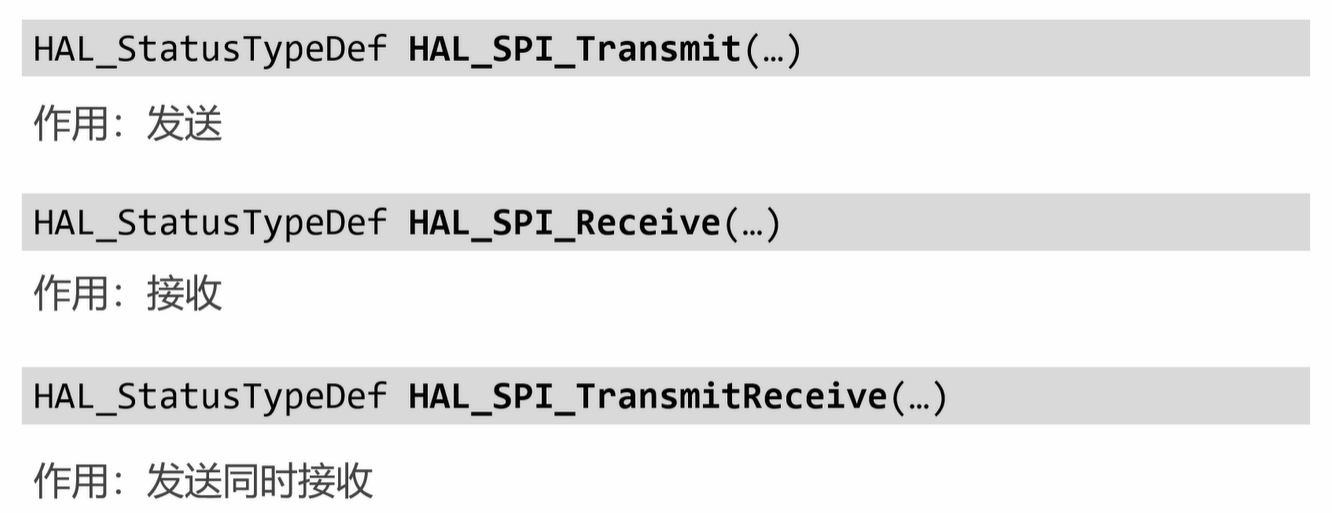

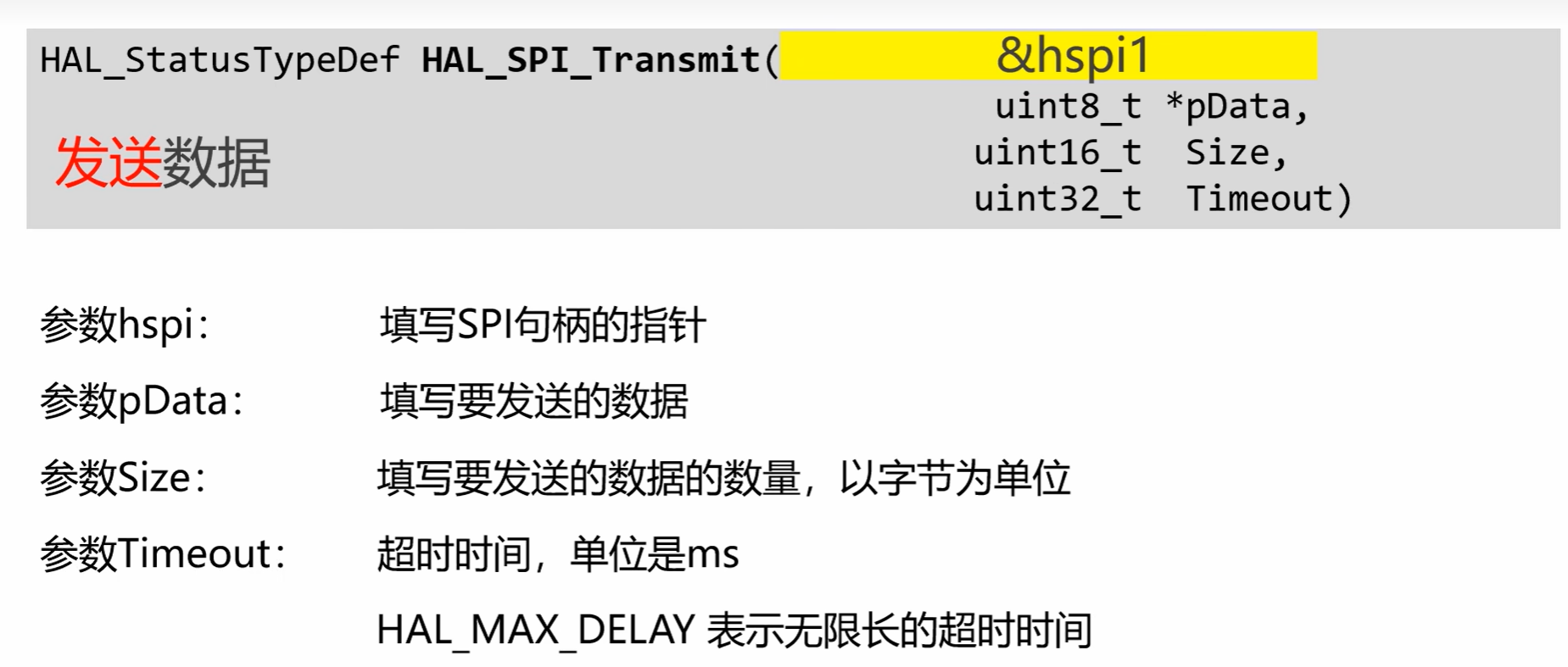

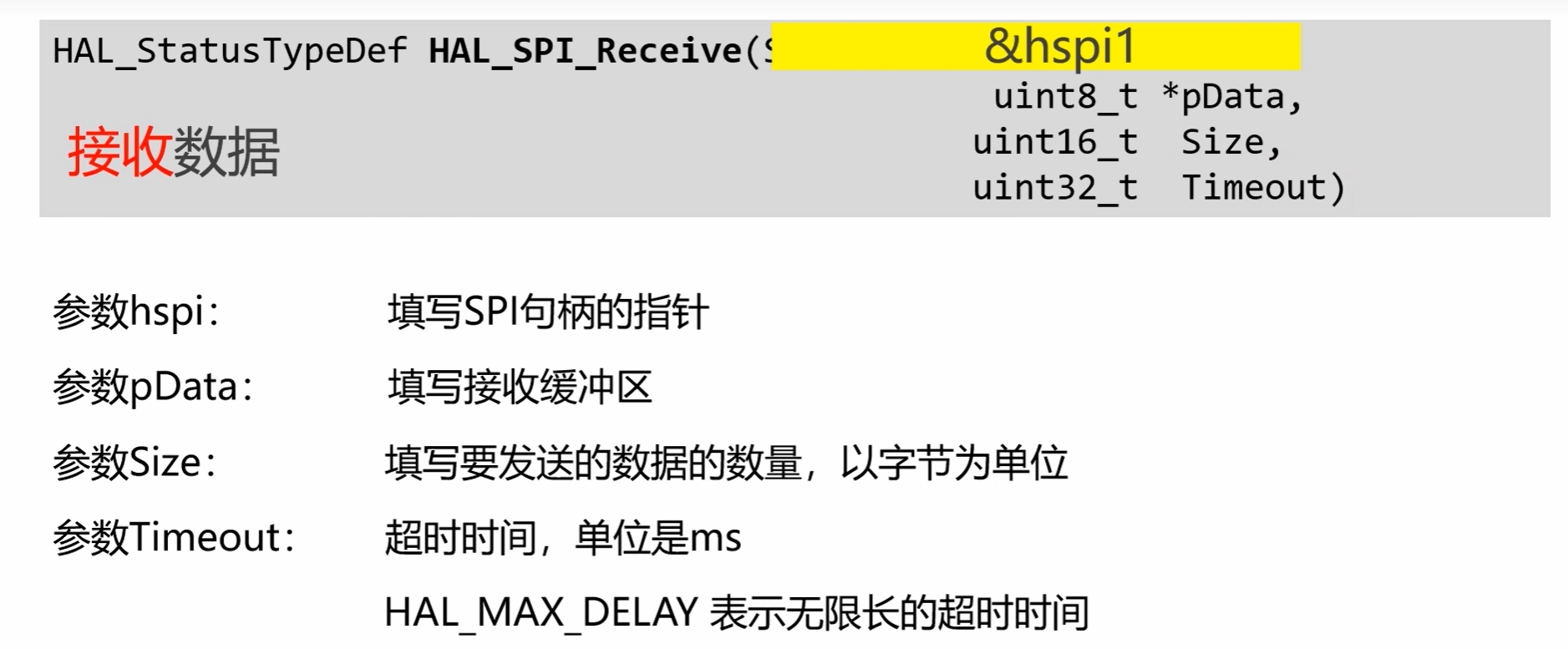

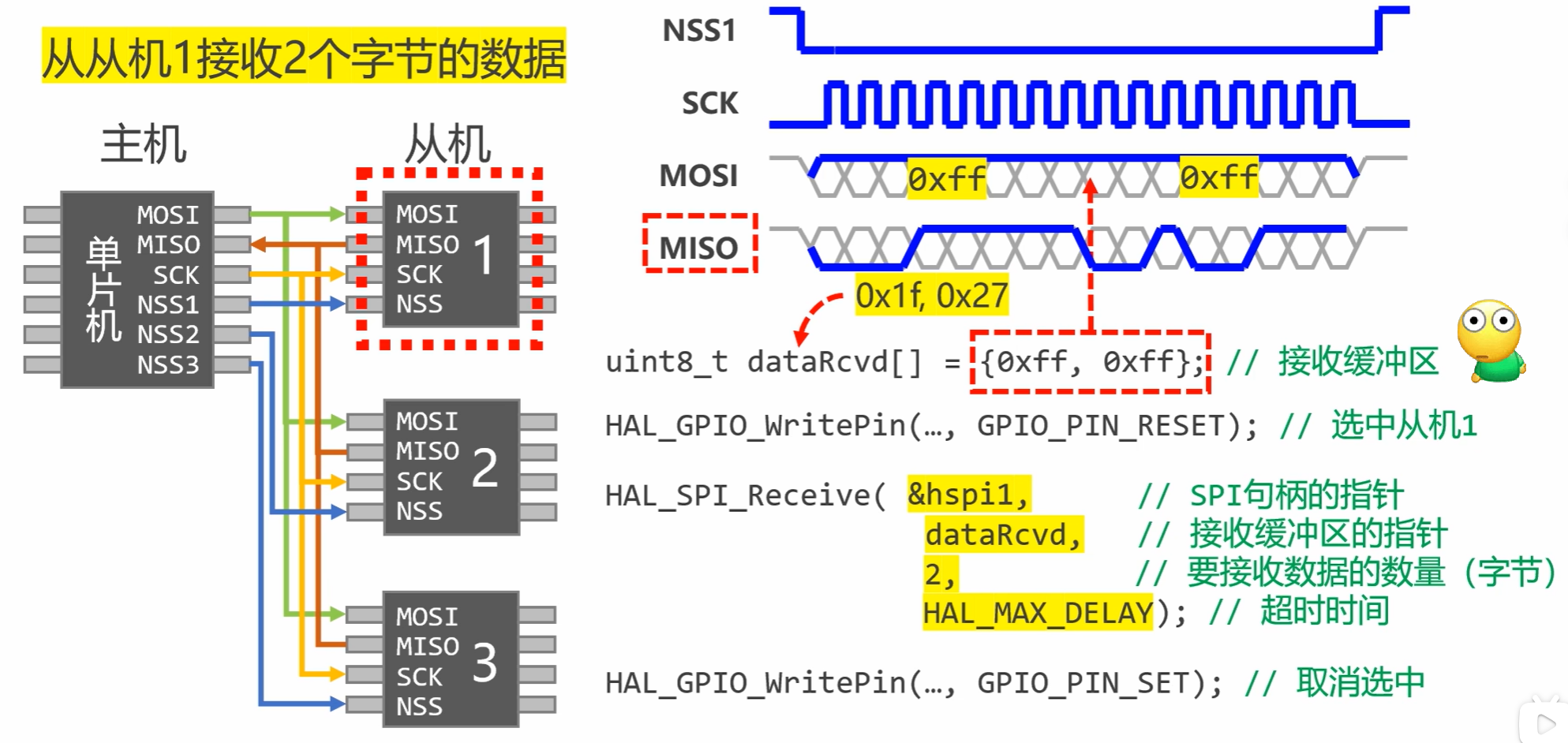

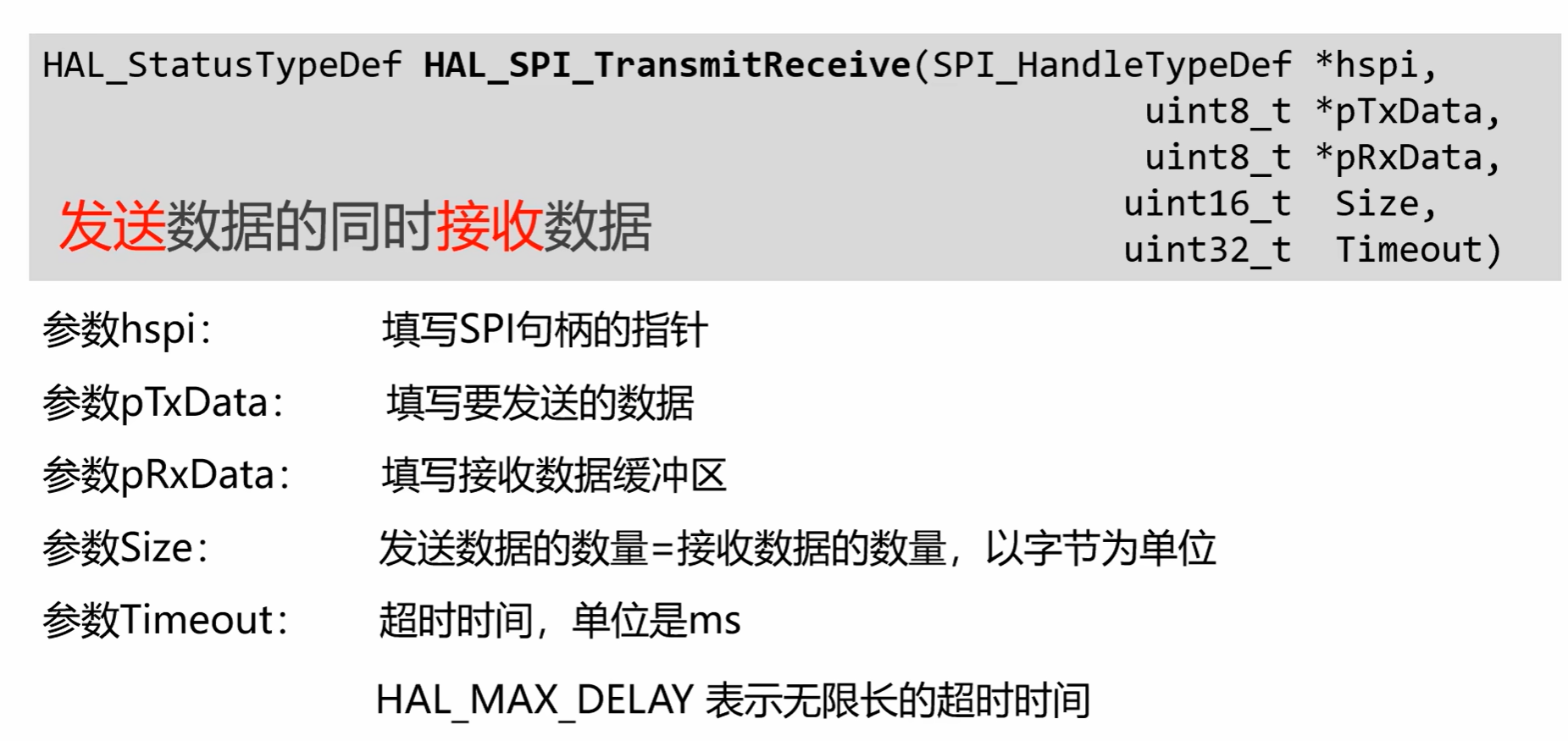

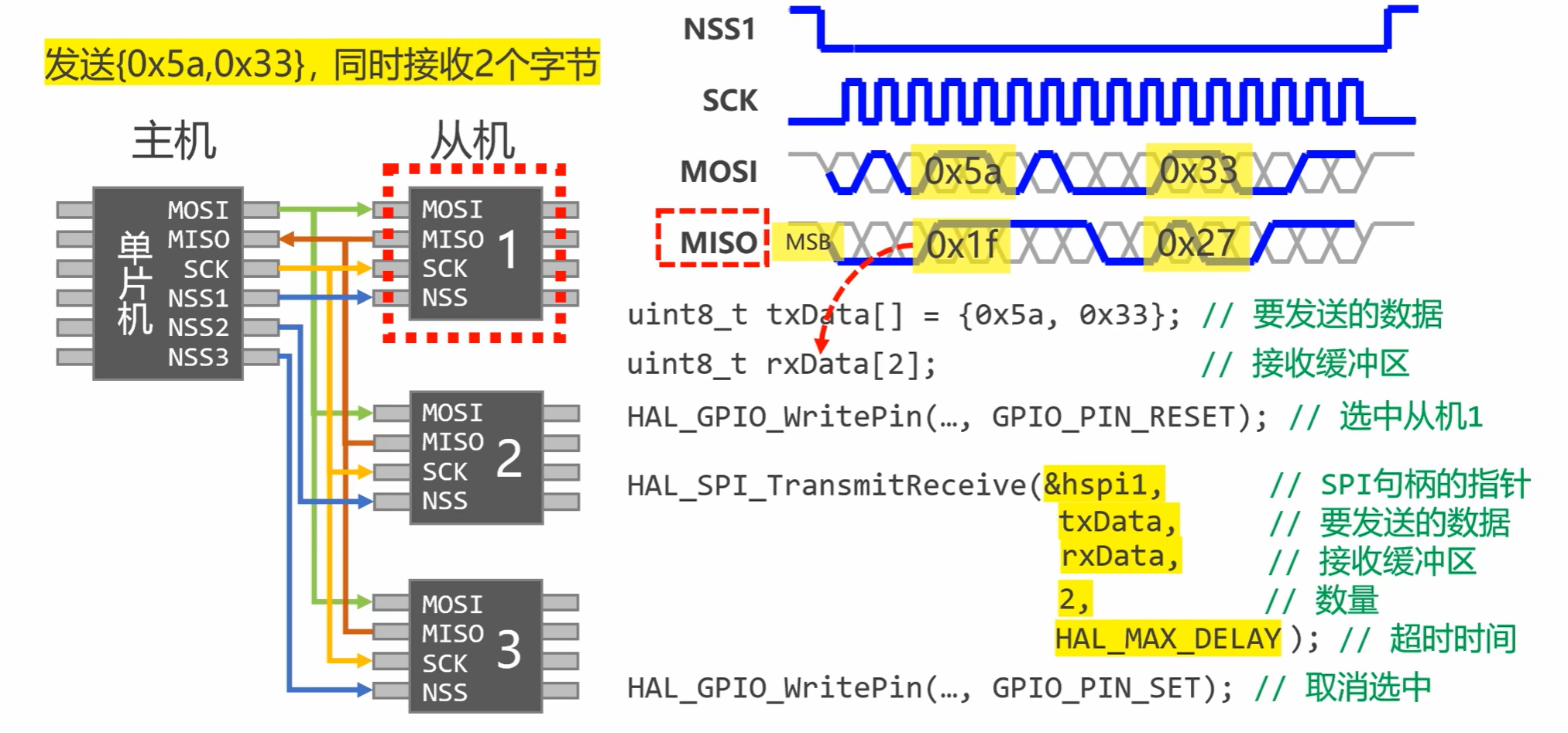

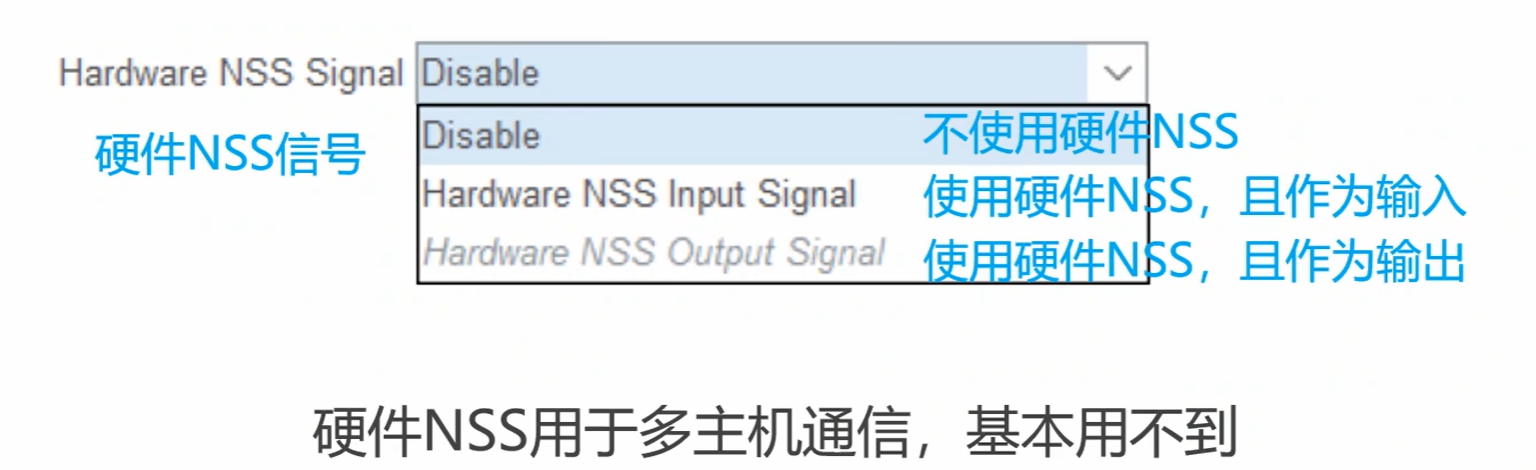

3个编程接口