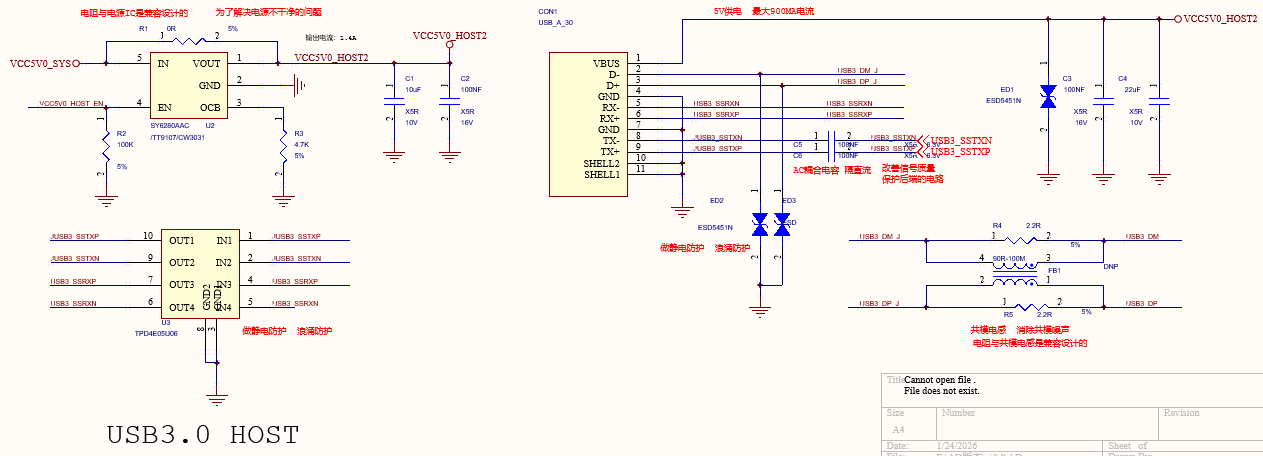

USB3.0 HOST 接口原理图详细解析

这是一个完整的USB3.0 主机(HOST)接口电路,包含电源稳压、ESD 防护、高速信号调理和 USB 母座接口,以下是各模块引脚及电路的作用详

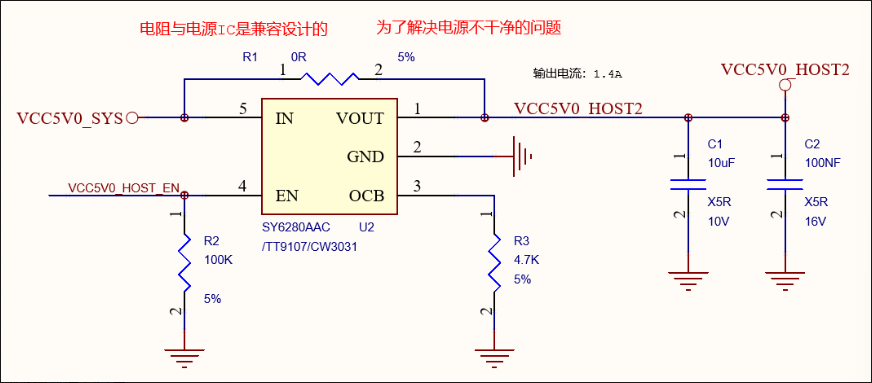

一、SY6280AAC 电源开关电路详细分析

这是一个带使能控制和过流保护的电源路径管理电路,主要为 USB3.0 HOST 接口提供可控的 5V 供电,核心芯片为 SY6280AAC(兼容 TT9107/CW3031),是一款高电流负载开关芯片,以下是各部分的作用解析:

1、核心芯片(SY6280AAC)引脚功能

| 引脚 | 作用与意义 |

|---|---|

IN(5脚) |

电源输入端口,连接系统主 5V 电源(VCC5V0_SYS),为芯片提供输入电能。 |

VOUT(1脚) |

电源输出端口,输出稳定的 5V 电压(VCC5V0_HOST2),最大支持 1.4A 输出电流,为 USB HOST 接口供电。 |

GND(2脚) |

接地引脚,芯片的参考地,提供电流回流路径,同时作为噪声泄放的参考点。 |

EN(4脚) |

使能引脚(高电平有效),通过R2下拉到地,默认处于关断状态 ;当VCC5V0_HOST_EN输入高电平时,芯片导通,输出电源。 |

OCB(3脚) |

过流保护输出引脚(开漏输出),当输出电流超过芯片内部过流阈值时,该引脚会被内部 NMOS 拉低;正常工作时为高阻态,需配合外部电阻(此处为R3)实现电平检测。 |

2、周边元件作用

2.1控制与保护元件

- R1(0Ω 电阻) :

- 作为电流检测点,调试时可串联电流表测量输出电流;

- 也可作为可熔断保险丝(若后续需要限流,可更换为小阻值电阻),当前 0Ω 设计为无额外限流,依赖芯片内部过流保护。

- R2(100KΩ 下拉电阻) :

- 确保

EN引脚在无控制信号时默认低电平,防止芯片误启动,提高电路可靠性。

- 确保

- R3(4.7KΩ 下拉电阻) :

- 配合

OCB开漏输出,正常工作时OCB为高阻态,下拉后引脚输出低电平;过流时OCB内部导通,引脚仍为低电平(注:若需检测过流,建议将R3改为上拉电阻,使正常时为高电平、过流时为低电平,更便于系统检测)。

- 配合

2.2 输出滤波元件

- C1(10uF X5R 电容):低频去耦电容,滤除电源低频纹波,稳定输出电压,减少负载变化导致的电压波动。

- C2(100nF X5R 电容):高频去耦电容,抑制电源高频噪声,降低电磁干扰(EMI),保证高速 USB 设备供电稳定。

3、整体电路工作逻辑

3.1电源通断控制

当主控输出VCC5V0_HOST_EN高电平时,EN引脚为高,芯片内部开关导通,VCC5V0_SYS经芯片输出到VCC5V0_HOST2,为 USB HOST 接口供电;当使能信号为低时,芯片关断,输出无电压。

3.2过流保护机制

若 USB 设备短路或电流过大(超过 1.4A),芯片内部检测到过流,OCB引脚拉低,系统可通过检测该引脚电平触发保护(如关断使能信号),避免电路损坏。

3.3电源稳定性保障

输出端的C1/C2组合滤波电容,有效滤除电源纹波,确保 USB 设备获得干净的供电,减少数据传输时的干扰。

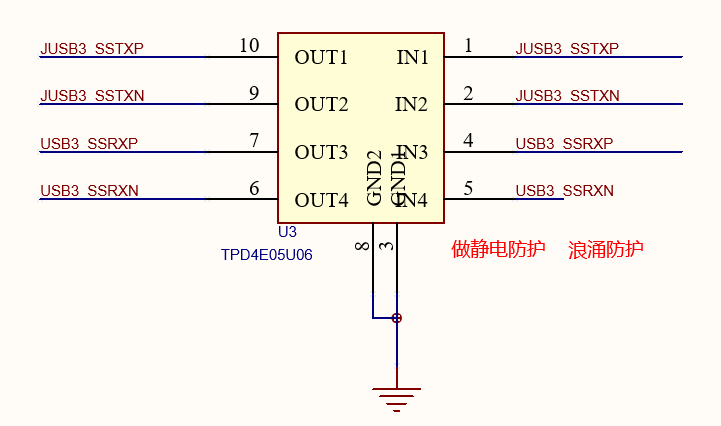

二、 ESD 静电保护模块

(U2:TPD4E004,四通道高速 ESD 保护芯片)

这是一个专为 USB3.0 高速差分信号设计的四通道静电(ESD)与浪涌防护电路,核心芯片 TPD4E05U06 是低电容高速 TVS(瞬态电压抑制器)阵列,用于保护高速接口免受静电和瞬态电压冲击,同时不影响信号完整性。

1、核心芯片(TPD4E05U06)引脚功能

该芯片是双向防护器件,输入输出端可互换,适配 USB3.0 双向高速传输特性:

| 引脚 | 连接信号 | 作用与意义 |

|---|---|---|

IN1(1脚)/OUT1(10脚) |

JUSB3 SSTXP(USB3.0 发送差分对正端) |

防护 USB3.0 高速发送信号的正端,ESD 事件时将瞬态高压泄放到地 |

IN2(2脚)/OUT2(9脚) |

JUSB3 SSTXN(USB3.0 发送差分对负端) |

防护 USB3.0 高速发送信号的负端,与 IN1 组成差分对防护 |

IN3(4脚)/OUT3(7脚) |

USB3 SSRXP(USB3.0 接收差分对正端) |

防护 USB3.0 高速接收信号的正端 |

IN4(5脚)/OUT4(6脚) |

USB3 SSRXN(USB3.0 接收差分对负端) |

防护 USB3.0 高速接收信号的负端,与 IN3 组成差分对防护 |

GND(3/8脚) |

系统地 | 作为 ESD 电流的泄放路径,将静电 / 浪涌能量导入大地,保护后端电路 |

2、电路核心特性

-

**低电容设计(<0.3pF / 通道)**USB3.0 信号速率高达 5Gbps,高电容会导致信号衰减、失真和眼图劣化。TPD4E05U06 的超低电容设计,确保高速信号传输时几乎无损耗,满足 USB3.0 的信号完整性要求。

-

双向防护能力芯片内部的 TVS 二极管是双向导通的,既能防护从接口端(IN)到后端(OUT)的静电,也能防护从后端到接口端的瞬态电压,适配 USB3.0 双向通信的特性。

-

多等级防护性能

- ESD 防护:支持 ±8kV 接触放电、±15kV 空气放电,符合 IEC 61000-4-2 标准;

- 浪涌防护:可抵御 ±200V 的瞬态浪涌电压,保护接口免受插拔、电源波动等带来的冲击。

3、工作原理

当发生 ESD 或浪涌事件时:

- 接口端出现瞬态高压 → 芯片内部的 TVS 二极管快速导通(响应时间 < 1ns);

- 瞬态高压通过 GND 引脚泄放到地 → 后端的 USB 主控 / 母座芯片免受高压击穿;

- 事件结束后,TVS 二极管快速恢复高阻态 → 不影响正常信号传输。

4、电路设计优势

- 极简布局:无需额外外围元件,仅需接地即可实现防护,PCB 布线简洁;

- 高速兼容:低电容设计完美适配 USB3.0、DisplayPort 等高速接口;

- 可靠性高:集成式 TVS 阵列提供多路防护,减少分立元件的布局风险。

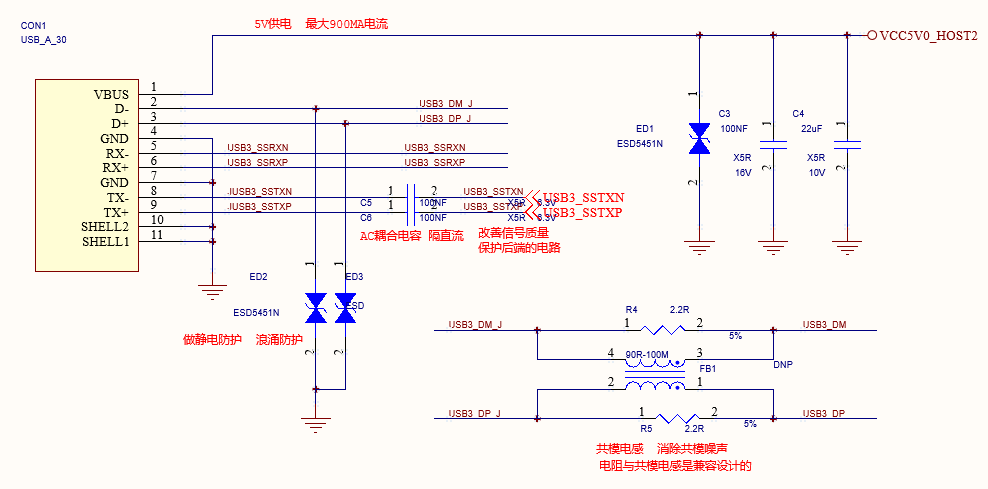

三、 USB3.0 母座(J1:USB3.0 Type-A 母座)

这是一个完整的USB3.0 主机(HOST)接口电路,集成了电源供电、高速信号传输、低速信号兼容、ESD 静电防护和信号调理功能,以下是各模块的作用解析:

1、USB3.0 母座(CON1:Type-A 母座)

作为物理连接接口,负责电源与信号的传输,引脚功能如下:

| 引脚 | 信号名称 | 作用与意义 |

|---|---|---|

1 |

VBUS |

5V 电源输出引脚,为外接 USB 设备供电,USB3.0 协议最大支持 900mA 电流 |

2/3 |

D-/D+ |

USB2.0 差分信号引脚,兼容低速(1.5Mbps)、全速(12Mbps)、高速(480Mbps)设备,同时用于设备枚举与充电检测 |

4/8 |

GND |

接地引脚,电源与信号的参考地,多引脚设计降低接地阻抗,提升抗干扰能力 |

5/6 |

RX-/RX+ |

USB3.0 接收差分对,速率 5Gbps,用于从外接设备接收高速数据 |

7/9 |

TX-/TX+ |

USB3.0 发送差分对,速率 5Gbps,用于向外接设备发送高速数据 |

10/11 |

SHELL |

母座金属外壳引脚,接地实现电磁屏蔽(减少外界干扰)和 ESD 泄放(静电能量导入大地) |

2、电源供电与防护电路

2.1.电源滤波

C3(100nF X5R电容):高频去耦电容,滤除电源高频纹波,抑制电磁干扰(EMI)。C4(22uF X5R电容):低频去耦电容,稳定输出电压,减少负载变化导致的电压波动,为 USB 设备提供干净的供电。

2.2 ESD / 浪涌防护

ED1(ESD5451N双向TVS二极管):并联在VBUS与GND之间,当发生静电或浪涌事件时,快速导通泄放高压,保护后端电源电路免受击穿。

3、USB3.0 高速信号处理电路

3.1 AC 耦合电容(C5/C6,100nF X5R)

- 作用:隔离高速差分信号(

TX/RX)的直流分量,仅允许交流信号传输,符合 USB3.0 协议的 AC 耦合要求(电容值需在 80~120nF 之间),可优化信号眼图质量,减少直流偏移对高速传输的影响。 - 标注说明:图中 "AC 耦合电容 隔直流 改善信号质量 保护后端的电路" 即对应此功能。

3.2ESD 防护(ED2/ED3,ESD5451N)

- 并联在高速差分对与

GND之间,双向 TVS 二极管响应时间 < 1ns,可泄放 ±8kV 接触放电 /±15kV 空气放电的静电能量,同时低电容(<1pF)设计不会影响 5Gbps 高速信号的完整性。

4、USB2.0 低速信号处理电路

4.1共模电感(FB1,45R@100MHz)

- 作用:抑制

D+/D-信号的共模噪声(如电源干扰、电磁辐射),减少 EMI 辐射,同时不影响差分信号的传输,是 USB2.0 接口抗干扰的核心器件。 - 标注说明:图中 "共模电感 消除共模噪声" 即对应此功能。

4.2 匹配电阻(R4/R5,2.2R)

- 串联在

D+/D-信号路径上,优化信号阻抗匹配,减少信号反射,提升 USB2.0 高速(480Mbps)传输时的信号稳定性。 - 标注说明:"电阻与共模电感是兼容设计的" 指电阻与电感的布局和参数匹配,避免相互干扰。

5、整体工作逻辑

- 供电流程 :系统 5V 电源(

VCC5V0_HOST2)经滤波后通过VBUS为外接设备供电,ESD 二极管保护电源免受静电冲击。 - 高速数据传输 :USB3.0 的

TX/RX差分对经 AC 耦合电容隔离直流、ESD 二极管防护静电后,实现 5Gbps 高速数据传输。 - 低速兼容传输 :USB2.0 的

D+/D-经共模电感滤波、匹配电阻优化后,兼容 USB2.0 设备,保证低速 / 高速信号稳定传输。 - 防护机制:外壳接地 + TVS 二极管双重防护静电与浪涌,多 GND 引脚降低接地阻抗,提升接口长期可靠性。

四、 高速信号调理与防护电路

1. USB3.0 高速信号电路

C3/C4(100nF):AC 耦合电容,隔离高速差分信号的直流分量,符合 USB3.0 协议的 AC 耦合要求,保证信号传输完整性。EBD1/EBD2:ESD 保护二极管,为TX/RX差分对和VBUS/GND提供额外的静电防护,泄放瞬态高压到地。

2. USB2.0 信号电路

FL1/FL2(4.7nH):共模电感,抑制 USB2.0D+/D-信号的共模噪声(如电源干扰、电磁辐射),减少 EMI(电磁干扰)。R4/R5(2.2Ω):下拉电阻,在无设备连接时保持D+/D-为低电平,确保主机能正确检测设备插入事件。

3. 电源滤波电路

C5/C6(100nF):接在VCC5V0_HOST2与地之间,进一步滤除电源纹波,保证 USB 设备供电稳定。

五、 整体功能逻辑

- 供电流程 :系统 5V 电源经 LDO 稳压后,通过

VBUS为外接设备供电,LDO 的过流保护可防止设备短路损坏电路。 - 数据传输 :USB3.0 高速数据(

TX/RX)经 ESD 保护和 AC 耦合后传输,USB2.0 信号(D+/D-)经共模电感滤波后兼容低速设备。 - 防护机制:ESD 保护芯片和二极管共同抵御静电冲击,共模电感减少电磁干扰,保障接口长期可靠工作。