一、IMX6ULL时钟树

IMX6ULL的时钟树是一个复杂的系统,负责为处理器内核、外设和接口提供时钟信号。时钟树由多个时钟源、PLL(锁相环)和分频器组成,能够动态调整频率以满足不同场景的功耗和性能需求。

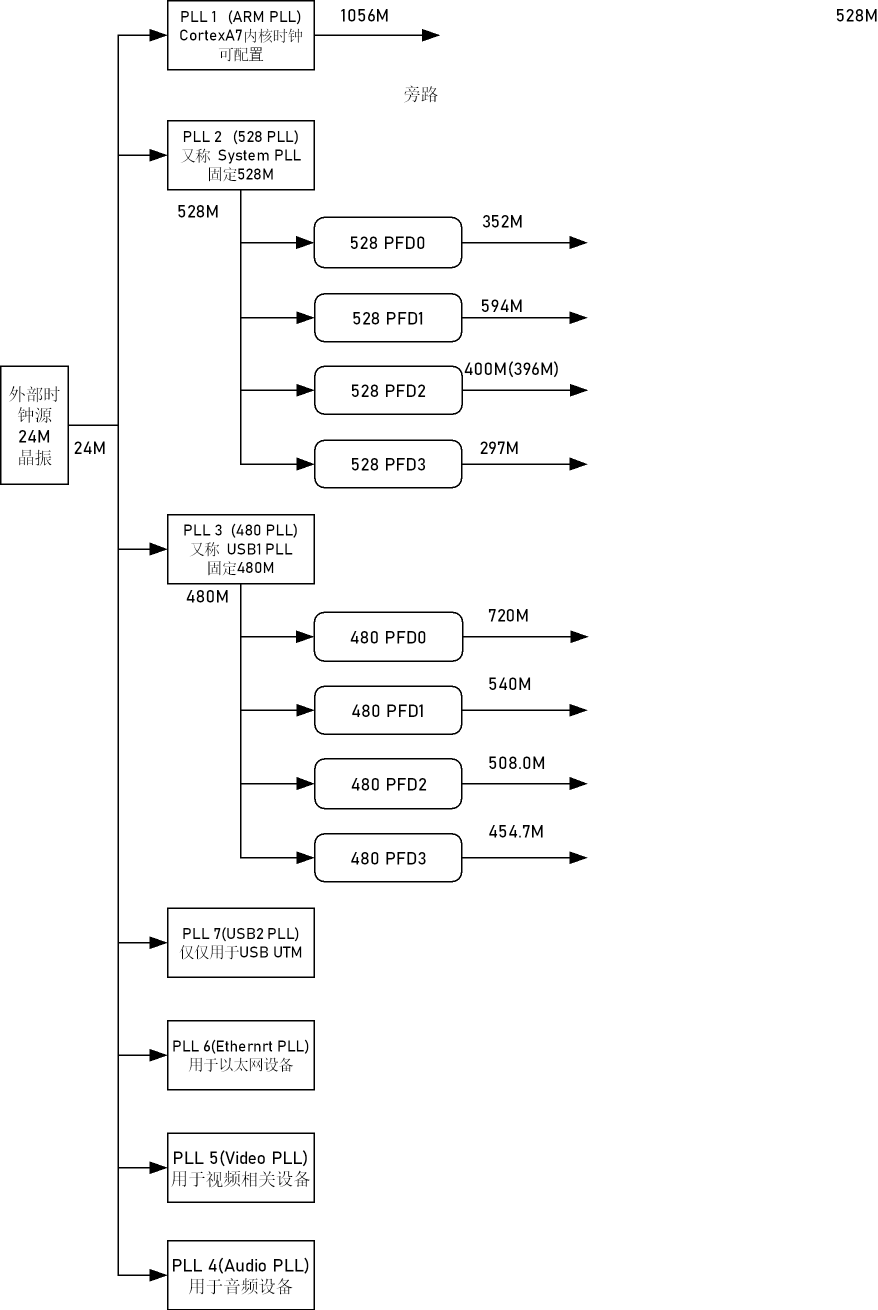

二、时钟源

IMX6ULL支持多种时钟源,包括外部晶体振荡器(24MHz)、内部RC振荡器以及可选的RTC时钟。主时钟源通常通过外部24MHz晶体提供,作为整个时钟树的基础输入。

三、PLL结构

IMX6ULL包含多个PLL模块,每个PLL负责生成特定范围的频率:

- ARM PLL(PLL1):为Cortex-A7内核提供时钟,最高可达1056MHz。

- System PLL(PLL2):生成528MHz基础频率,供总线、DDR等关键子系统使用。

- USB PLL(PLL3):专为USB模块设计,固定输出480MHz。

- Audio PLL(PLL4):支持可编程频率输出,用于音频相关外设。

- Video PLL(PLL5):为显示和图形处理单元提供时钟。

- Ethernrt PLL(PLL6):用于以太网设备

- USB2 PLL(PLL7):仅仅用于USB UTM

四、时钟分频与门控

每个PLL输出的时钟会通过分频器进一步分配到不同模块:

- Cortex-A7内核:通过ARM PLL分频得到,支持动态频率调整(DVFS)。

- AHB/IPG总线:由System PLL分频产生,典型配置为132MHz(AHB)和66MHz(IPG)。

- 外设时钟(如UART、SPI):通过IPG总线时钟分频或门控使能。

五、时钟配置寄存器

时钟树的配置通过以下寄存器组实现:

- CCM(Clock Controller Module):包含PLL使能、分频系数设置等控制位。

- *ANALOG_PLL_系列寄存器:直接配置PLL的倍频参数和输出模式。

关键寄存器示例:

c

// 设置ARM PLL倍频系数(需解锁时序)

CCM_ANALOG->PLL_ARM = (1 << 13) | (82 << 0); // 24MHz * 82 / 2 = 984MHz

CCM->CACRR = 0; // 不分频六、动态频率调整

IMX6ULL支持运行时时钟切换:

- DVFS:根据CPU负载在996MHz/528MHz等预设频率间切换。

- 低功耗模式:在IDLE状态下可关闭部分PLL或切换到低频率RC振荡器。

七、外设时钟使能

每个外设需通过CCM的CCGRx寄存器启用时钟门控:

c

// 启用UART1时钟

CCM->CCGR1 |= CCM_CCGR1_UART1(CCM_CCGR_ON);八、常见问题

- PLL失锁:输入时钟不稳定或倍频系数超出范围会导致PLL无法锁定。

- 时钟抖动:电源噪声或PCB布局不良可能引起时钟信号质量下降。

- 外设无响应:未正确启用CCGR时钟门控是常见原因。