"DRAM 上电时存储单元内容全为 0;Flash 上电时存储单元内容全为 1。"

该陈述是否正确?

2. DRAM 上电默认状态分析

- DRAM 是 volatile memory (易失性存储器),断电后数据丢失。

- 断电时,所有存储单元的电荷因漏电完全耗尽 → 状态归零。

- 因此,上电初始状态必为全 0(未写入前的"空白"状态)。

- 逻辑推导:若断电丢失数据,则上电时无历史残留 → 统一初值(0 或 1),而结构决定为 0。

3. Flash 上电默认状态分析

- Flash 是 non-volatile memory (非易失性存储器),断电后数据保留。

- 上电时内容 = 断电前最后状态,不一定是全 1 或全 0。

- 仅当芯片出厂后经 擦除操作(Erase),或用户显式写入全 1,才呈现全 1。

- 若此前写入

1010,上电仍为1010;若写入全 0,上电即为全 0。 - 原题"Flash 上电全为 1"过于武断,错误

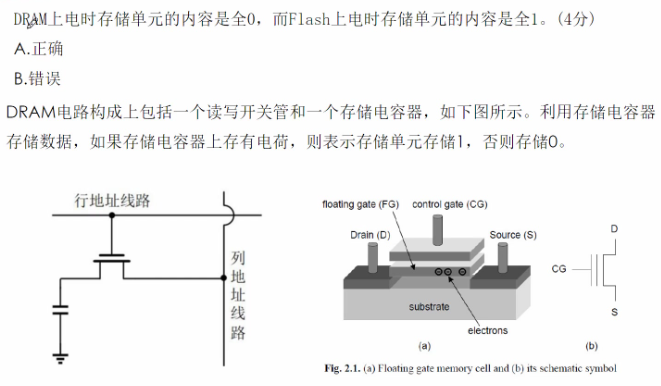

4. DRAM 结构原理详解

- 基本存储单元:1 个 MOS 开关管 + 1 个电容(1T1C 结构)。

- 数据表示 :

- 电容充电(存有电荷)→ 逻辑

1 - 电容放电(无电荷)→ 逻辑

0

- 电容充电(存有电荷)→ 逻辑

- 读写控制:通过字线(Word Line, WL)选通行,位线(Bit Line, BL)充放电。

- 刷新必要性:电容存在漏电,需周期性刷新维持电荷(典型 64ms 刷新周期)。

- 断电后果:WL/BL 无信号 → 电容无充放电回路 → 电荷自然泄漏 → 全 0。

5. Flash 结构原理:Floating Gate 技术

- 核心结构:Floating Gate MOSFET(浮栅 MOS 管)。

- 与普通 MOS 区别:栅极分为两层:

- Control Gate (CG) :外接控制端(可连外部电路,用于充放电)

- Floating Gate (FG) :被二氧化硅绝缘层包围,无电气连接 (浮空,隔离,不给放电)

- 存储原理 :

- 利用 Fowler-Nordheim Tunneling (FN 隧穿效应)或 Hot Carrier Injection(热电子注入)将电子注入 FG。

- FG 存储电子 → 改变沟道阈值电压 Vth → 影响导通状态 → 表示数据。

- 电子在 FG 中无放电路径 → 可保存数年(典型 10 年以上)。

6. Flash 擦除与写入机制

-

擦除(Erase) :

- 对衬底(Substrate)加高压(如 +12V),CG 接地 → 电子从 FG 隧穿至衬底 → FG 放电。

- 擦除后 FG 无电子 → Vth 降低 → 逻辑

1(注:Flash 通常以"擦除态=1"定义)。

-

写入(Program) :

- CG 加高压(如 +10V),衬底接地 → 电子从沟道隧穿至 FG → FG 充电。

- 充电后 Vth升高 → 逻辑

0。

-

关键关系 :

- 擦除 → FG 电子移除 → 逻辑

1 - 写入 → FG 电子注入 → 逻辑

0

注:部分器件采用反向逻辑,但工业标准多为"擦除=1,编程=0"

- 擦除 → FG 电子移除 → 逻辑

7. DRAM 与 Flash 默认状态总结

| 特性 | DRAM | Flash |

|---|---|---|

| 易失性 | Volatile(断电丢失) | Non-volatile(断电保留) |

| 上电默认值 | 恒为 0(电荷耗尽) | 取决于历史操作:<br>• 擦除后 = 全 1<br>• 未擦除 = 断电前状态 |

| 物理机制 | 电容充放电(1T1C) | 浮栅电荷存储(Floating Gate) |

| 刷新需求 | 需定期刷新(防漏电) | 无需刷新 |

| 典型应用 | 主存(如 DDR4/5) | BIOS、固件、嵌入式存储(eMMC, UFS) |