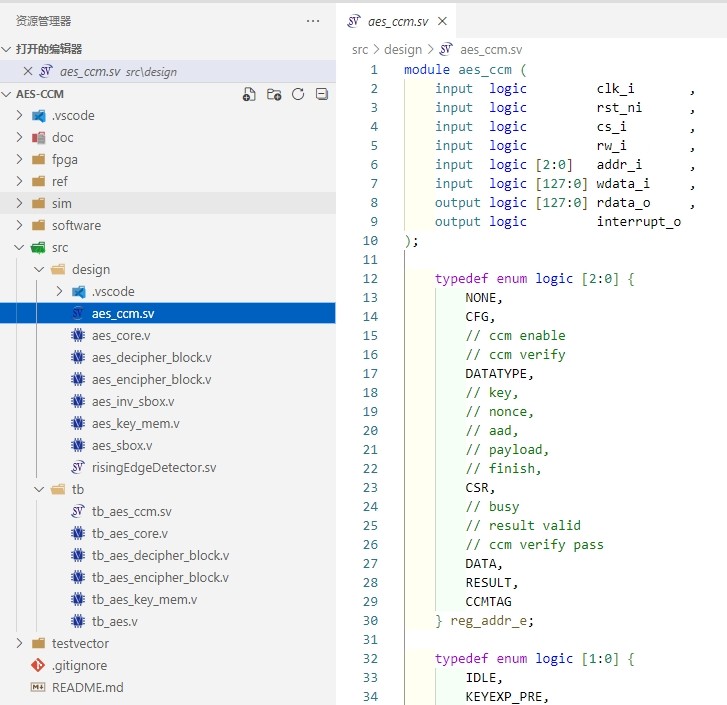

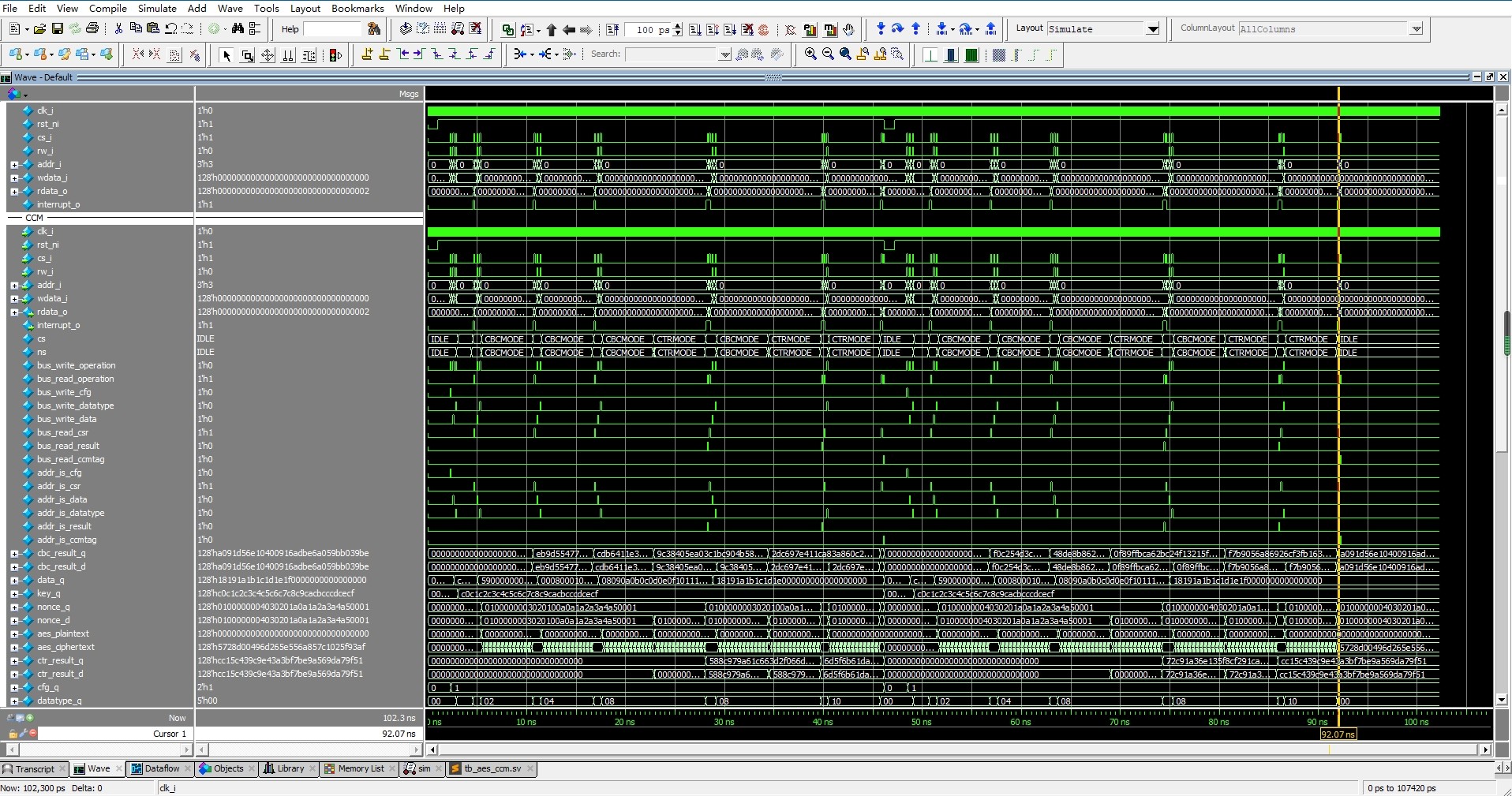

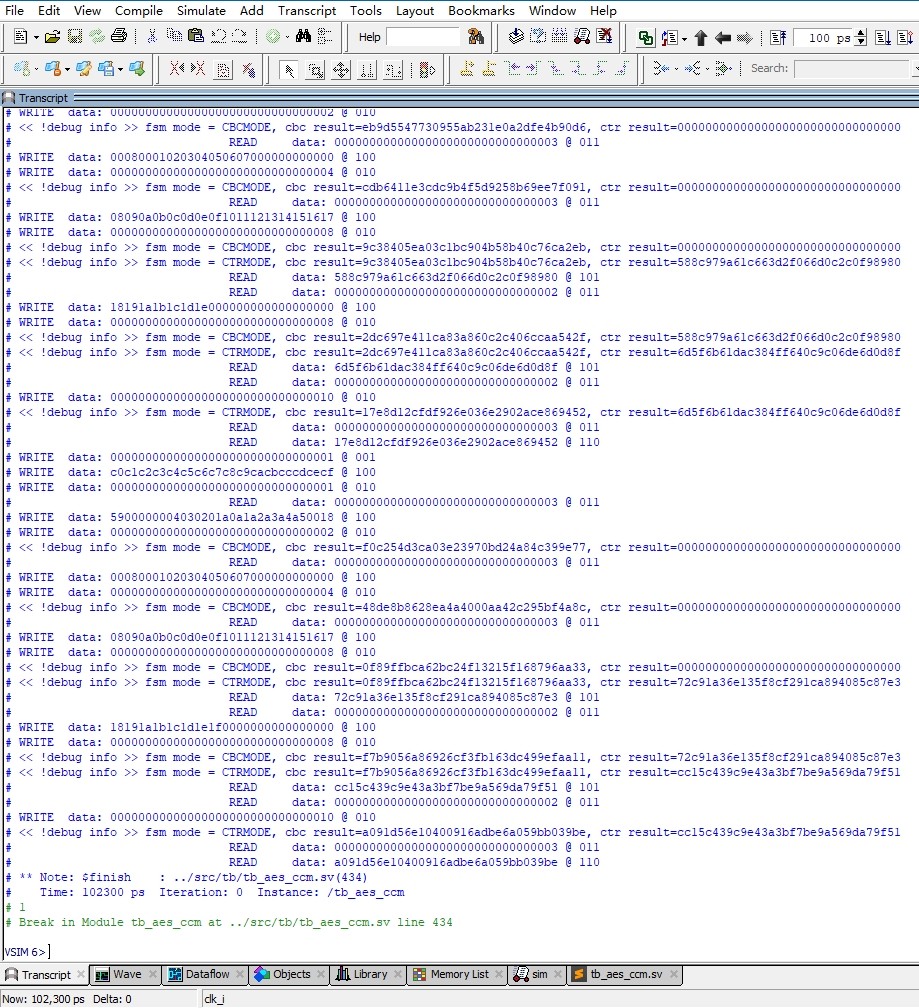

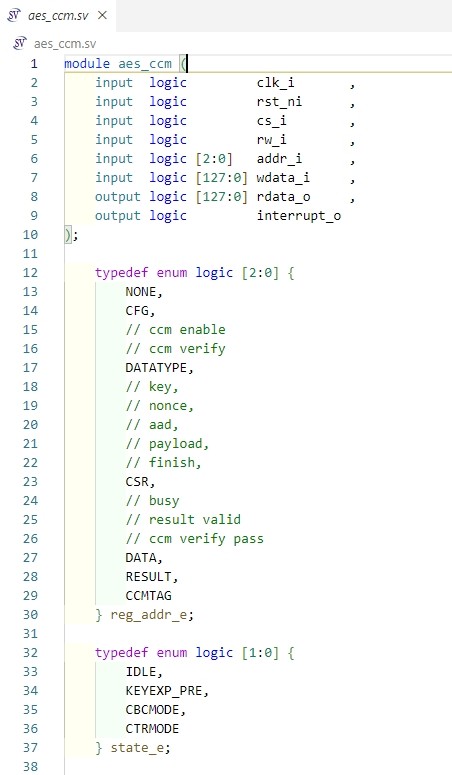

AES CCM算法的Verilog/FPGA实现 一、产品名称 AES CCM算法的FPGA/Verilog实现 二、主要功能 1. AES加密、解密、密钥扩展算法的Verilog实现 2. AES-CCM 128位算法的Verilog实现 3. AES-CCM的嵌入式C语言参考代码 4. AES-CCM算法的测试向量 5. AES-CCM算法自动化仿真测试环境(Modelsim & Makefile) 三、文件夹目录结构 1. src文件夹:设计文件和测试激励(*.v, *.sv) 2. doc文件夹:设计相关的文档 3. sim文件夹:Modelsim仿真环境 4. software文件夹:嵌入式软件C代码 5. testvector文件夹:NIST提供的测试向量 四、设计文件仿真截图 见附图

在数字安全领域,AES(高级加密标准)一直是加密算法的中流砥柱,而AES CCM算法更是在众多应用场景中大放异彩。今天咱就唠唠这AES CCM算法的FPGA/Verilog实现。

主要功能拆解

1. AES加密、解密与密钥扩展的Verilog实现

AES加密和解密是基于一系列复杂的轮变换操作。咱先看看密钥扩展的Verilog代码片段:

verilog

module key_expansion (

input wire [127:0] key,

output reg [127:0] w[0:10]

);

always @(*) begin

w[0] = key;

for (int i = 1; i < 11; i = i + 1) begin

if (i % 4 == 0) begin

// 轮常量异或等操作

w[i] = w[i - 1] ^ {w[i - 4][111:0], w[i - 4][127:112]} ^ {8'h01 << (i / 4 - 1), 56'h0};

end else begin

w[i] = w[i - 1] ^ w[i - 4];

end

end

end

endmodule这里通过不断地对输入密钥进行异或等操作,生成不同轮次所需要的子密钥。每一轮的子密钥生成逻辑都紧密关联,是整个AES加密解密过程的关键基础。

2. AES - CCM 128位算法的Verilog实现

AES - CCM在传统AES基础上增加了认证功能。以认证码计算部分为例:

verilog

module ccm_auth (

input wire [127:0] block,

input wire [127:0] key,

output reg [127:0] auth_tag

);

reg [127:0] state;

// 初始化状态

always @(*) begin

state = block;

for (int i = 0; i < 10; i = i + 1) begin

// 与子密钥异或

state = state ^ key;

// 执行AES轮变换操作(类似加密轮操作)

// 这里省略具体轮变换代码实现

end

auth_tag = state;

end

endmodule此模块通过对数据块和密钥进行多次操作,生成认证标签,确保数据在传输过程中的完整性。

3. AES - CCM的嵌入式C语言参考代码

虽然咱主要讲FPGA/Verilog,但嵌入式C语言代码也是很好的参考。下面是简单的加密函数片段:

c

void aes_ccm_encrypt(unsigned char *plaintext, unsigned char *key, unsigned char *iv, unsigned char *ciphertext) {

// 初始化相关参数

// 调用AES加密函数对明文进行加密

aes_encrypt(plaintext, key, ciphertext);

// 进行CCM模式相关的额外操作,如计算认证码等

// 这里省略具体代码

}这段C代码展示了如何调用AES加密函数,并结合CCM模式的特点来对明文进行加密处理。

4. AES - CCM算法的测试向量

测试向量是验证算法正确性的关键。从NIST提供的测试向量中,我们可以获取一系列已知的明文、密钥、密文组合。比如在testvector文件夹下,可能有这样的文件格式:

text

plaintext: 00112233445566778899aabbccddeeff

key: 000102030405060708090a0b0c0d0e0f

ciphertext: 69c4e0d86a7b0430d8cdb78070b4c55a通过将我们实现的算法在这些测试向量上运行,对比结果是否一致,就能判断算法是否正确实现。

5. AES - CCM算法自动化仿真测试环境(Modelsim & Makefile)

在sim文件夹下,我们搭建了Modelsim仿真环境。Makefile是自动化的关键,下面是一个简单的Makefile示例:

makefile

SIMULATION := modelsim -c -do "run -all; quit"

all:

$(SIMULATION)

clean:

rm -rf transcript vsim.wlf *.log这里通过Makefile的规则,定义了仿真命令。只需要在命令行输入make,就可以自动运行Modelsim进行仿真,make clean则可以清理仿真产生的中间文件,让工作环境保持整洁。

文件夹目录结构探秘

1. src文件夹

这个文件夹可是重中之重,存放着设计文件和测试激励。.v**和 .sv文件里,既有像上面展示的加密、解密、密钥扩展模块,也有用于测试这些模块功能的测试激励文件。测试激励文件通过给各个模块输入特定信号,观察输出结果是否符合预期,从而验证模块功能。

2. doc文件夹

设计相关的文档都在这儿。从算法原理介绍,到模块架构设计说明,应有尽有。它就像是一本指南,无论是对刚接触这个项目的新人,还是对想要深入了解设计细节的老手,都非常有帮助。

3. sim文件夹

Modelsim仿真环境就在这。里面有各种仿真设置文件,还有前面提到的Makefile。在这里,我们可以对设计文件进行功能仿真、时序仿真等,确保设计在硬件实现前功能和时序都正确。

4. software文件夹

嵌入式软件C代码安放在此。这些代码可以和FPGA实现的AES CCM算法相互配合,在实际应用场景中,比如物联网设备,一边是FPGA负责高速数据加密处理,一边是嵌入式软件负责系统管理和与外部交互。

5. testvector文件夹

存放着NIST提供的测试向量,这些测试向量就是验证算法的"金标准",前面也提到,通过它们来验证我们实现的算法是否正确。

设计文件仿真截图

见附图(这里虽然没实际展示截图,但在实际博文中,附上关键模块仿真波形截图,能更直观地展示信号变化和模块功能)。

AES CCM算法的Verilog/FPGA实现 一、产品名称 AES CCM算法的FPGA/Verilog实现 二、主要功能 1. AES加密、解密、密钥扩展算法的Verilog实现 2. AES-CCM 128位算法的Verilog实现 3. AES-CCM的嵌入式C语言参考代码 4. AES-CCM算法的测试向量 5. AES-CCM算法自动化仿真测试环境(Modelsim & Makefile) 三、文件夹目录结构 1. src文件夹:设计文件和测试激励(*.v, *.sv) 2. doc文件夹:设计相关的文档 3. sim文件夹:Modelsim仿真环境 4. software文件夹:嵌入式软件C代码 5. testvector文件夹:NIST提供的测试向量 四、设计文件仿真截图 见附图

AES CCM算法的FPGA/Verilog实现,从功能实现到测试验证,每一步都充满挑战与乐趣。通过合理的目录结构管理和各种工具的配合,我们能够高效地完成这个复杂算法的硬件实现,为数字安全领域贡献一份力量。