目录

[1. 概述](#1. 概述)

[2. Innovus 中的 TSV / Bump / 背面金属建模](#2. Innovus 中的 TSV / Bump / 背面金属建模)

[3. 硬宏中的禁止区域定义](#3. 硬宏中的禁止区域定义)

[4. 禁止区域违规检查](#4. 禁止区域违规检查)

[5. Innovus 中的 3D IC 流程](#5. Innovus 中的 3D IC 流程)

[6. 设计导入](#6. 设计导入)

[7. 堆叠式 IC Verilog 输入](#7. 堆叠式 IC Verilog 输入)

[8. 堆叠配置输入](#8. 堆叠配置输入)

[9. 电源连接输入](#9. 电源连接输入)

[10. 芯片间接口同步与信息交换](#10. 芯片间接口同步与信息交换)

[11. TSV 与bump操作](#11. TSV 与bump操作)

[11.1 TSV / bump生成](#11.1 TSV / bump生成)

[12. 通孔(Feedthru)处理](#12. 通孔(Feedthru)处理)

[13. TSV 与bump布线](#13. TSV 与bump布线)

[13.1 TSV 到 IO 焊盘 / bump / 电源接地条纹的布线](#13.1 TSV 到 IO 焊盘 / bump / 电源接地条纹的布线)

[13.2 bump到bump的布线](#13.2 bump到bump的布线)

[14. 跨芯片连通性验证](#14. 跨芯片连通性验证)

[15. 导出文件](#15. 导出文件)

[用于 RC 提取和导轨分析](#用于 RC 提取和导轨分析)

1. 概述

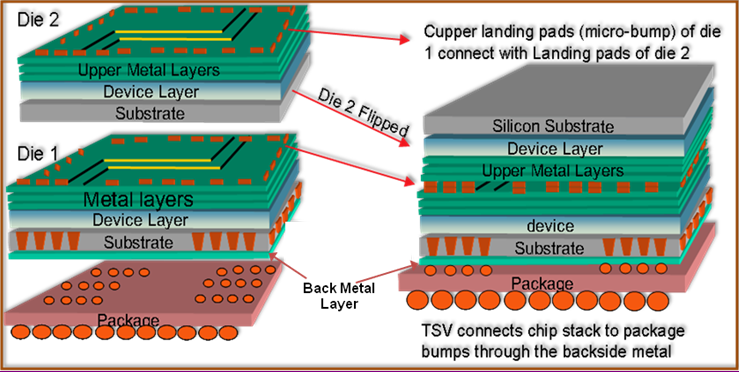

3D IC 系统通常包含多个以三维方式连接的芯片(Die)。在传统 IC 中,输入输出(IO)引脚通过芯片一侧的凸点(Bump)或焊盘实现。为实现 3D 互连,芯片上需额外创建几个组件:

- 在芯片背面形成若干再分布层(RDL),使Bump可分布在芯片的正面和背面。

- 在正面金属层与背面再分布层之间的硅衬底上制造硅通孔(TSV)。

- 当芯片堆叠时,芯片间对齐的Bump构成了芯片间的数据传输路径。

图 1 3D IC 剖面示意图

图 1 3D IC 剖面示意图

Innovus 支持 TSV 设计。在 Innovus 中,3D IC 的所有芯片被划分为多个层级(Tier)。每个层级包含若干芯片,且每个芯片可相对于封装进行翻转、旋转和偏移。通过 Innovus,设计人员能够:

- 指定多芯片系统配置(芯片间的互连关系、各芯片的相对位置)。

- 操作 TSV 和Bump。

- 进行协同设计。

- 同步所有芯片间的接口。

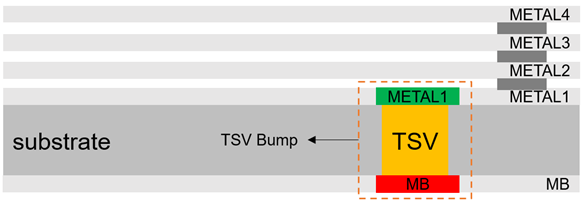

2. Innovus 中的 TSV / Bump / 背面金属建模

为建立芯片间的 3D 堆叠互连,需引入背面金属(MB)、TSV 和Bump。

-

背面金属(MB):是衬底背面的再分布层。

-

TSV(硅通孔):是穿透硅衬底的金属化通孔。TSV 的顶部覆盖层通常是第一层常规布线层(METAL1),底部覆盖层是背面金属(MB),因此背面金属与第一层金属通过 TSV 连接。

为实现芯片间的连接,会在顶层金属层或背面金属层上放置若干焊球(或焊柱)。这些焊球及其下方的金属焊盘在 Innovus 中被称为Bump**(Bump)** 。芯片间对齐的Bump称为ubump(Micro Bump)或着陆焊盘(Landing Pad) 。跨芯片的信号或电源通过微凸点在相邻芯片间传输。芯片与封装基板之间的Bump称为倒装芯片凸点(Flip Chip Bump)。

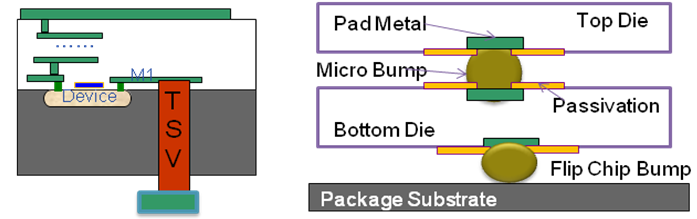

图 2 TSV 与bump横截面示意图

图 2 TSV 与bump横截面示意图

TSV 与bump横截面 背面金属、TSV 和bump的所有物理信息均在 LEF 文件(版本需为 LEF 57 或更高)中定义:

-

背面金属(MB)被建模为常规布线层(ROUTING) ,位于第一层常规金属之前,并为其分配 LEF 属性

BACKSIDE。 -

TSV 被建模为切割层(CUT) ,并分配 LEF 属性

TYPE TSV。

以下是 LEF 文件中用于定义 TSV 和背面金属的附加信息示例:

bump 的焊盘金属信息也在 LEF 文件中描述。bump 被建模为一个单元(Cell),该单元包含一个引脚,其形状和所在层与bump的焊盘金属一致。LEF 文件中不描述焊球的具体信息。

bump的另一种分类方式是基于其所在的金属层:

- 位于顶层金属层的凸点称为正面bump(Front Bump)。

- 位于背面金属层的凸点称为背面bump(Back Bump)。

- 微bump 可以是正面bump 背面bump,具体取决于芯片的堆叠方式。

示例

LEF 文件中描述 TSV 的语句如下:

PROPERTYDEFINITIONS

LAYER LEF58_BACKSIDE STRING ;

LAYER LEF58_TYPE STRING ;

...

END PROPERTYDEFINITIONS

LAYER MB # 背面金属层

TYPE ROUTING ;

PROPERTY LEF58_BACKSIDE "BACKSIDE ; " ;

...

END MB

LAYER TSV # 位于METAL1与MB之间的TSV切割层

TYPE CUT ;

PROPERTY LEF58_TYPE "TYPE TSV ; " ;

SPACING 20.0 LAYER OVERLAP ;

...

END TSV

LAYER METAL1 # 第一层金属

TYPE ROUTING ;

...

END METAL1

...

VIA VIAB1

RESISTANCE 0.01 ;

LAYER MB ;

RECT -11.00 -11.00 11.00 11.00 ;

LAYER TSV ;

RECT -5.00 -5.00 5.00 5.00 ;

LAYER METAL1 ;

RECT -7.0 -7.0 7.0 7.0 ;

END VIAB13. 硬宏中的禁止区域定义

可以在宏内部定义禁止区域约束,以避免bump / 相邻芯片边缘与这些区域发生重叠。如果在禁止区域内创建bump,Innovus 会报告警告,并且该禁止区域信息可传递给相邻芯片。

在硬宏中,可通过在宏的 LEF 文件中创建以下观察层(OBS)来指定阻挡区域:

-

正面钝化层

-

背面钝化层

-

顶层芯片的主切片层

-

底层芯片的主切片层

-

使用 LEF 文件中的钝化层来定义bump的禁止区域。

-

使用 LEF 文件中的主切片层来定义芯片边缘的检查区域。

LEF 文件中用于定义芯片边缘检查和bump禁止区域的语句如下:

# 背面凸点禁止区域层

LAYER BACKPASSIV

TYPE CUT ;

PROPERTY LEF58_TYPE "TYPE PASSIVATION ; " ;

PROPERTY LEF58_BACKSIDE "BACKSIDE ; " ;

END BACKPASSIV

# 正面凸点禁止区域层

LAYER TOPPASSIV

TYPE CUT ;

PROPERTY LEF58_TYPE "TYPE PASSIVATION ; " ;

END TOPPASSIV

# 顶层芯片边缘新层

LAYER TOPDIE

TYPE MASTERSLICE ;

PROPERTY LEF58_TYPE "TYPE ABOVEDIEEDGE ; " ;

END TOPDIE

# 底层芯片边缘新层

LAYER BOTTOMDIE

TYPE MASTERSLICE ;

PROPERTY LEF58_TYPE "TYPE BELOWDIEEDGE ; " ;

END BOTTOMDIE然后,在宏中为这些约束定义 OBS 层。OBS 层定义的示例语法如下:

......

OBS

LAYER TOPDIE

SPACING 10 ;

RECT -10 -20 100.940 70.885 ;

LAYER BOTTOMDIE

SPACING 5 ;

RECT 50 10 580 80.885 ;

LAYER TOPPASSIV

SPACING 20 ;

RECT 200 -10 300 20 ;

LAYER BACKPASSIV ;

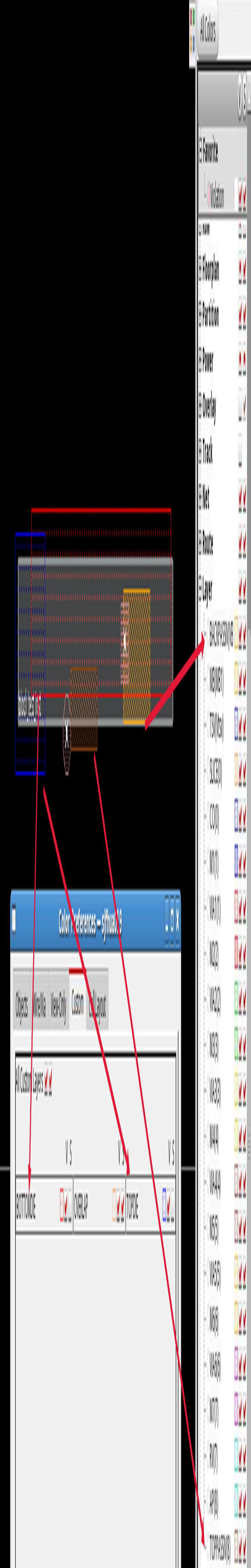

RECT 400 0 500 50 ;要控制 OBS 层的可见性,请执行以下操作:

-

点击 "颜色首选项" 窗口的 "导线 / 通孔" 标签页(选项 - 所有颜色),选择这些层。

-

要控制

BACKPASSIV和TOPPASSIV上 OBS 层的可见性,请点击 "颜色首选项" 窗口的 "层" 标签页,选择这些层。 -

要控制

BOTTOMDIE和TOPDIE上 OBS 层的可见性,请点击 "所有颜色" 按钮,选择 "自定义" 标签页,然后选择这些层。

图 3 OBS 层示例

图 3 OBS 层示例

4. 禁止区域违规检查

使用以下命令检查bump禁止区域违规:

verify_stacked_die -check_type {bump_keepout}该命令用于检查 OBS 层与bump(包括正面和背面bump)之间的重叠情况。

还可以使用以下命令检查相邻芯片间的芯片边缘违规:

verify_stacked_die -check_type {die_edge}一旦在宏内部定义了 OBS 层,相邻芯片的边缘不应与该 OBS 区域重叠。如果宏 OBS 与相邻芯片边缘之间存在违规,该违规将在图形用户界面(GUI)窗口中标记出来。

verify_stacked_die命令必须在执行readDieAbstract命令以导入相邻芯片的芯片摘要文件后使用。该命令会同时检查顶层和底层芯片的边缘违规。

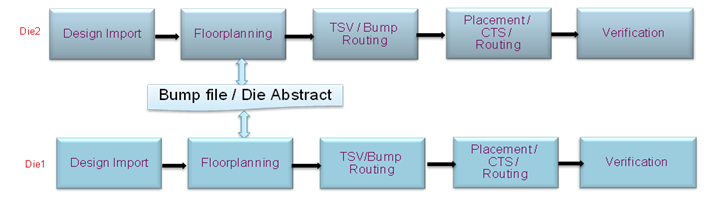

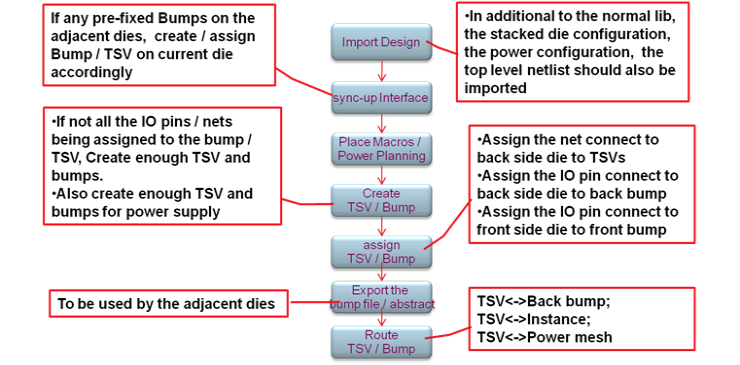

5. Innovus 中的 3D IC 流程

下图展示了 Innovus 中 3D IC 设计的通用流程。该流程图仅包含 2 个芯片,但可扩展至多个芯片。

图 4 Innovus 中的 3D IC 设计流程

图 4 Innovus 中的 3D IC 设计流程

Innovus 采用逐个芯片设计的方式。在设计一个芯片时,会考虑相邻芯片上的微bump及其实例,并对当前芯片上的ubump进行同步和优化。每个芯片的设计流程与常规设计流程非常相似,但需执行以下额外步骤:

-

设计导入阶段:需导入堆叠芯片的额外配置信息。

-

布局规划阶段:确保各芯片间的接口同步,并创建和分配 TSV / bump。

-

布局规划完成后:对 TSV 和bump进行布线。

-

验证阶段:验证芯片间的连通性。

图 5 3D IC 设计中单个芯片的详细布局规划流程

图 5 3D IC 设计中单个芯片的详细布局规划流程

Innovus 提供TSV 工具盒 来执行各种 3D IC 流程任务。它包含 3D IC 流程中使用的表单,包括 TSV / bump操作、数据交换、TSV / bump布线和设计验证。选择tool - TSV可打开该工具盒。

图 6 TSV 工具盒的图形用户界面(GUI)表单

6. 设计导入

Innovus 将传统信息和堆叠芯片的额外信息作为每个芯片设计的输入。

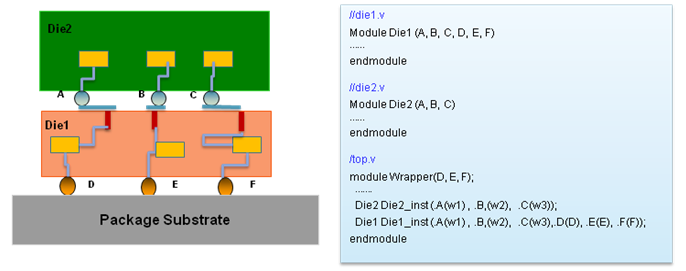

7. 堆叠式 IC Verilog 输入

Innovus 会输入一个额外的顶层网表,用于描述芯片间和芯片与封装间的互连关系。在该顶层网表中,封装被设置为顶层模块;每个芯片被实例化,并描述芯片间的连通性。

图 7 顶层网表示例

需要修改.globals设计文件以导入顶层网表。除了待设计芯片的模块外,顶层网表也应包含在.globals文件中。init_top_cell应设置为待设计芯片的模块名称。

以图 7 为例,在设计配置中,以下设置适用于Die1的设计:

set init_top_cell {Die1}

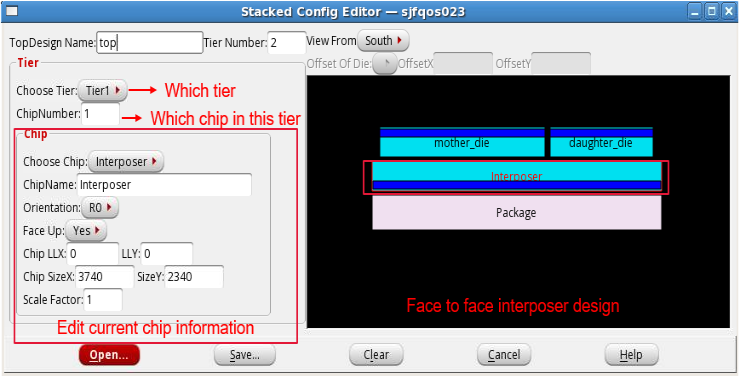

set init_verilog { Die1.v top.v }8. 堆叠配置输入

Innovus 会输入一个 XML 文件,该文件描述了每个芯片相对于封装的位置、翻转方向和朝向。该 XML 文件可通过readTSVConfig命令直接加载,或通过堆叠配置编辑器表单生成和编辑。

<StackChip>

<TopDesign name="top" offsetX=0.0 offsetY=0.0 orientation="R0" />

<Tier number=1>

<Chip name="Interposer" orientation="R0" faceUp="yes" llx=0 lly=0

sizeX=3740 sizeY=2340 scaleFactor=1 />

</Tier>

<Tier number=2>

<Chip name="mother_die" orientation="R0" faceUp="no" llx=100 lly=100

sizeX=2140 sizeY=2140 scaleFactor=0.8 />

<Chip name="daughter_die" orientation="R0" faceUp="no" llx=2300 lly=500

sizeX=1340 sizeY=1340 scaleFactor=1 />

</Tier>

</StackChip>

图 8 堆叠配置文件示例

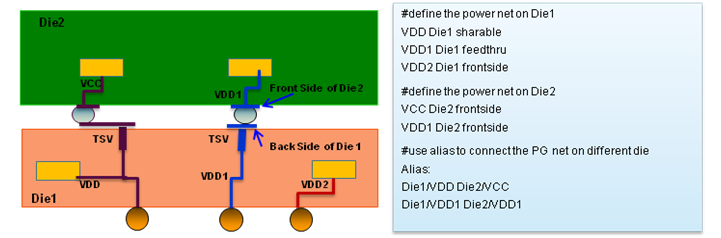

9. 电源连接输入

使用一个文本文件来设置每个芯片上的电源 / 接地(P/G)网络配置。

P/G 网络有四种类型:

-

正面(Frontside):P/G 网络仅连接到正面bump。

-

背面(Backside):P/G 网络仅连接到背面bump。

-

可共享(Sharable):P/G 网络连接到正面和背面bump,以及芯片内的其他实例。

-

通孔(Feedthru):P/G 网络直接连接到正面和背面bump,不连接到当前芯片的任何实例;需使用别名(Alias)在不同芯片上定义相同的 P/G 网络。

图 9 电源配置文件示例

图 9 电源配置文件示例

10. 芯片间接口同步与信息交换

在 3D IC 中,微bump是芯片间的数据 / 电源传输路径。如图 2 所示,微bump的焊盘必须精确对齐,以实现芯片间的连接。

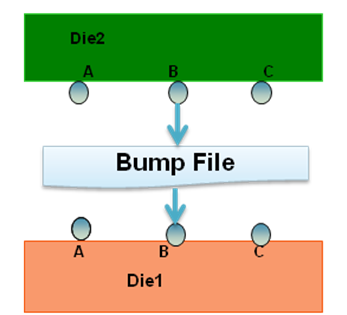

Innovus 通过bump文件在芯片间传输bump信息。bump文件包含了一个芯片的所有bump信息。其流程如下:

-

从一个芯片中通过

writeBumpLocation命令导出bump文件。 -

在相邻芯片上调用

readBumpLocation命令。 -

readBumpLocation命令会根据相邻芯片上的凸点,在当前芯片上创建并分配微凸点。

图 10 接口同步流程

图 10 接口同步流程

bump信息的写入 / 读取过程 可在两个相邻芯片之间迭代进行。如果其中一个芯片上的微bump 发生变化,该芯片的bump信息应被写入并由另一个芯片读取。

在设计一个芯片时,应参考并显示相邻芯片的信息。此步骤并非必需,但有助于跨芯片的优化和手动调试。其流程如下:

-

从一个芯片中通过

writeDieAbstract命令导出芯片摘要文件。 -

在相邻芯片上调用

readDieAbstract命令。 -

readDieAbstract命令会导入相邻芯片的信息,这些信息会在当前设计的芯片中显示并被参考。

11. TSV 与bump操作

Innovus 提供了创建 / 删除和分配 / 取消分配 TSV 和bump的功能。

11.1 TSV / bump生成

在 Innovus 中,有多种方法可创建 TSV / bump:

-

根据相邻芯片的凸点创建 TSV / bump

-

如果相邻芯片上有固定的微bump ,可使用

writeBumpLocation命令导出该芯片的bump文件。 -

然后在当前芯片中,使用

readBumpLocation命令导入该bump 文件,并指定-frontBump、-backBump和--tsvViaName选项,以创建相应的正面凸点、背面凸点和 TSV。

-

-

通过命令在当前芯片上创建 TSV / bump

-

如果相邻芯片上没有固定的微bump ,可运行

addTSV命令,并指定-addTSV、-frontBump和-backBump选项来创建相应的单元。 -

同时,可指定

-lowerLeftLoc、-pitchxy和-upperRightLoc选项来创建期望的 TSV /bump阵列。

-

由于 TSV 和bump 是芯片间的传输路径,应将 TSV 和背面bump放置在与背面连接到相邻芯片的 IO / 模块引脚附近。除非 TSV 必须与核心区域内的模块连接,否则应将其放置在核心区域之外(因为 TSV 会破坏跟随引脚)。

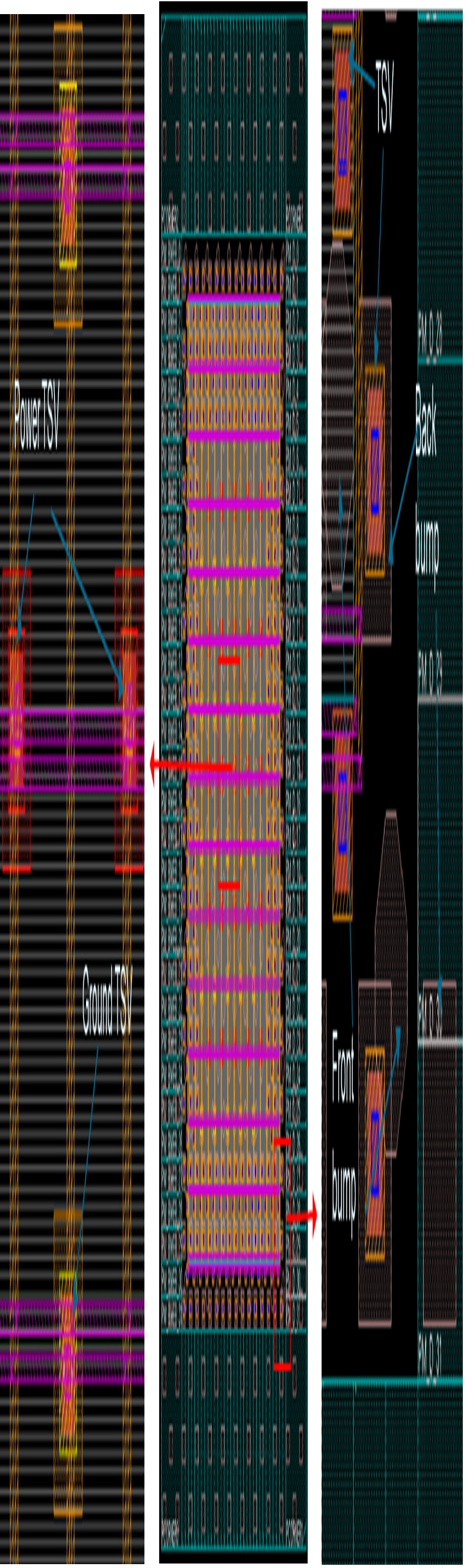

图 11 GUI 中的 TSV / 凸点示意图

图 11 GUI 中的 TSV / 凸点示意图

11.2 TSV / bump分配

创建 TSV / bump后,您可以为信号和电源的 TSV、正面和背面bump进行分配。

-

**根据相邻芯片的凸点分配 TSV /**bump

- 如果相邻芯片上有固定的微bump,

read_bump_locations命令可帮助自动创建和分配凸点。

- 如果相邻芯片上有固定的微bump,

-

**通过命令在当前芯片上创建 TSV /**bump

-

运行

assignTSV命令,将网络分配给 TSV、正面和背面bump,以及 / 或通孔。-

assignTSV -frontBump:帮助将正面bump与 IO 引脚分配。 -

assignTSV -backBump:帮助将背面bump和 TSV 分配。 -

assignTSV -tsvViaName:帮助仅将指定的 TSV 单元分配。

-

-

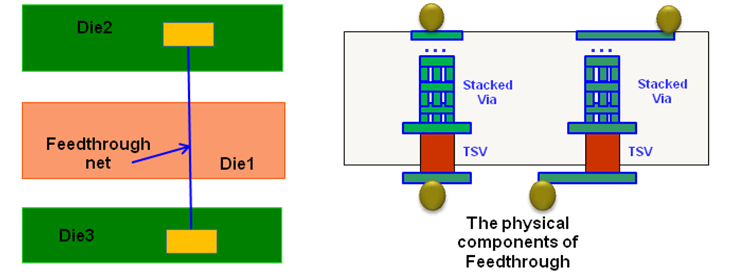

12. 通孔(Feedthru)处理

在 3D IC 设计中,有一种特殊的网络称为通孔网络(Feedthrough Net)。通孔网络仅有两个引脚:一个是正面的 IO 引脚,另一个是背面的 IO 引脚。它不连接到芯片上的任何实例。

通孔网络在一个芯片上的定义,是为了实现正面和背面相邻芯片之间的连接,如图 12 所示。

图 12 通孔的逻辑概念与物理组件

图 12 通孔的逻辑概念与物理组件

可以在 Verilog 网表中定义通孔网络,方法是将正面和背面的两个 IO 引脚一起分配。要创建一个通孔,可在addTSV命令中指定-tsvFeedthru参数。

assignTSV命令可通过开启和关闭-feedthru和-nonFeedthru参数,来同时或单独分配通孔网络和普通网络。assignTSV命令也支持嵌入式 TSV(该 TSV 被建模为背面金属上的一个引脚),但不会将该背面引脚分配给 TSV。

13. TSV 与bump布线

在 3D IC 设计中,用户通常需要将 TSV / bump布线到bump、电源 / 接地条纹、模块引脚和 IO 焊盘。Innovus 提供了多种布线引擎来支持 TSV / bump的布线。

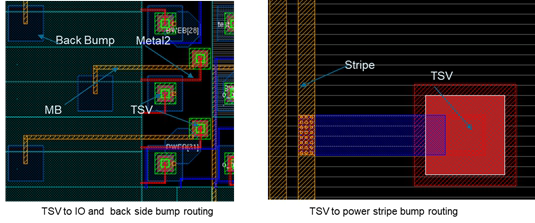

13.1 TSV 到 IO 焊盘 / bump / 电源接地条纹的布线

-

TSV 到 IO 焊盘的布线

-

使用

fcroute命令的aio模式来支持 TSV 到 IO 焊盘的布线。例如:fcroute -type connect_bump_to_pad -designStyle detail -connectTsvToPad -routeWidth 3 -layerChangeTopLayer METAL4 -layerChangeBotLayer METAL1

-

-

TSV 到凸点的布线

-

Innovus 无法同时对正面和背面凸点进行布线,需分开操作。

-

示例:TSV 与背面凸点的布线

-

将顶层和底层布线层均设置为背面层,并定义额外配置

srouteExcludeBumpType。使用以下命令:fcroute -type connect_bump_to_pad -designStyle detail -routeWidth 8 -layerChangeTopLayer MB -layerChangeBotLayer MB -connectTsvToBump -extraConfig ./conf/backside.extraConf -

在

backside.extraConf文件中,需要定义"srouteExcludeBumpType FRONT_BUMP",其中"FRONT_BUMP"是正面凸点的单元名称。

-

-

示例:TSV 与正面 bump的布线

-

将顶层和底层布线层均设置为正面层,并定义额外配置

srouteExcludeBumpType。使用以下命令:fcroute -type connect_bump_to_pad -designStyle -routeWidth 8 -layerChangeTopLayer METAL4 -layerChangeBotLayer METAL1 -connectTsvToBump -extra_config ./conf/frontside.extraConf -

在

frontside.extraConf文件中,需要定义"srouteExcludeBumpType BACK_BUMP",其中"BACK_BUMP"是背面bump的单元名称。

-

-

-

TSV 到电源 / 接地条纹的布线

-

使用

fcroute命令的-connectTsvToRingStripe类型来对 TSV 和电源 / 接地条纹进行布线。例如:fcroute -type power -connectTsvToRingStripe -routeWidth 6 -layerChangeTopLayer METAL2 -layerChangeBotLayer METAL1

-

嵌入式 TSV 被建模为背面金属上的一个引脚,fcroute命令支持该引脚,并会对其进行参考。

图 13 TSV / 凸点布线示意图

图 13 TSV / 凸点布线示意图

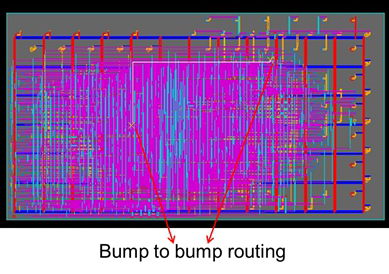

13.2 bump到bump的布线

-

正面 bump到正面 bump的布线

-

中介层(Interposer)设计中没有实例,需要将正面凸点直接连接。您可以使用 NanoRoute 来对其进行布线。使用以下设置和命令:

setNanoRouteMode -routeSelectedNetOnly setNanoRouteMode -routeConnectToBump routeDesign -

图 14 凸点到凸点的布线示意图

图 14 凸点到凸点的布线示意图

-

-

正面bump到正面bump总线的布线

- 在连接 HBM 芯片和 SoC 芯片的中介层设计中,通常需要进行总线布线,以确保 HBM 芯片和 SoC 芯片之间的信号传输性能。本节阐述了中介层设计中总线布线的方法。

布线步骤:

-

创建非默认规则(NDR)和总线布线约束a. 以下命令定义了将在总线布线中使用的 NDR(在 METAL2 和 METAL4 层上,线宽为 2 微米,间距为 3 微米):

add_ndr -width {METAL2 2.0 METAL4 2.0} -spacing {METAL2 3 METAL2 3} -name bus_ndrb. 以下命令定义了将在布线中使用的总线网络约束。它要求工具仅使用 METAL2 作为总线布线层,并使用

bus_ndr作为布线规则。当连接到bump引脚时,工具可能会切换最后几节导线的层。setIntegRouteConstraint -type bus -topLayer METAL2 -bottomLayer METAL2 -rule bus_ndr -net {bus_net_1 bus_net_2 ...} -

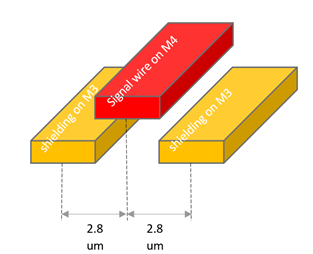

设置层间屏蔽约束 在某些情况下,用户可能希望在信号布线层之间创建屏蔽线,这被称为层间屏蔽 。a. 层间屏蔽偏移以下示例定义了 METAL1 和 METAL3 层上,信号导线中心线与层间屏蔽导线中心线之间的偏移量(2.8 微米)。

setNanoRouteMode -interposerInterlayerShieldingOffsets {METAL1 2.8 METAL3 2.8}b. 层间屏蔽宽度以下示例定义了 METAL1 和 METAL3 层上,层间屏蔽导线的布线宽度(2 微米)。

setNanoRouteMode -interposerInterlayerShieldingWidths {METAL1 2.0 METAL3 2.0}c. 层间屏蔽层以下示例定义了层间屏蔽导线分别在 M2 和 M4 层的下方布线。

setNanoRouteMode -interposerInterlayerShieldingLayers {METAL2 bottom METAL4 bottom}d. 层间屏蔽网络名称以下示例定义了在 METAL1 至 METAL4 层范围内的屏蔽网络名称为 VSS。

setNanoRouteMode -interposerInterlayerShieldingNets {METAL1:METAL4 VSS} -

设置同层交错屏蔽约束 在某些情况下,用户可能希望在同层的信号布线之间创建屏蔽线,这被称为交错屏蔽 。a.

setFlipChipMode -constraintFile fc_shield.constb.fc_shield.const文件内容:以下示例定义了屏蔽宽度为 1.0 微米,屏蔽与信号的间距为 2.0 微米,屏蔽网络为 VSS。SHIELDWIDTH 1.0 SHIELDGAP 2.0 SHIELDSTYLE c SHIELDNET VSS -

在电源 / 接地bump上方创建电源 / 接地条纹

-

对受约束的总线网络和屏蔽进行布线

routeDesign -bump

图 15 屏蔽图案示意图

图 15 屏蔽图案示意图 -

正面凸点到 TSV - bump 通孔网络的布线 在某些情况下,TSV 通孔和背面bump 会被封装在一起,形成一个新的bump 单元,称为TSV bump 。TSV bump 通常在正面、TSV 层和背面都有多个几何形状。

fcroute命令支持通过-connectTsvToBump选项和BUMP_AS_PAD约束,实现从正面凸点到 TSV - bump的布线。fcroute -type connect_bump_to_pad -connectTsvToBump -layerChangeTopLayer METAL4 - layerChangeBotLayer METAL1 --constraintFile fc.const -nets "net1 net2 ..."在

flipchip.const文件中,需要定义"BUMP_AS_PAD"约束,其中"TSV_bump_cell_name"是 TSV - bump的单元名称。BUMP_AS_PAD <TSV_bump_cell_names> END BUMP_AS_PAD 图 16 TSV - bump单元示意图

图 16 TSV - bump单元示意图 -

TSV / bump到模块引脚的布线 在 3D 堆叠芯片设计中,有时没有 IO 焊盘。TSV 和正面bump直接连接到模块引脚。Innovus 通过 NanoRoute 支持此功能。使用以下设置和命令:

setNanoRouteMode -routeSelectedNetOnly true setNanoRouteMode -routeConnectToBump true routeDesign

14. 跨芯片连通性验证

verifyConnectivity命令用于检查芯片间的连通性是否正确实现,即相邻芯片上具有相同信号的微bump是否对齐。

要检查单个芯片上的微bump对齐情况,您需要导出所有相邻芯片的芯片摘要文件,然后运行以下命令:

verifyConnectivity -tsv违规将显示在违规浏览器中,并且违规标记将显示在布局窗口中。

readBumpLocation -checkAlignment命令也可用于检查bump对齐情况。

15. 导出文件

设计完成后,Innovus 除了导出 DEF、GDSII 等常规文件外,还可以为 3D IC 设计导出额外文件。这些额外文件用于下游分析工具,如静态时序分析(STA)、提取和导轨分析。

用于静态时序分析(STA)

Innovus 能够创建一个顶层 SPEF 文件,该文件描述了芯片间的连通性。此 SPEF 文件中的 RC 值为 0,但仅写入芯片间的互连信息。该 SPEF 文件与每个芯片的 SPEF 文件一起,是 Tempus 进行静态时序分析的输入。使用以下命令:

createTSVNoLoadSPEF用于 RC 提取和导轨分析

Innovus 能够为 Quantus 和 Voltus 生成微凸点映射文件。该文件描述了相邻芯片之间微凸点的连接关系。

writeMicroBumpMappingFile- 总结