3.4.5 Differential Fault Simulation

Differential fault simulation结合了下面两种方法的优点:

- concurrent fault simulation

- single fault propagation techniques

这个方法是逐个仿真所有faulty circuit,只观测本次仿真的faulty circuit和上次仿真的不同。用event-driven simulator可以很方便的实现这个仿真。

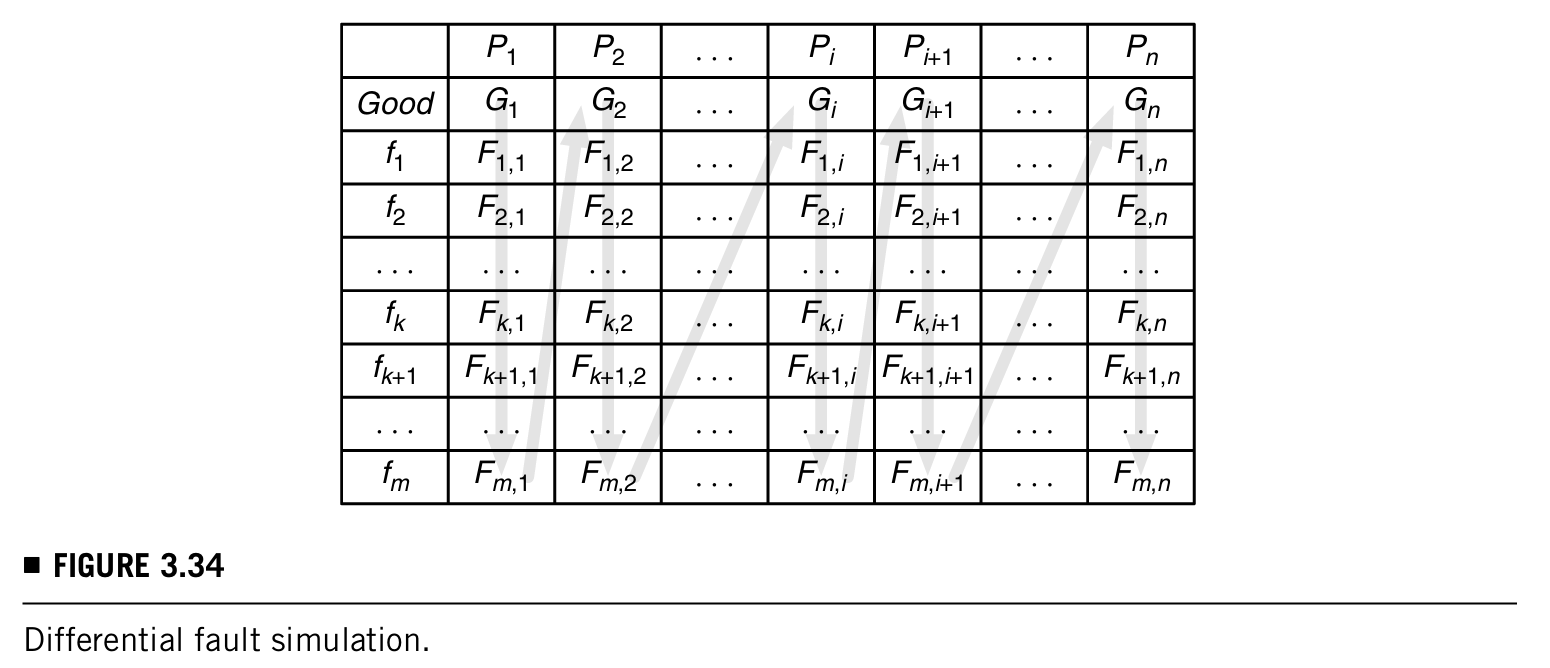

differential fault simulation工作的过程如下图所示(需要时参考原文):

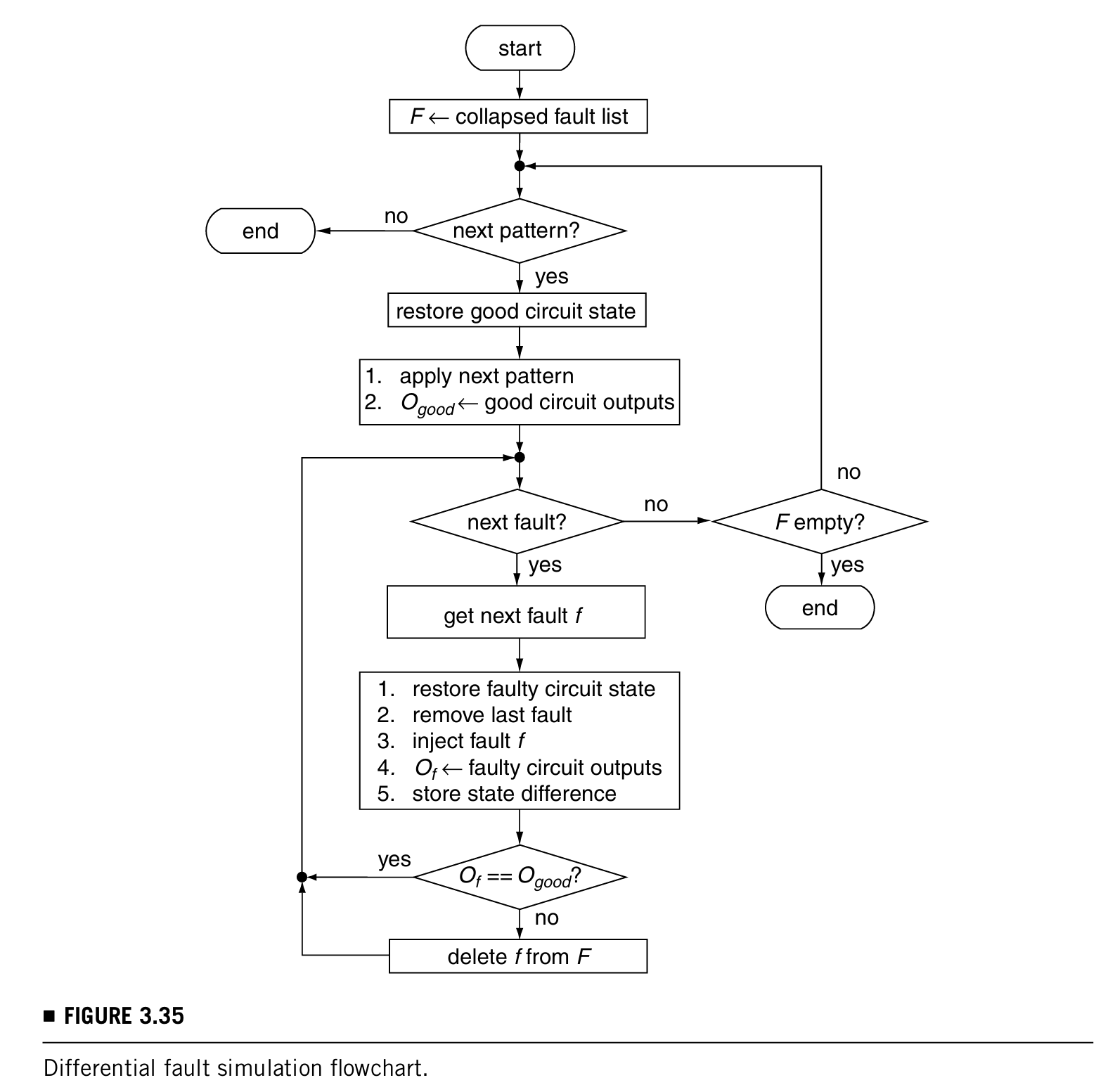

differential fault simulation的仿真流程图如下(和前面几个方法类似):

这个仿真方法的问题是每一个fault的顺序都不一定是它们真实发生的顺序,如果把时序也考虑进去的话,那么这个仿真方法也需要不小的存储空间。

3.4.6 Fault Detection

前面讲的故障仿真的方法都是为了让故障检测更加简单,但是实际上,故障的检测是更加困难的。

比如说有以下两类:

- oscillation faults:指的是输入错误后导致输出处于不确定的状态,意味着故障可能被检测到也可能检测不到,这就增加了故障检测的难度(当然可以多测几组pattern,测到的概率就大了)

- hyperactive faults过度活跃故障:例如时钟发生故障,fault-free电路和faulty电路不一样的地方很多,导致需要花费的时间和存储空间变得很大(但是这种故障是容易被检测到的,所以通常不仿真,防止仿真器爆炸)

3.4.7 Comparison of Fault Simulation Techniques

故障仿真技术需要考虑以下几个因素:

- 速度(major):serial fault simulation<parallel fault simulation< deductive fault simulation<=concurrent fault simulation< Differential fault simulation(快12倍)

- 需要的存储空间(major):serial fault simulation<parallel fault simulation=PPSFP< deductive fault simulation<Concurrent fault simulation>Differential fault simulation

- 多值逻辑仿真的能力multivalued logic simulation capability:Serial fault simulation、concurrent fault simulation、differential fault simulation可以

- delay model仿真的能力delay model simulation capability: serial fault simulation、concurrent fault simulation可以

- 功能模型仿真的能力functional model simulation compatibility:serial fault simulation、concurrent fault simulation、differential fault simulation可以

- 时序故障仿真的能力sequential fault simulation capability:serial fault simulation、parallel fault simulation、concurrent fault simulation、differential fault simulation可以

选择最合适的仿真技术就需要对应考虑:

- 仿真时间限制因素

- 系统的存储空间

- 未知或者高阻的状态

- delay model

- 电路的功能描述(the presence of functional level descriptions)

- 电路的特性(是时序逻辑还是组合逻辑)

最适合用于组合逻辑电路的仿真方法:

- PPSFP

- concurrent fault simulation

最适合用于时序逻辑电路的仿真方法:

- differential fault simulation

- concurrent fault simulation

不同方法应对不同情况,所选用技术算法可以切换。

即便现在的技术都在速度和存储空间上表现很不错,但是仿真还是存在存储空间爆炸和仿真时间长的问题。针对存储空间问题,有multiple-pass fault simulation 方法;针对故障仿真速度问题,有distributed fault simulation方法。

3.4.8 Alternatives to Fault Simulation

fault simulation对于大型电路来说是非常耗时的,所以人们会寻找其他省时的方案代替真正的故障仿真,比如只需要进行一次fault-free的仿真或者进行很少次数的故障仿真。

讨论两种情况:

- fault grading:也就是评价pattern质量的时候,可以用alternatives

- diagnosis:不可以用alternatives,因为诊断需要详细知道用什么pattern探测出了什么故障

下面几节是几种不同的方法。

3.4.8.1 Toggle Coverage(切换覆盖)

切换覆盖是一种很流行的评估测试pattern的方法,因为它只需要一个fault-free仿真。

定义有两种:

- 宽松的定义:net的值被置为0和1

- 严格的定义:net中既包含0到1也包含1到0的转换

3.4.8.2 Fault Sampling

故障采样技术是指只仿真一组抽样出来的fault。真实的故障覆盖率和采样后的故障覆盖率很接近(具体的数学论证方法见原文)。

采样的误差取决于两个因素:

- 采样的样本量

- 采的样是否有偏差

3.4.8.3 Critical Path Tracing(关键路径追踪)

关键路径追踪是,给定一个测试pattern t,net x有一个关键值 v,如果且仅如果x stuck at v'这个故障发生可以被t检测到。

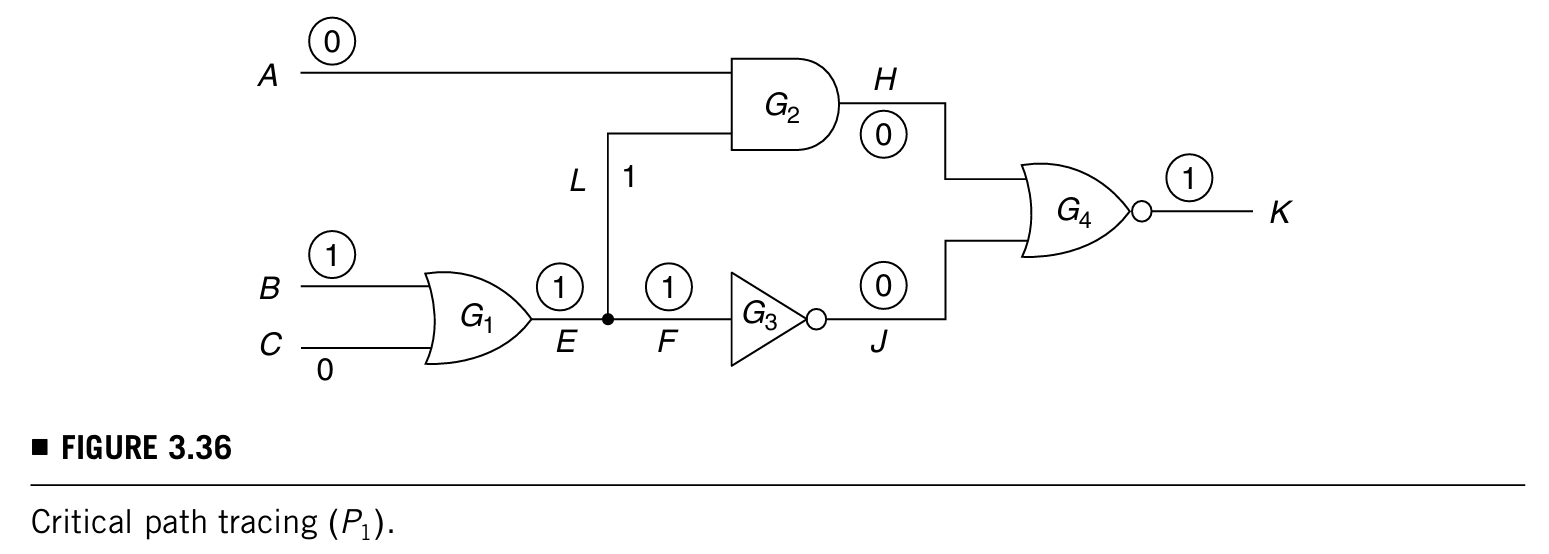

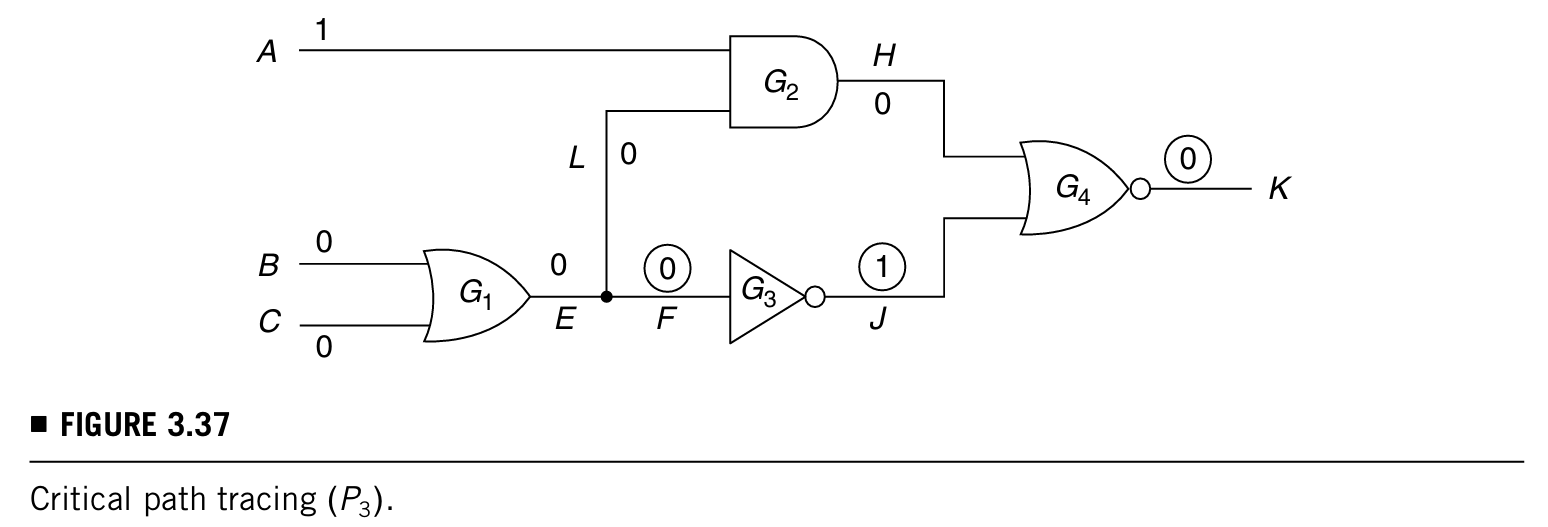

用pattern P1和P3举两个例子。

P1举例,有7个关键net,它们的相关故障是{A/1, H/1, B/0, E/0, F/0, J/1, K/0}

P3举例,有3个关键net,它们的相关故障是{F/1, J/0, K/1}

3.4.8.4 Statistical Fault Analysis(统计故障分析)

statistical fault analysis (STAFAN) :基于概率论

(当拓展阅读吧)

3.5 CONCLUDING REMARKS

商业可用的logic simulators和所属公司如下:

- Cadence:Verilog-XL, NC-Verilog

- Mentor Graphics:ModelSim

- Synopsys:VCS

fault simulators可以是单独的工具也可以是和ATPG中集成的工具:

- 单独用的工具:

- Cadence:Verifault-XL

- SynTest:TurboFault and TurboScan

- ATPG中集成的工具:

- Cadence:Encounter Test

- Mentor Graphics:FastScan

- Synopsys:TetraMAX